SmartDRC/LVS Physical Verification

SmartDRC/LVS performs physical verification of analog, digital and mixed-signal ICs including design rule checks (DRC), layout connectivity extraction and layout vs schematic (LVS) comparisons. Its unique architecture delivers high performance and capacity using multiple CPUs, accurate processing of complex shapes, and exceptional user productivity with fast interactive verification and intuitive debug. SmartDRC/LVS are silicon-proven, and foundry certified for processes at Tower Semiconductor, X-FAB and UMC.

Introduction

Increasingly complex designs together with shrinking process geometries are driving the need for a highly productive physical verification environment. This includes the ability to rapidly setup rule and technology files, an efficient data flow from design entry to verification, and the verification tools’ capacity and performance to process huge hierarchical designs quickly. Users need easy design navigation within the tools, intuitive visualization, rapid debug and resolution of identified errors. Accurate calculation of geometry dependent SPICE parameters is crucial, as is the ability to correctly process complex shapes and all-angle objects.

SmartDRC/LVS has unique capabilities to meet these growing requirements. Exceptional performance is delivered through the use of multi-threaded processing, optimized layer operations, efficient memory management and advanced algorithms.

SmartDRC/LVS is tightly integrated with Silvaco’s Expert layout editor and Gateway schematic editor. The integration enables users to visualize and pinpoint design issues and design rule violations and quickly act to resolve them. SmartLVS extracts the netlist from layout and provides the user the ability to cross-compare the schematic and layout.

Features

DRC/LVS

- DRC (design rule checking)

- LVS (layout versus schematic)

- NVN (netlist versus netlist)

- Innovative One-Shot architecture for near linear scaling and runtime predictability

- Support of antenna rules, density rules, pads, latches, and other special rules

- Any angle support for specific devices

- Run and debug GUI environment (RDE) with interactive violation handling

- Hierarchical error browsing

- Waiver system

- Native error browsing in Expert layout editor

- LVS cross-probing

- Comprehensive reports and summaries

- Clear and powerful programmable rule language

- Integration with Expert and other physical layout editors

- OpenAccess native support

Benefits

- Class-leading performance, matching or exceeding offerings from other vendors

- Scalable performance across large CPU farms and multi-core machines

- Easy navigation and visualization through graphical and text DRC error reports

- Intuitive for new users and experts

- Silicon-proven and foundry certified for processes at Tower Semiconductor, X-FAB and UMC

Applications

- Analog mixed-signal, digital, MEMS, memory, photonics, power management, Flat Panel, radiation hardened, and RF designs

Performance

SmartDRC provides predictable scaling whether running flat or hierarchical, on single or multi-cores. For an existing complex foundry certified rule set at 180nm, SmartDRC, utilizing its One-Shot technology, can process approximately 16M transistors/hour even running flat.

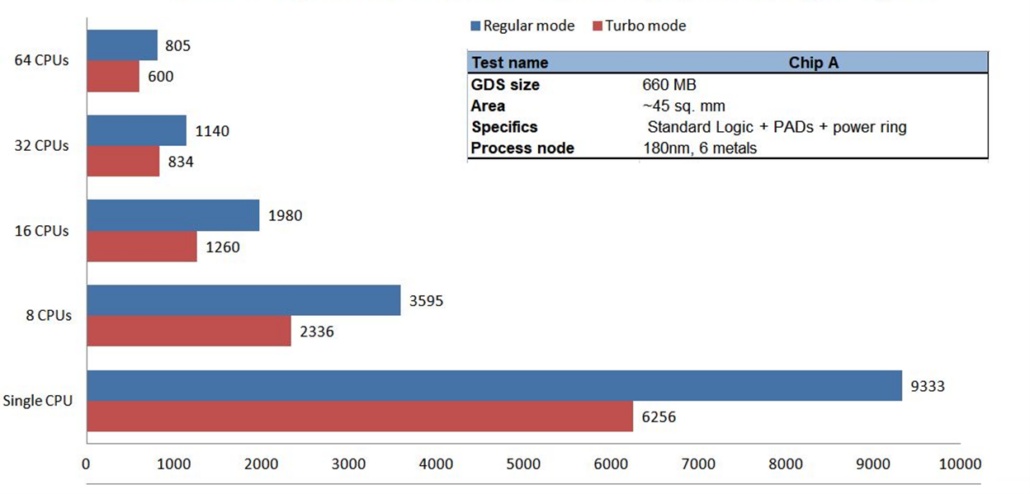

In the figure below, SmartDRC performed DRC analysis of a 180nm design using a foundry-certified rule deck, that included standard logic, PADs, and power rings using six metal layers. The flat GDS layout database was 660 MB in size. Runtimes, in seconds, are shown for different runs that used a growing number of CPUs. Turbo mode is a heuristic algorithm that speeds runtimes for most designs with minimal compromises in accuracy. Compared to a single CPU, performance gains of 10X are seen here with a 64 CPU configuration. Performance gains over 25% are still seen when moving from 32 to 64 CPUs, showing the advantages of SmartDRC/LVS ‘s analysis technology. SmartDRC/LVS runtimes are on par with or superior to established physical verification tools in the market.

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors