SmartDRC/LVS物理検証

SmartDRC/LVSは、アナログ/デジタル/ミックスドシグナルIC向けの DRC(デザイン・ルール・チェック)、ネットリスト抽出、LVS(レイアウト対スケマティック)を行う物理検証ツールです。マルチCPUを利用した独自のアーキテクチャにより、高い性能とキャパシティ、複雑な形状の高精度な処理、高速なインタラクティブ検証と直感的なデバッグ環境を提供するため、生産性の大幅な向上を実現できます。SmartDRC/LVSはシリコン実証済みで、Tower Semiconductor、X-FAB、UMCのプロセスでファウンドリ認証を受けています。

はじめに

デザインが一層複雑となり、プロセス形状のさらなる縮小も続く今日では、生産性向上に大きく貢献する物理検証環境の必要性がますます高まっています。このような環境には、ルール・ファイル/テクノロジ・ファイルを素早く設定できること、デザイン入力から検証までのデータ・フローの効率化を実現できること、および大規模な階層的デザインを短時間で処理できる機能と性能を持つ検証ツールを使用できることが求められます。また、必要なデザイン情報がツール画面にわかりやすく表示されること、データを視覚化により直感的に確認できること、および特定したエラーに対し素早くデバッグを実行して解消できることも必要です。形状依存SPICEパラメータを正確に計算する機能や、複雑な形状と任意の角度のオブジェクトを高精度で処理できる機能も欠かせません。今日の検証環境に求められる要件は、ますます増加しています。

SmartDRC/LVSは、そうした一連の要件を満たす独自のさまざまな機能を備えています。マルチスレッド処理の活用、レイヤ演算の最適化、メモリ管理の効率化、および高度なアルゴリズムの使用により、SmartDRC/LVSは極めて高いパフォーマンスを実現することができます。

SmartDRC/LVSの特長の1つは、Expertレイアウト・エディタ、およびGatewayスケマティック・エディタとの緊密な統合です。この統合により、デザイン上の問題やデザイン・ルール違反をピンポイントで指定して視覚化できるので、それらの解消に向け素早く対応することができます。

特長

DRC/LVS

- DRC(デザイン・ルール・チェック)

- LVS(レイアウト対スケマティック)

- NVN (ネットリスト対ネットリスト)

- 革新的なワンショット・アーキテクチャにより、線形に近いスケーラビリティと実行時間の予測可能性を実現

- アンテナ・ルール、密度ルール、パッド、ラッチ、その他の特殊ルールのサポート

- 任意角度エッジ形状を含んだデバイスのサポート

- インタラクティブなエラー処理が可能なラン&デバッグGUI環境(RDE)

- 階層的なエラー・ブラウジング

- 疑似エラー管理システム

- Expertレイアウト・エディタでのネイティブ・エラー・ブラウジング

- Expert/GatewayとのLVSクロス・プロービング

- 包括的なレポートとサマリ

- 明確かつ強力なプログラム可能ルール言語

- Expertや他のレイアウト・エディタとの統合

- OpenAccessのネイティブ・サポート

利点

- クラス最高性能を実現

- 大規模なCPUファームやマルチコア・マシンでのスケーラブルなパフォーマンス

- DRCエラーレポートのグラフィカル/テキスト表示により、容易なナビゲーションが可能

- 初めての方から上級者まで直感的に操作可能

- Tower Semiconductor、X-FAB、UMCのプロセスでシリコン実証済み、ファウンドリ認証済み

用途

- アナログ・ミックスドシグナル、デジタル、MEMS、メモリ、フォトニクス、パワー・マネージメント、フラットパネル、耐放射線デザイン、RFデザイン

パフォーマンス

SmartDRCは、フラットDRC、階層DRC、どちらの実行方法においても、シングルコア/マルチコア実行において、予測可能なスケーラビリティを実現します。ファウンドリで認証された180nmの既存の複雑なルール・セットの場合、SmartDRCはワンショット技術を利用して、フラットDRCでも約1,600万トランジスタ/時間の処理が可能です。

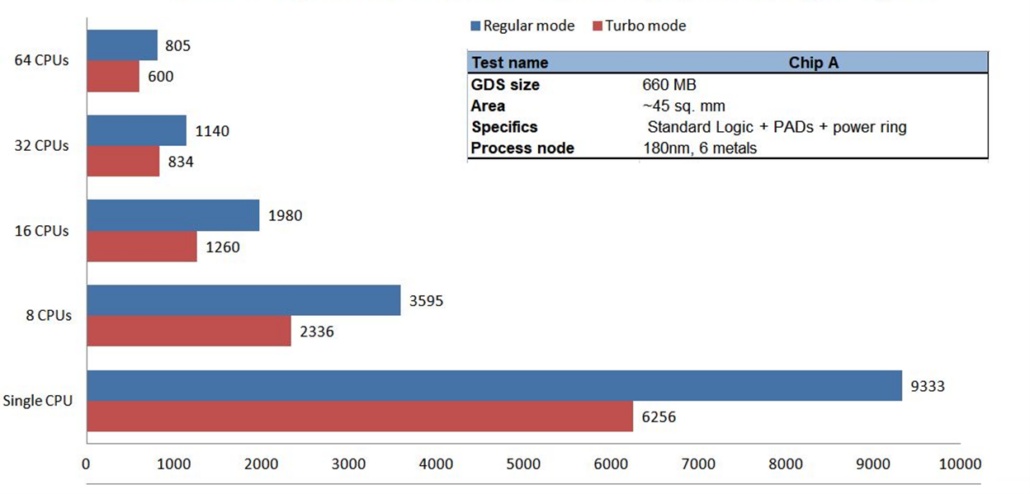

下の図では、6層メタル・レイヤを使用した標準ロジック、PAD、電源リングを含む180nmプロセスのデザインに対して、ファウンドリ認定のルール・デッキを使用してDRCを行っています。フラットなGDSファイルのサイズは660MBでした。CPUの数を増やしながら実行した場合の実行時間を秒単位で示しています。ターボ・モードはヒューリスティックなアルゴリズムであり、ほとんどのデザインにおいて精度の低下を最小限に抑えながら、実行時間を短縮することができます。シングルCPUでの実行と比較して、64CPU構成では10倍のパフォーマンス向上が見られます。また、32CPU構成から64CPU構成に変更しても25%以上のパフォーマンス向上が見られ、SmartDRC/LVSの解析技術の優位性を示すものとなっています。SmartDRC/LVSは、市場で確立されている物理検証ツールと同等以上のパフォーマンスを誇っています。

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

新機能Design Explorerを使ったアナログ回路設計とポストレイアウト・シミュレーション

SmartSpice Signal Integrity 最新機能の紹介

RPI TFTモデルの理解と実装(2)リーク電流モデル