SmartDRC/LVS 物理验证

SmartDRC/LVS用于模拟、数字和混合信号IC的物理验证,包括设计规则检查(DRC)、版图连接性提取和版图与原理图(LVS)比较。其独特的体系结构使用多个CPU,能够提供高性能和高容量,精确处理复杂形状,并通过快速交互验证和直观调试实现卓越的用户高效性。SmartDRC/LVS经过硅验证,并通过了Tower Semiconductor、X-FAB和UMC等多家foundary的工艺认证。

概述

越来越复杂的设计和不断缩小的工艺几何结构推动了对高效物理验证环境的需求,包括快速建立规则和技术文件的能力,从设计输入到验证的高效数据流,以及验证工具快速处理大型分层设计的能力和性能。用户对工具的需求是:简明的设计导航、直观的可视化操作、快速的调试和错误识别与矫正。准确的版图物理结构参数计算至关重要,SmartDRC/LVS对于特殊工艺需求拥有处理复杂图形以及任意角度图形的能力。

SmartDRC/LVS具有独特的性能来满足这些不断增长的需求。凭借多线程处理、优化的层操作、高效的内存管理和高级算法,实现了卓越的工具性能。

SmartDRC/LVS已经集成在Silvaco的版图编辑工具Expert和电路编辑工具Gateway中,能够帮助客户用可视化方法高效精确定位设计问题和探究设计规则冲突,并迅速采取行动解决问题。SmartLVS从版图版图中提取网表,并为用户提供交叉比较原理图和版图的能力。

功能特性

DRC/LVS

- DRC(设计规则检查)

- LVS(版图与原理图校验)

- NVN(网表校验)

- 创新的“One-Shot”版图扫描计算模式,可实现版图规模和扫描时间近乎于线性关系,使运行时间具有可预测性

- 可支持天线规则、版图密度、焊接PAD、闩锁效应和其他特殊规则检查

- 特定器件的任意角度检查

- 软件运行和结果调试GUI环境(RDE)

- 层次化错误结果浏览与定位

- 忽略机制

- 在版图编辑工具Expert中浏览结果

- LVS交叉指针

- 综合报告和摘要

- 清晰且强大的可编程语言

- 可集成于Expert或其他版图编辑器

- 开源支持

优势

- 一流的性能,与其他供应商的同类产品具有可比性甚至更优

- 在大型CPU集群和多核机器的可扩展性能

- 图形化和文本化的DRC结果报告可轻松导航和可视化

- 面向新用户和专家的直观体验

- 在Tower Semiconductor、X-FAB和UMC等晶圆厂获得工艺认证。

应用

- 模拟混合信号、数字、MEMS、存储器、光子学、电源管理、平板、抗辐射和射频设计

性能

SmartDRC不论在单核或多核CPU运行模式下,用平面运行亦或分层运行方法,均具有很好的运行时间控制能力。对于现有在180nm工艺平台使用客户结果,SmartDRC利用其“One-Shot-Scan”算法,兼顾运行状态平稳,每小时可处理约16M个晶体管。

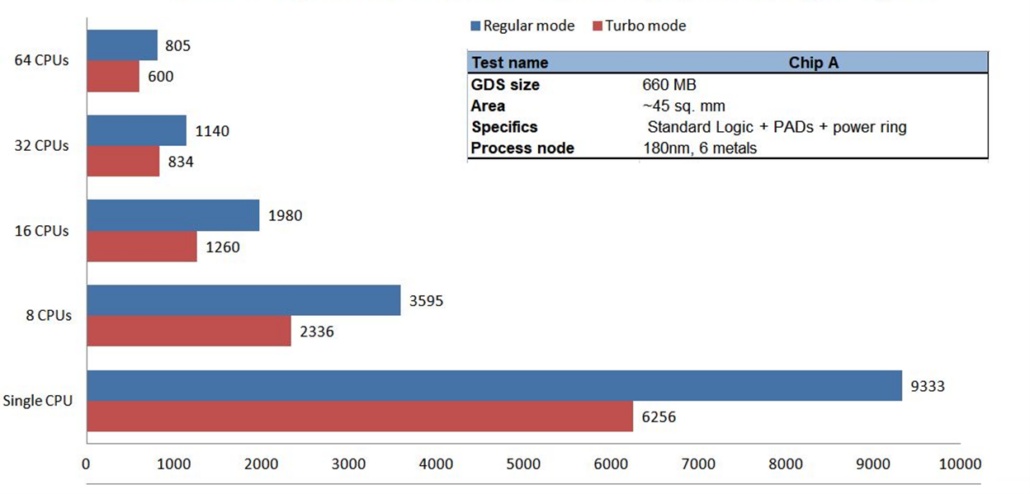

如下图,SmartDRC在180nm技术节点对某个设计版图进行标准规则DRC分析检查。其中包括,六层金属互联的标准逻辑、焊接PAD和电源环。版图为660MB,以秒为单位显示CPU数量与运行时间关系。Turbo算法可在最小的精度损失下加快大多数设计的运行时间。与单CPU相比,64 CPU配置的性能提高了10倍。从32到64个CPU,性能仍有超过25%的提升,这表明了SmartDRC/LVS分析技术的优势。SmartDRC/LVS产品表现与业界其他类的物理验证工具相比具有很强的竞争力。

如何使用 Viso 检查、分析和解决复杂的寄生问题

Si、GaN和SiC功率器件的SPICE建模

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors