SmartSpice:电路仿真

Silvaco的SmartSpice™是一款高性能并行SPICE模拟器,具有业界领先的精确度。它是一个经过验证的综合解决方案,适用于复杂的高精度模拟和混合信号电路、存储器、定制数字设计以及先进半导体工艺的特征单元库的仿真。

它使用智能架构,部署了多个解算器、步进算法和计算技术,实现了准确、稳健的收敛结果以及业界领先的性能和容量——超过800万台有源设备。它与HSPICE®和Spectre®兼容,支持经校准的先进工艺SPICE模型,包括TFT、OTFT、SOI、HBT、FRAM和FinFET等。SmartSpice与Silvaco原理图编辑器Gateway和波形查看器SmartView集成,可无缝融入前端模拟IC设计流程。它支持多线程并行仿真和跨网络CPU的分布式多任务处理,从而加快分析速度。

应用

- 模拟、混合信号电路

- 存储器设计

- FPD设计

- 定制数字电路

- 单元库特征化

Rubberband实时电路分析功能

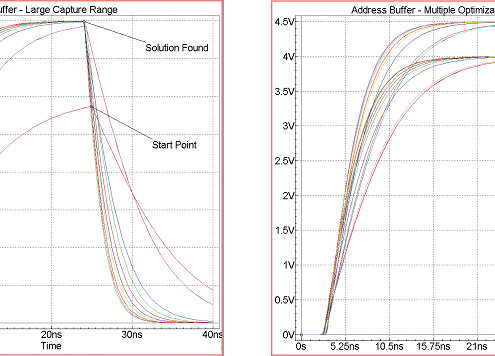

使用SmartSpice和Gateway的Rubberband功能,轻松改进模拟设计。当用户更改模型或器件实例在各种组合中的参数,Rubberband功能可以实时反馈电路性能变化。

本地优化

SmartSpice为电路进行参数优化,它拥有整合的界面和交互式显示系统,可将优化过程的可视化。支持性能测量和函数曲线优化。

性能测量优化

- 电路元件的值和参数可自动更改,使单个电气特性满足规格要求。

- 可以微调延迟、上升/下降时间、跳变点、最大和最小电流,以及其他任何可由SmartSpice .MEASURE语句计算的电路性能。

- 多目标同时优化,支持同时进行几个性能测量优化。

函数曲线优化

- 对于DC、AC和瞬态分析的计算曲线,函数曲线优化功能通过将其与期望曲线拟合来进行优化。 期望曲线是TCAD 仿真或者实际测量的结果。

- T不受电路分析类型的限制,可进行电路的稳态优化、频率优化和时域优化等。

Verilog-A语言环境

SmartSpice的Verilog-A语言为电路设计师和模型开发人员提供了一个易于使用的综合环境,用于设计和验证复杂的模拟和混合信号电路和模型。支持通过行为建模对模拟和混合信号电路进行自上而下的设计和自下而上的验证。Verilog-A源代码的编译和加密支持使用专用模型和模拟IP,而无需公开源代码。

关键功能特性

- 集成调试器和开发环境,加速开发紧凑行为模型

- 与Verilog-AMS 2.3.1语言规范的所有仿真特性兼容

- 以多种分布方式(高斯、指数、泊松、卡方、Student’s T分布和Erlang分布等)处理小信号和噪声源

- 支持时间积分/导数、偏导数、跃变、斜率、拉普拉斯变换和Z变换等模拟运算

- 为模拟电路锁相环、VCO、A/D和D/A等设计构建原型,以便在详细电路设计之前进行原型设计

- 支持混合信号电路的数字组件设计,如Sigma-Delta转换器

如何使用 Viso 检查、分析和解决复杂的寄生问题

Si、GaN和SiC功率器件的SPICE建模

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors