嵌入式存储器编译器IP

Silvaco提供行业首款具有处理器速度的缓存存储器编译器,用于高性能计算(HPC)和人工智能(AI)存储解决方案。Silvaco超高速缓存存储器是一种自适应的非一致性缓存IP,具有先进的缓存架构和逻辑规则位单元。这种架构提升了系统性能、可扩展性、能源效率、数据局部性、应用响应性、成本优化和市场竞争力,提供了独特的商业价值。

Silvaco还提供多种嵌入式存储器编译器,其架构针对性能、功耗和密度进行了优化,同时在各种工艺技术下的良率都十分稳健,帮助设计师在性能、功耗和面积之间取得最佳平衡。

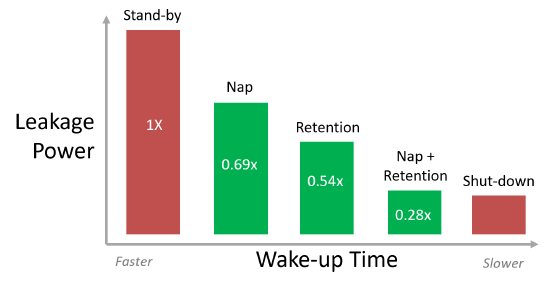

凭借先进的电源管理功能,我们的存储器编译器可以满足具有挑战性的低功耗、低漏电和低电压设计要求。

Learn How SilTerra Uses Cello and Viola for Standard Cells and I/O Library Optimization and Characterization

Learn About Silvaco’s AMBA AHB Subsystems and How to Customize, Secure, and Verify

Designing with Silvaco’s Octal SPI Memory Controller with Advanced Memory Support for IoT Systems

Achieving Extreme Low Power IoT Designs with Silvaco’s 55LPx Foundation IP Solution

Development & Delivery of Complete IO & ESD Library in 5 Weeks