SmartSpice RadHard Radiation Effects Circuit Simulator

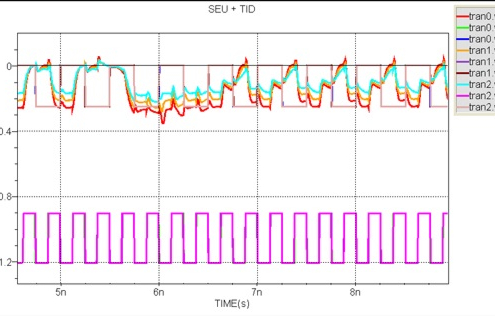

SmartSpice RadHard provides simulation capability for modeling and analyzing radiation effects due to Single Event Effects (SEE), and Dose Rate (DR). Built upon the commercial SmartSpice Analog Circuit Simulator, it provides the accuracy, capacity and performance required to design and analyze the most advanced electronics and analyze the most advanced semiconductor technologies.

Key Features

- Provides accurate Dose Rate (DR), SEE, analysis using the .RAD statement for transient and DC analysis

- Built as an extension to industry-proven SmartSpice simulator

- Analyzes DR with modified Wirth & Rogers’ models and with optional customer-defined models

- Analyzes Single Event Upsets (SEU’s) and Multi-Bit Upsets (MBU’s) with modified Messenger’s models and with optional customer-defined models

- Advanced circuit optimization improves the radiation tolerance of the your design and enables complex analysis of design trade offs necessary to meet system specifications

- Supports standard foundry-supplied HSPICE®, PSPICE® and SmartSpice models for bulk CMOS, SOI, bipolar, an biCMOS processes

- Provides open model development environment and extensive analog behavioral capability with Verilog-A option

- Supports research of new and emerging phenomena through custom models and sophisticated ‘what if’ features in simulator control

- SmartSpice RadHard is fully integrated into the Silvaco radiation tool flow which links process modeling, device simulation, circuit analysis, physical layout, and chip parasitic effects to deliver a high fidelity, physics based environment to assess radiation and reliability effects

Single Event Effects Analysis

- Radiation physics incorporated through enhanced, fully complied versions of industry standard device models as opposed to subcircuits

- Customer-defined current pulse modeling

- Rapid, user friendly radiation effects analysis capability without complicating circuit netlists

- Single bit upset analysis

- Multi-bit upset analysis

如何使用 Viso 检查、分析和解决复杂的寄生问题

Si、GaN和SiC功率器件的SPICE建模

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors