Hipex フルチップ寄生素子抽出

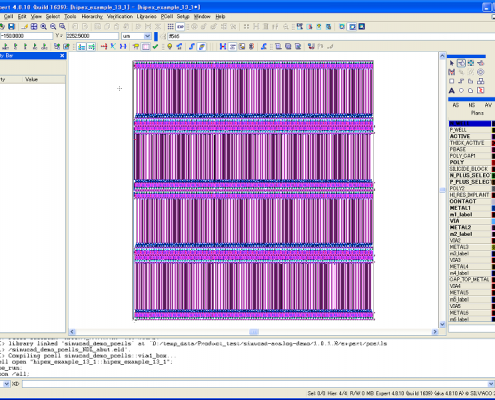

Hipex™は、階層レイアウトからの寄生容量と寄生抵抗の抽出を高精度かつ高速に実現するソリューションで、アナログ、ミックスドシグナル、メモリIC、SoCの設計に適しています。 シルバコのアナログ・カスタム・デザイン・フローを構成するツールの1つであり、シルバコのExpertレイアウト・エディタと緊密に連携して、DRC/LVS検証から寄生RC抽出までの統合デザイン・フローを実現します。

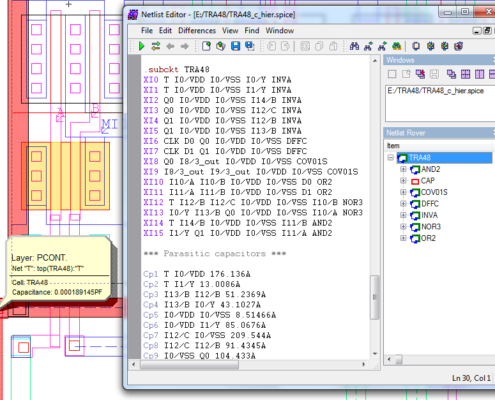

Hipexは、GDSII、セル・ネットリスト、およびルール・ベースのテクノロジ・ファイルに対応しており、レイアウトからの寄生抵抗と寄生容量の値を高精度で抽出することができます。また、フルチップ、指定したネットまたはノードに対して抽出を実行し、抽出した寄生RCを含む回路図ネットリストにバックアノテートすることが可能です。

Hipexのデバイス抽出機能は、元のレイアウト階層が保持された階層ネットリストを生成でき、スタンダード・デバイスおよびユーザ定義のパラメタライズド・デバイスを含む幅広いデバイスをサポートしています。配線のショートやオープン、あるいは未接続のデバイスを検出するERC (電気的ルール・チェック)機能も備えています。

複数のサーバを使用した効率的な並列処理が可能なHipexは、大規模なフルチップ・デザインのための高速処理とメモリ使用量の効率化を実現します。

特長

- 3次元抽出に近い精度の、高速な2次元抽出

- SoCや大規模メモリに対して、選択したクリティカル・ネットまたはレイヤから抽出することで解析時間を短縮可能

- 多岐にわたる寄生抽出モデル(集中RC、容量のみ、抵抗のみ、カップリング容量、分配RCなど)をサポート

- 回路図のノード、寄生抵抗、および寄生容量の抽出結果をネットリストにバックアノテート

- 複数の抽出モデルと方程式ソルバにより、45°、90°以外のデバイスや任意の抵抗形状も高精度に抽出

- 抽出した寄生RCをP2P形式で出力して、ネット別の合計容量、および指定した2点間の抵抗を取得可能

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

新機能Design Explorerを使ったアナログ回路設計とポストレイアウト・シミュレーション

SmartSpice Signal Integrity 最新機能の紹介

RPI TFTモデルの理解と実装(2)リーク電流モデル