Hipex Full-chip Rule-based RC Parasitic Extraction

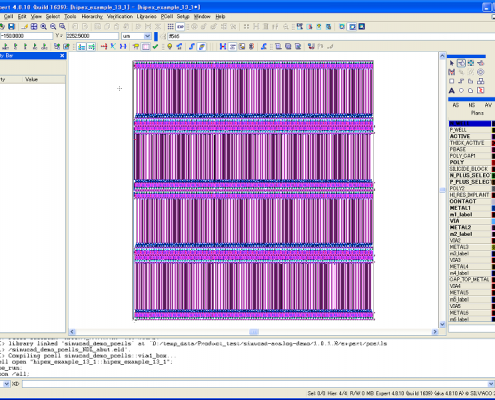

Hipex-RC provides an accurate and fast solution for the extraction of parasitic capacitance and resistance from hierarchical layouts of analog, mixed-signal, memory IC and SoC designs. As part of Silvaco’s complete analog custom design flow, RC parasitic extraction together with DRC/LVs is tightly integrated with the Silvaco Expert layout editor.

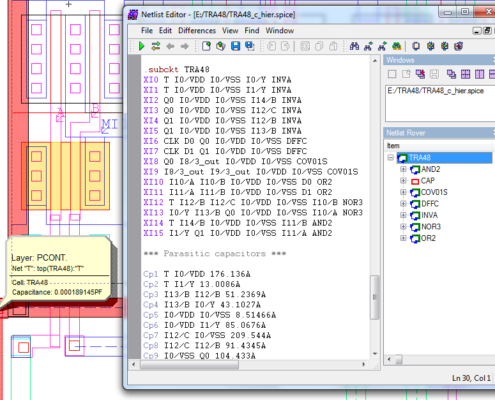

Working from GDSII, cell netlists and rule-based technology files, Hipex-RC performs the parasitic extraction for either the full chip or selected nets or nodes, then back-annotates the schematic netlist with the extracted parasitics.

The device extraction capabilities of Hipex-RC allows the generation of hierarchical netlists that preserve the original layout hierarchy and supports a wide range of standard and parameterized user-defined devices. In addition it performs electrical rule checking (ERC) for shorts, opens and dangles.

Built for efficient parallelization on multi-processing servers, Hipex-RC is fast with efficient memory usage for large, full chip designs.

Features

- Performance of a fast 2D extractor with capacitance calculation near 3D accuracy

- Fast analysis of user selected critical nets or layers without extracting the full-chip

- Supports lumped RC, C only, R only, Coupled C and fully distributed RC extraction

- Back-annotates the extracted netlist with schematic node names, parasitic resistances and capacitances

- Accurate device extraction for non 45 and non 90 degrees devices and arbitrary shape resistors

- Enables total per net capacitance and point-to-point resistance calculation by providing extracted parasitic RC in P2P format

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors