Hipex and Victory RCx Pro Parasitic Extraction

Silvaco offers both rule and field-solver based RC parasitic extraction software.

Full-chip Rule-based RC Parasitic Extraction

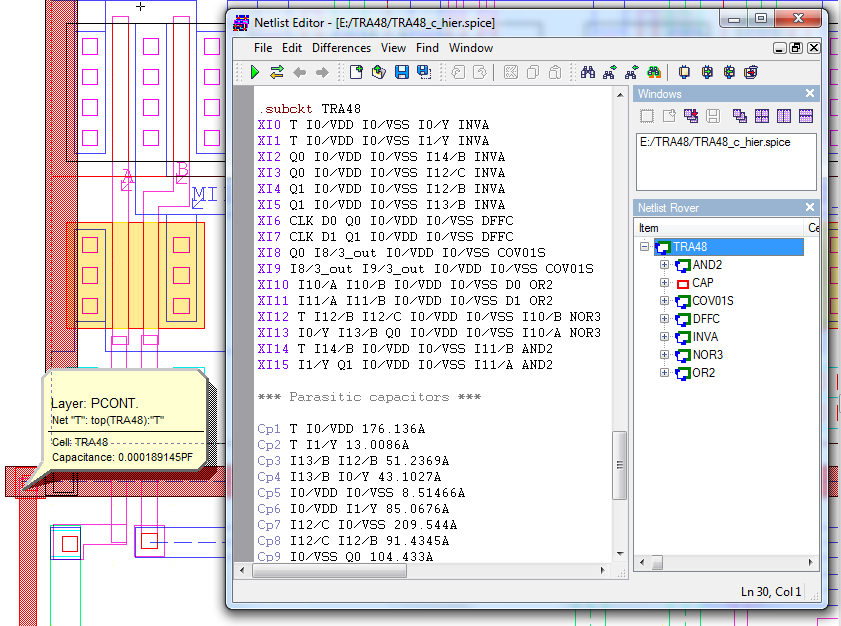

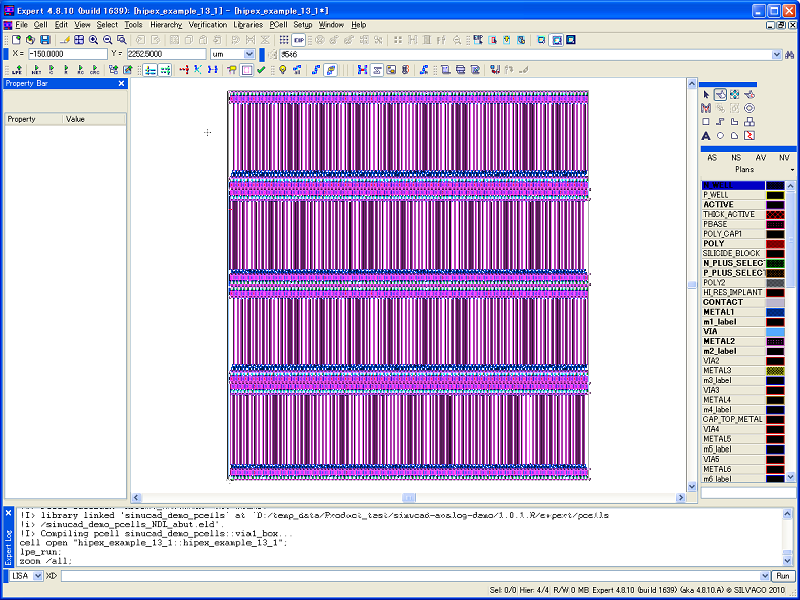

Hipex-RC provides an accurate and fast solution for the extraction of parasitic capacitance and resistance from hierarchical layouts of analog, mixed-signal, memory IC and SoC designs. As part of Silvaco’s complete analog custom design flow, RC parasitic extraction together with DRC/LVS is tightly integrated with the Silvaco Expert layout editor.

Working from GDSII, cell netlists and rule-based technology files, Hipex-RC performs the parasitic extraction for either the full chip or selected nets or nodes, then back-annotates the schematic netlist with the exacted parasitics.

The device extraction capabilities of Hipex-RC allows the generation of hierarchical netlists that preserve the original layout hierarchy and supports a wide range of standard and parameterized user-defined devices. In addition it performs electrical rule checking (ERC) for shorts, opens and dangles.

Built for efficient parallelization on multi-processing servers, Hipex-RC is fast with efficient memory usage for large, full chip designs.

Field-Solver RC Parasitic Extraction

Silvaco has two field-solver RC parasitic extraction tools: Victory RCx Pro and Hipex-FS.

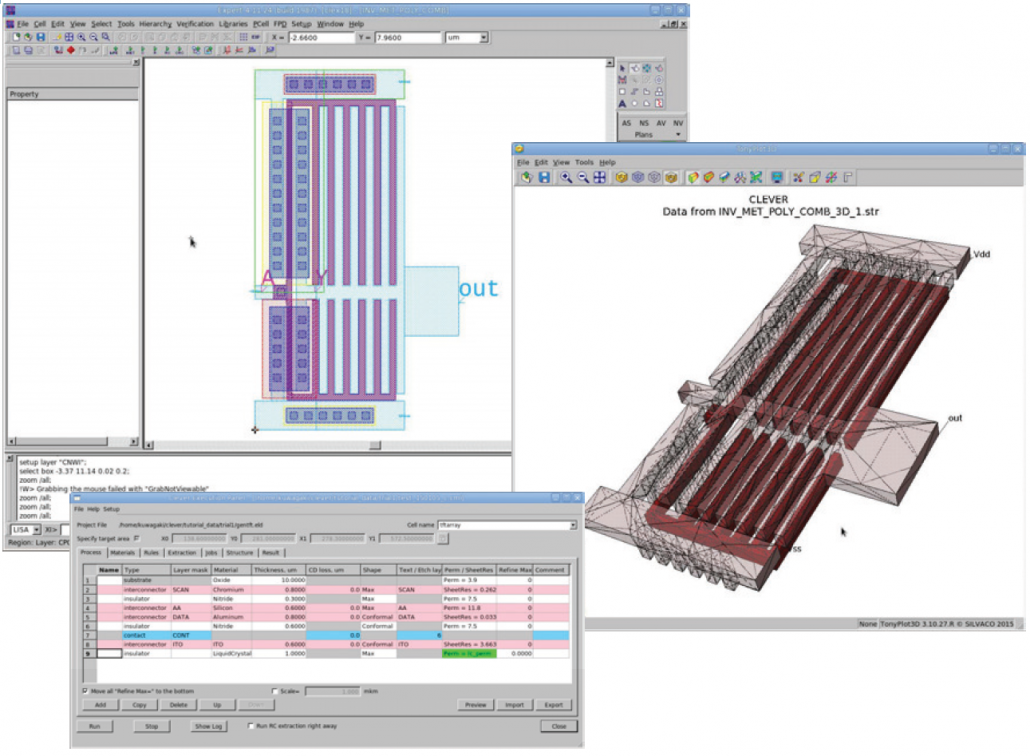

Hipex-FS is driven via the Silvaco Expert layout tool, for an designer-friendly 3D field solution based RC extraction, utilizing the same physics and solvers as Victory RCx Pro.

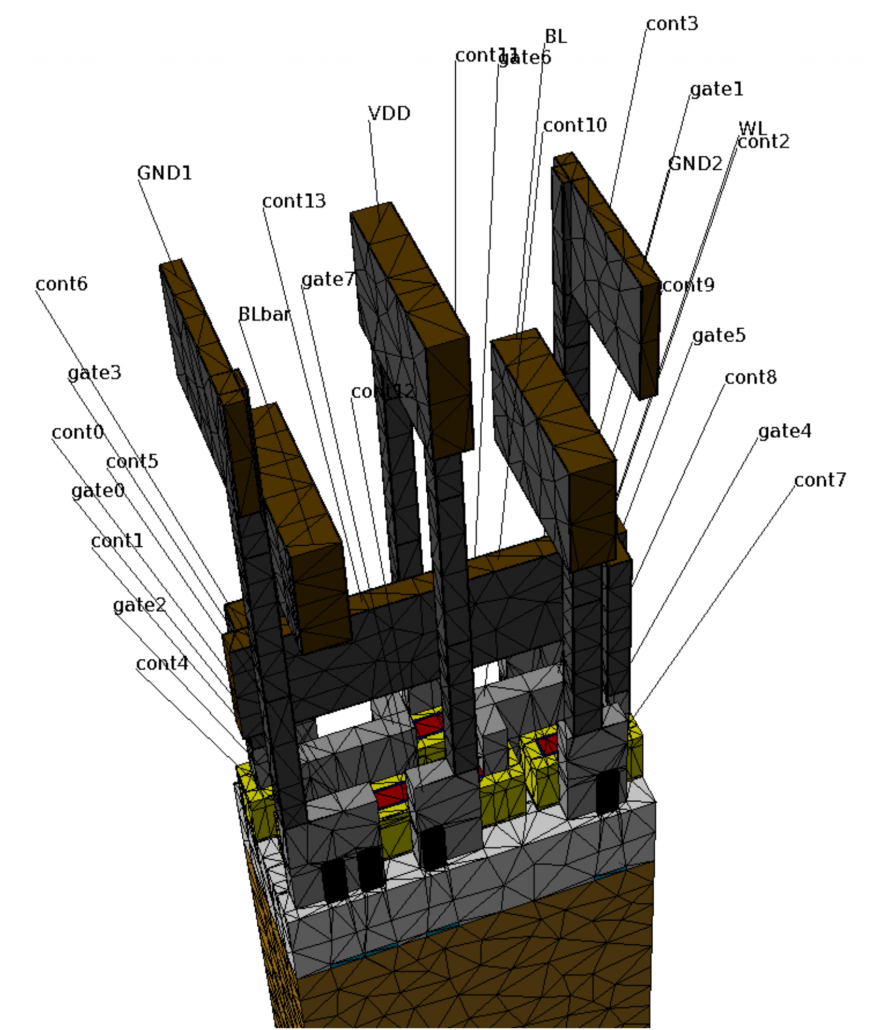

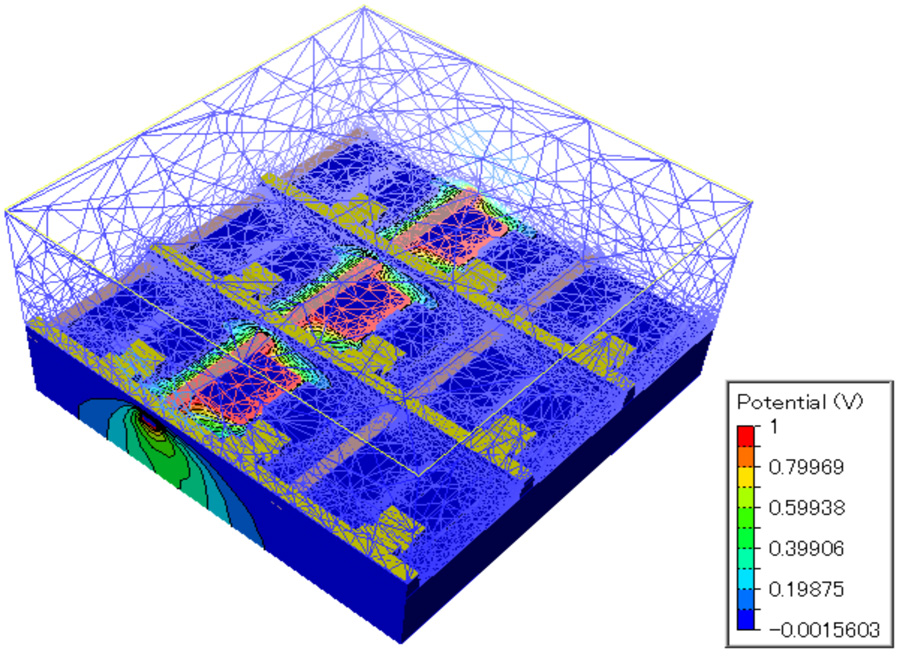

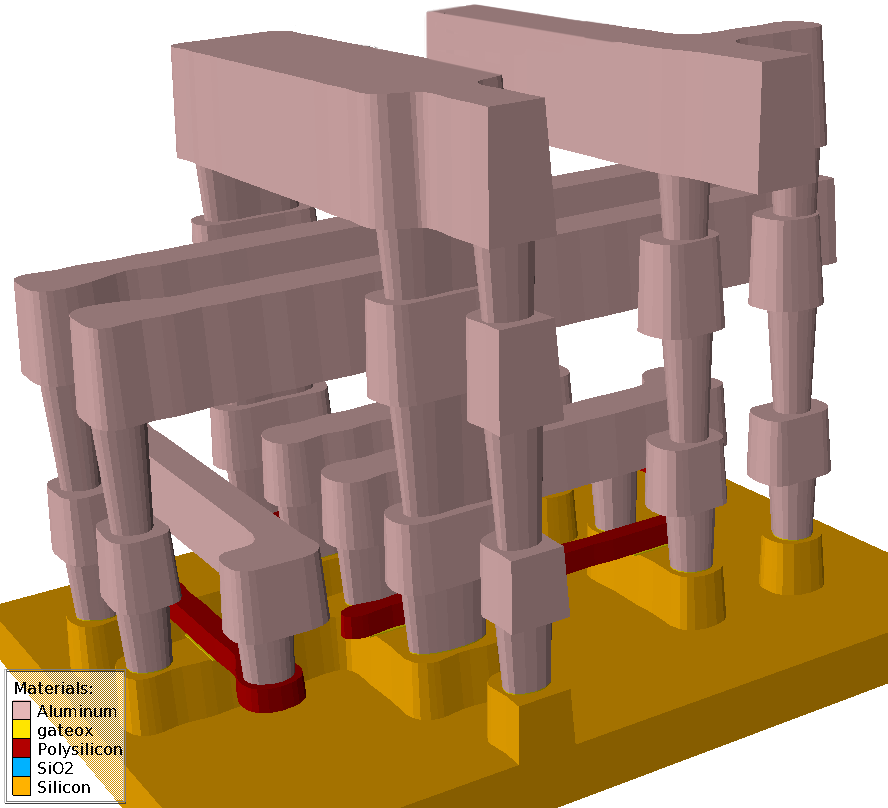

Victory RCx Pro is a TCAD-like solution, and is ideal for detailed extraction of cell layouts and is a physics-based resistance and capacitance field solver for any arbitrary 3D shaped structure.

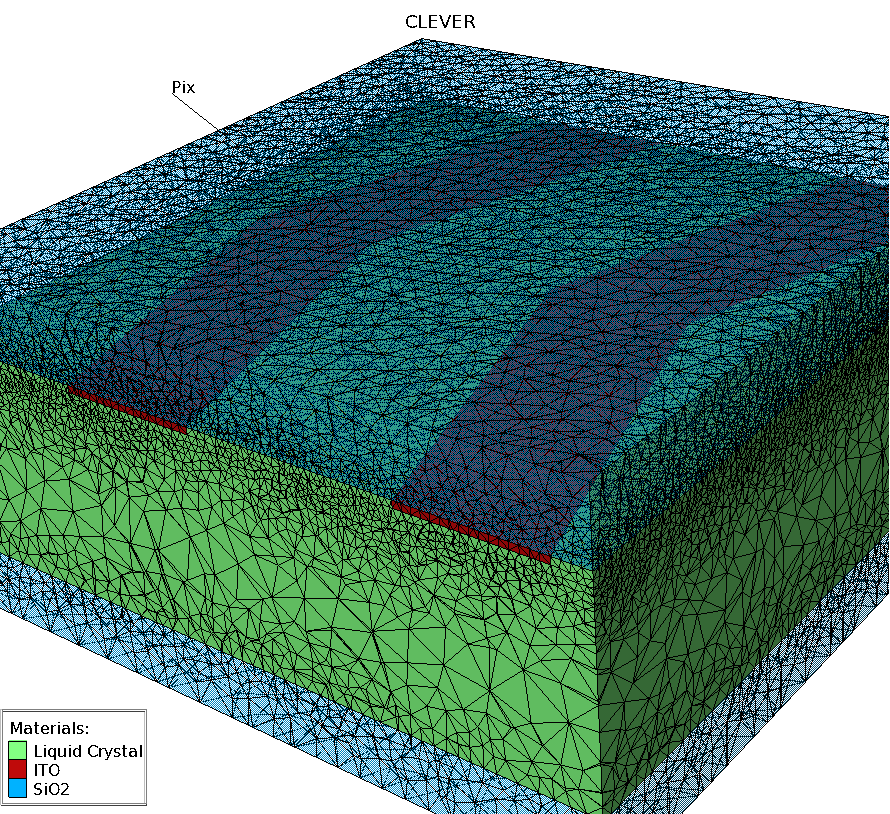

Both Victory RCx Pro and Hipex-FS performs RC extraction with the highest accuracy, productivity and versatility for the most complicated interconnect cells, including realistic etching and deposition processes. The local adaptive-mesh refinement (AMR) feature allows the user to specify a desired accuracy. It will automatically refine the unstructured mesh where required, optimizing maximum accuracy, together with minimum simulation time.

Benefits

- Multiple options depending on size/complexity of design

- Resolve complex non-planar geometries with structural accuracy for more precise RC extraction

- User accuracy control for optimal runtime

- Output in SPICE netlist form for universal compatibility

Applications

- Advanced CMOS and FinFET, SOI, Bulk CMOS

- Display-TFT, LCD, Touch Panel

Organic Transport Model for Tandem Organic Light-Emitting Diode

Enabling the Next Generation of High-Voltage Power: Gallium Oxide Trench Schottky Diodes from Simulation to System

Victory TCAD 2025 Release

Accelerating Vertical GaN Power Technology Development with Physics-based Digital Twins for 800V DC AI Factory Power Infrastructure