Hipex and Victory RCx Pro Parasitic Extraction

실바코는 룰과 필드-솔버에 기초한 RC 기생 추출 소프트웨어를 제공합니다.

Full-chip Rule-based RC Parasitic Extraction

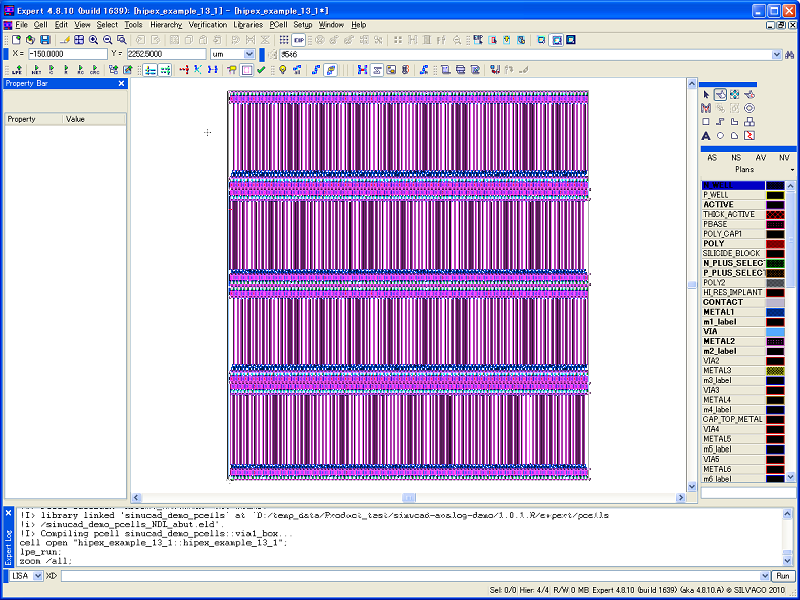

Hipex-RC는 아날로그, 믹스드 시그널, 메모리 IC, SoC 디자인의 계층형 레이아웃으로부터 기생 캐패시턴스와 저항을 추출하기 위해 빠르고 정확한 솔루션을 제공합니다. 실바코의 아날로그 커스텀 디자인 플로우의 일부분으로서, DRC/LVS와 함께 실바코의 Expert 레이아웃 에디터와 긴밀하게 연계되어 있습니다.

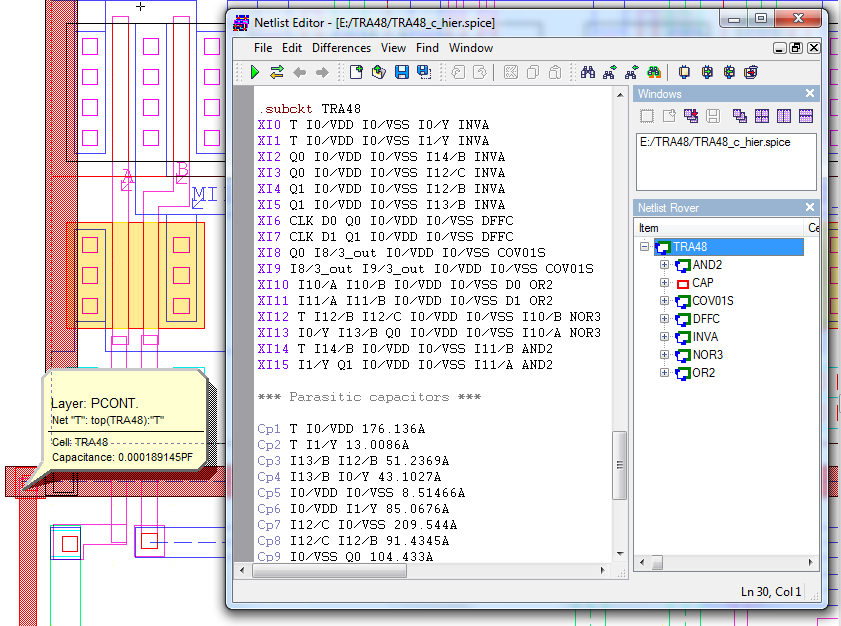

Hipex-RC는 GDSII, 셀 넷리스트 및 룰에 기초한 테크놀로지 파일로부터 전체 칩 또는 선택한 넷/노드에 대해 기생 성분을 추출하여, 스키매틱 넷리스트에 백 애노테이션을 실행합니다.

Hipex-RC의 소자 추출 기능으로 계층형 넷리스트를 생성하여, 원본 레이아웃 계층을 보존하며, 광범위한 표준 소자 및 파라미터로 명시한 사용자 정의 소자를 지원합니다. 또한, 단락, 개방, 댕글에 대해 전기적 룰 체크 (ERC)를 실행합니다.

멀티 프로세스 서버에 대해 효율적인 병렬화를 지원하여, 대규모의 전체 칩 설계에 메모리를 효과적으로 사용하여 빠른 속도를 구현합니다.

Field-Solver RC Parasitic Extraction

실바코는 두 개의 필드-솔버 RC 기생 추출 툴을 제공합니다: Victory RCx Pro, Hipex-FS

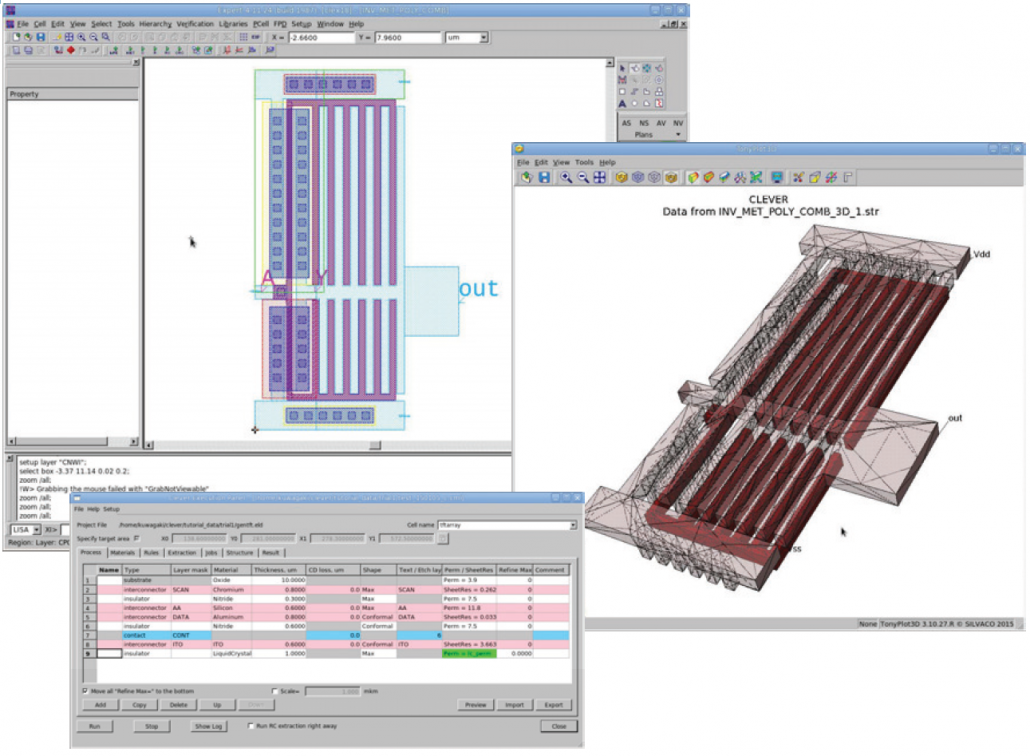

Hipex-FS는 실바코의 Expert 레이아웃 툴을 통해 실행되며, 설계자에 친숙한 3D 필드 솔루션 기반 RC 추출에 Victory RCx Pro와 동일한 물리학 및 솔버를 활용합니다.

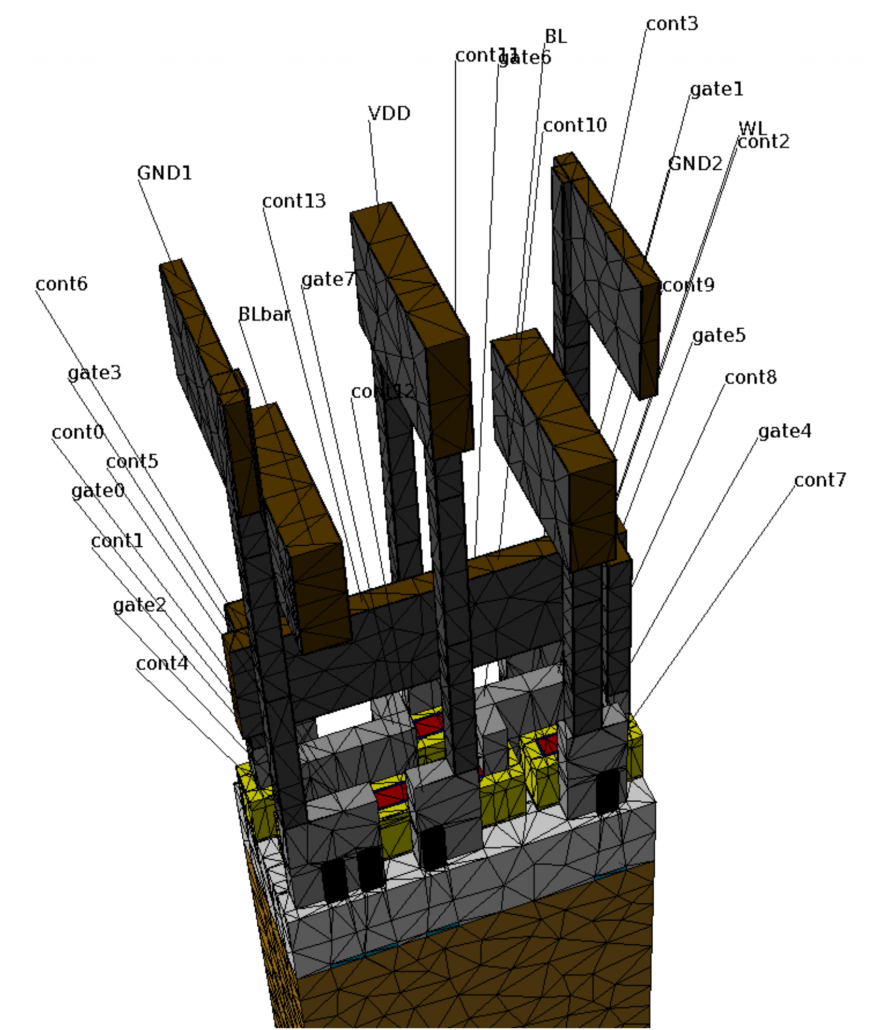

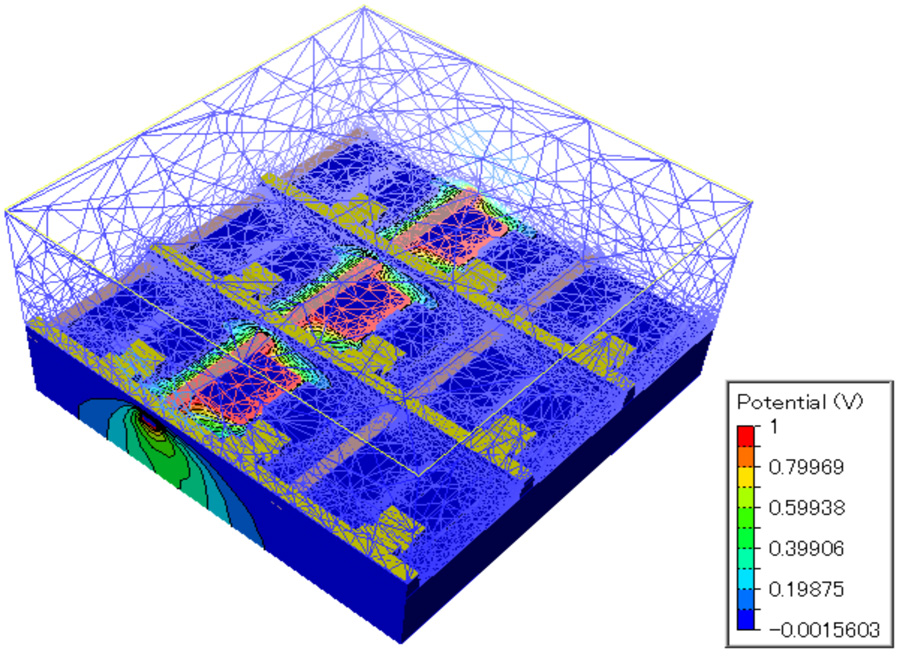

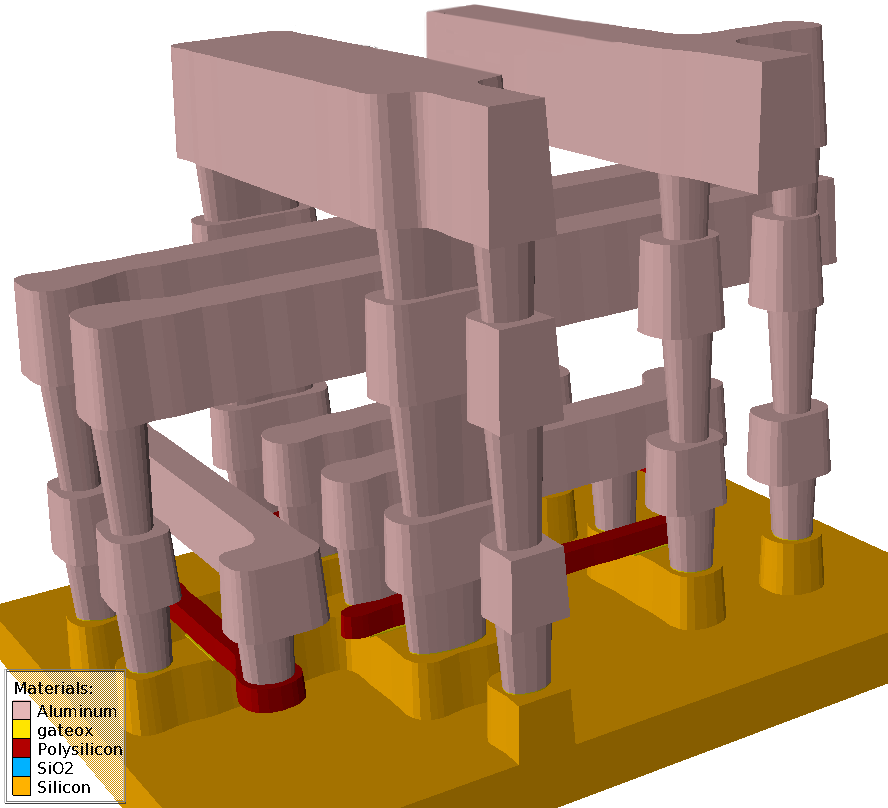

Victory RCx Pro는 TCAD와 유사한 솔루션으로서, 셀 레이아웃의 세밀한 추출에 이상적이며, 임의의 3D 형상 구조에 대해 물리학에 기초한 저항 및 캐패시턴스 필드 솔버입니다.

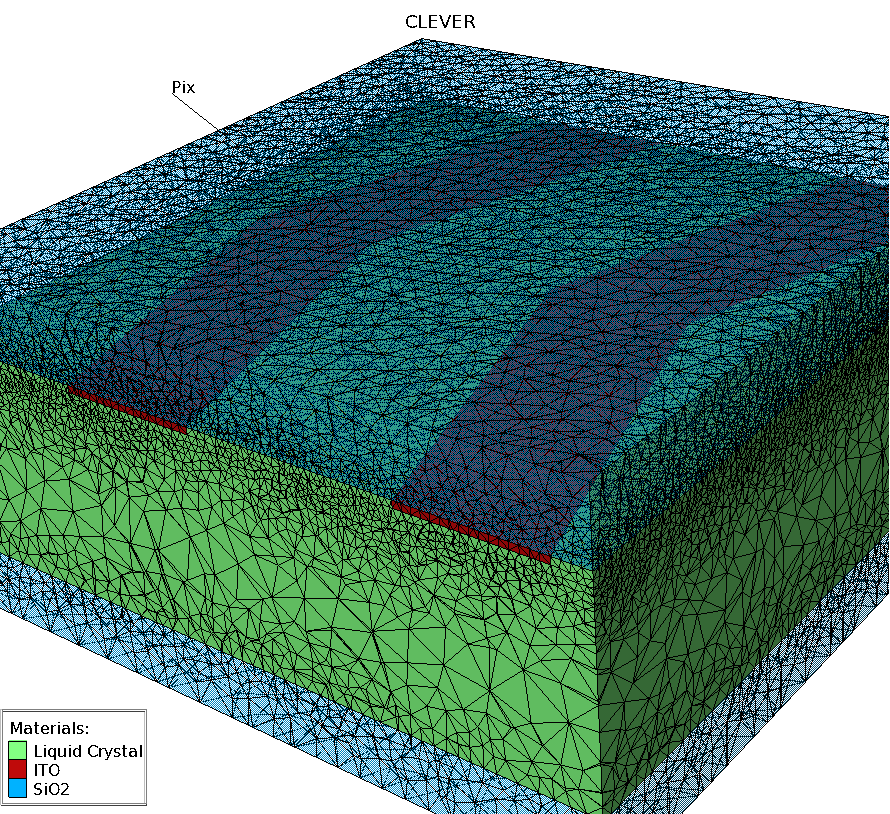

Victory RCx Pro와 Hipex-FS 모두 실제적인 식각과 증착 공정 등을 포함하여, 가장 복잡한 인터커넥트 셀에 대해 고도의 정확성, 생산성, 유연성으로 RC를 추출합니다. 부분 적응형-메쉬 개선 (Adaptive-Mesh Refinement, AMR) 기능으로 원하는 대로 정확성을 설정할 수 있습니다. 최소 시뮬레이션 시간으로 정확성을 최적화하여, 자동으로 비구조화 메쉬를 세밀하게 생성합니다.

장점

- 설계의 크기 및 복잡도에 종속적인 다양한 옵션

- RC를 보다 정밀하게 추출하기 위해 정확한 구조로 복잡한 비평면 구조를 해결

- 실행 시간을 최적화하기 위해 정확성을 제어

- 범용적인 호환성을 위해 SPICE 넷리스트 형식으로 출력

적용

- 최신 CMOS, FinFET, SOI, 벌크 CMOS

- 디스플레이 – TFT, LCD, 터치 패널

Organic Transport Model for Tandem Organic Light-Emitting Diode

Enabling the Next Generation of High-Voltage Power: Gallium Oxide Trench Schottky Diodes from Simulation to System

Victory TCAD 2025 Release

Accelerating Vertical GaN Power Technology Development with Physics-based Digital Twins for 800V DC AI Factory Power Infrastructure