라이브러리 디자인 서비스

실바코는 완전히 독립적인 써드파티 IP 벤더 또는 고성능 라이브러리의 개발의 파트너로서 스탠더드 셀 라이브러리 설계 및 최적화 서비스를 제공합니다.

제공되는 가장 일반적인 서비스는 다음과 같습니다:

- 스탠더드 셀 라이브러리 개발

- 스탠더드 셀 라이브러리 및 설계 최적화

- 성능 추가 셀

- IP 마이그레이션 및 라이브러리 변형의 생성

- 라이브러리 특성화 서비스

스탠더드 셀 라이브러리 개발

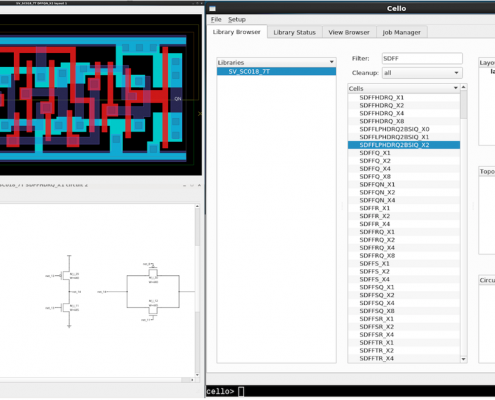

실바코는 .35um~20nm 기술 노드 분야에서 20년 이상의 경험을 보유하고 있으며, 현재 14nm 미만 레벨에서 대형 파운드리 및 팹리스 IC 기업과 파트너로서 일하고 있습니다. 당사의 완벽한 스탠더드 셀 라이브러리는 최대의 밀도 및 라우팅 성능을 입증했습니다. 보다 복잡한 셀에 사용되는 셀 스키매틱 또한 고성능, 고밀도 설계 최적화를 위한 옵션을 제공합니다. 패키지의 일부로서, 모든 산업 표준 뷰(CDL netlist, LEF, GDSII, Liberty, PEX Spice netlist, Verilog, VITALT, EDIF, OpenAccess db 등)를 일관성 있는 데이터베이스에서 제공합니다. Liberty 파일은 모든 타이밍, 전력, 노이즈 모델과 함께 모든 작동 조건 (PVT 코너)에 대해 도출할 수 있습니다. 다음은 스탠더드 셀 라이브러리에 있는 셀의 예시입니다.

- Inverters, Buffers, Clock cells

- NAND, NOR, AND, OR cells

- AOI, OAI, AO, OA cells

- XNOR, XOR (buffered, unbuffered) cells

- MUX, IMUX cells

- D-type Latches (set, reset) and clock gate cells

- D-type Flops and Scan D-Type Flops (set, reset, both, enable)

- Half-Adder, Full-Adder cells

전원 관리, 보존 및 특수 동작 셀처 특수한 셀을 라이브러리에 추가할 수 있습니다. 실바코는 또한 특정 용도에 필요한 폭넓은 셀 레퍼토리를 포함합니다.

실바코를 라이브러리 IP 공급자 및 파트너로 활용하면 다음과 같은 이점이 있습니다:

- 단시간 내에 저비용, 고품질의 DRC, DFM 친화적인 레이아웃을 구현 – 가장 앞선 레이아웃 개발 툴 제품군인 당사의 Library Creator Platform을 활용;

- 설계 규칙이 변경되는 경우, 신속한 라이브러리 업데이트 (레이아웃 DRC 정리 포함) – 기술 탐색 및 PDK 개발 단계;

- 셀 사양(기능, 스키매틱)의 유연성;

- 라이브러리 변수 생성 옵션 (아래의 IP 마이그레이션 참조)

- .35um~14nm 스탠더드 셀 라이브러리와 CPU/GPU용 애플리케이션별 퍼포먼스 셀에 대한 방대한 경험과 노하우

- 라이브러리의 재 특성화와 같은 광범위한 사후 서비스 – 매우 합리적

스탠더드 셀 라이브러리 및 설계 최적화

실바코는 주요 Tier-1 회사의 설계 팀과 협력하여 프로세서 코어 최적화 (주로 CPU 및 GPU) 경험을 많이 쌓았습니다. 파운드리에서도 실바코의 설계 및 라이브러리 최적화 플로우를 사용하여 벤치마크에서 높은 성능을 달성하였습니다. IP 최적화 부문에서, 실바코는 주로 두 가지의 독립적이지만 상호 보완적인 서비스를 제공합니다:

- 스탠더드 셀 라이브러리 최적화

- 설계 최적화

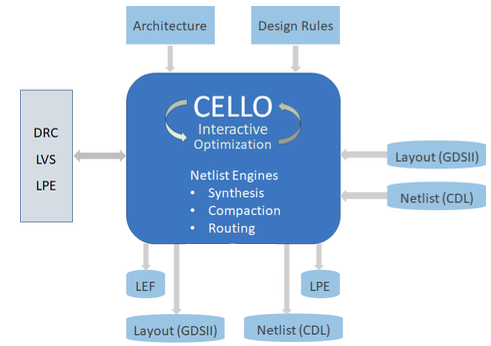

라이브러리가 최상의 퍼포먼스를 발휘하려면 먼저 대상 애플리케이션 (설계)을 알아야 합니다. 또한 디자인의 퍼포먼스는 스탠더드 셀 라이브러리, 매크로 및 사용되는 메모리의 품질에 좌우됩니다. 각각의 최적화는 독립적으로 수행할 수 있고 양호한 결과를 제공하지만, 라이브러리와 설계를 동시에 최적화하는 것은 맞춤형 디자인 플로우와 유사하거나 더 우수합니다. 아래 그림은 동시 최적화의 작동 방식(사이클 단위)을 나타냅니다:

고성능 (고 충격) 셀에 대한 자세한 내용은 아래의 Performance Add-On Cell을 참조하여 주십시오.

Performance Add-On Cell

실바코는 라이브러리 최적화 서비스의 일부 또는 독자적인 IP로서, 특정 대상(성능, 영역, 전원)에 대해 이러한 비 스탠더드 셀을 제공할 수 있습니다.

다음은 실바코가 제공하는 고성능 셀의 예입니다:

- Timing Performance Cells: high-skew, asymmetric, tapered, fast inputs, combined “simple”, XOR/XNOR variants, MUX/IMUX variants, low-gain negative-unate cells, extra drive strengths;

- ECO Timing Cells: footprint compatible variants;

- Power Reduction Cells: High-gain positive-unate cells, gate-length (gate biasing) variants, specialized power latches and clock gates, multi-bit cells, VT variants;

- Area Reduction Cells: Combined functions, highly-dense low drive-strength cells;

- Flip-Flop Variants and custom cells

IP 마이그레이션: 라이브러리 변형 생성

실바코는 IP 마이그레이션 및 라이브러리 변형 생성 기능을 제공합니다. 이는 라이브러리 개발 서비스의 일부로서 또는 다른 벤더의 IP를 통해 수행할 수 있습니다. 실바코는 IP 마이그레이션 서비스에서 많은 경험이 있으며, 다음은 그 예시를 나타냅니다.

- Vt (threshold) 라이브러리 변형;

- 게이트 길이 (게이트 바이어스) 라이브러리 변형;

- 템플릿 (셀 구조) 라이브러리 변형;

- 메탈-스택 풋프린트 호환 라이브러리 변형 (ECO에 사용);

- 셀 높이 및 트랜지스터 크기 라이브러리 변형 등.

IP 마이그레이션 서비스는 보통 매우 저렴한 가격으로 제공되며, 개발 주기가 짧습니다.

라이브러리 디자인 서비스에 대한 자세한 정보는 sales@silvaco.com으로 문의하여 주십시오.