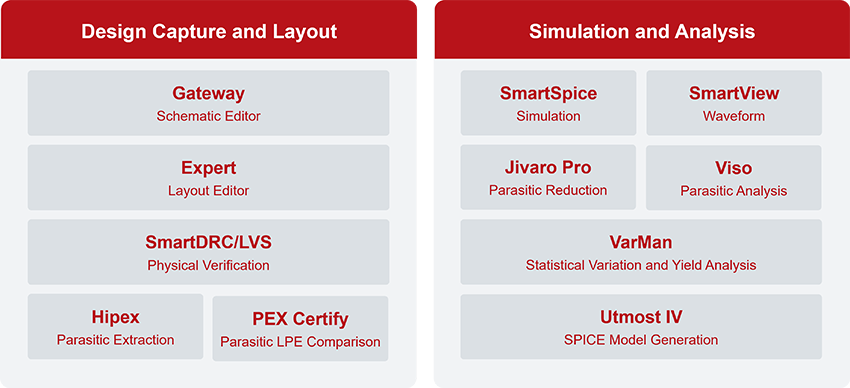

Full Analog IC-CAD Design Flow

실바코는 디자인 캡처, 회로 시뮬레이션, 레이아웃 디자인, 물리 검증, 기생성분 추출 및 감축과 통계적 변동 분석, 수율 분석을 포함한 포스트-레이아웃 분석 등, IC-CAD 전체 디자인 플로우를 제공합니다.

Schematic Editor

Layout Editor

Physical Verification

Parasitic Extraction

Circuit Simulation

Waveform Analyzer

Parasitic Reduction

Parasitic Analyzer and Debugger

Statistical Variation and Yield Analysis

Device Characterization and SPICE Modeling

Parasitic Extraction Comparison

스키매틱 에디터

Gateway 직관적인 편집 기능, 복잡한 대규모 계층 디자인 또는 플랫 디자인 지원, 기존 넷리스트에서 심볼 자동 생성, 업계 표준 넷리스트 및 인터페이스 형식에 대한 지원 등을 갖춘 생산적인 환경입니다. 실바코의 TCAD 및 아날로그 커스텀 디자인 툴과 긴밀하게 연결됩니다.

레이아웃 에디터

Expert는 아날로그, 믹스드 시그널, RF, 디지털 회로에서 다양한 실리콘 기술에 사용할 수 있는 계층식 IC 레이아웃 에디터입니다. 실바코의 커스텀 IC 설계 제품군의 핵심으로서, Expert는 Gateway 스키매틱 디자인 툴 및 SmartDRC/LVS 물리 검증 환경과 원활하게 연결됩니다. Calibre® RealTime은 필요에 따라 대화식으로 연결되어, 사인 오프 품질의 DRC를 제공합니다. Expert의 직관적인 인터페이스, 손쉬운 설정 및 대화식 규칙 검사를 통해 레이아웃을 정확하고 신속하게 작성하여 테이프 아웃할 수 있습니다.

DRC/LVS 물리 검증

SmartDRC/LVS은 설계 규칙 검사 (DRC), 레이아웃 연결성 추출 및 레이아웃과 스키매틱의 비교 (LVS) 등, 아날로그, 디지털, 믹스드 시그널 IC에 대한 물리 검증을 수행합니다. 신속한 대화식 검증과 직관적인 디버깅과 함께 멀티 CPU, 복잡한 형상의 정확한 처리 및 우수한 생산성을 활용하여 탁월한 성능을 제공합니다.

전체 칩의 기생성분 추출

Hipex는 아날로그, 믹스드 시그널, 메모리 IC, SoC 디자인의 계층형 레이아웃에서 기생 캐패시턴스와 저항을 추출하기 위해 빠르고 정확한 솔루션을 제공합니다. 실바코의 물리 IC 설계 검증 플로우의 일부분으로서, DRC/LVS 및 RC 기생성분 추출을 위해 Expert 레이아웃 에디터와 긴밀하게 연결됩니다. Hipex는 빠른 패턴 매칭과 필드 솔버 모드를 지원합니다.

회로 시뮬레이션

SmartSpice는 고성능 병렬 SPICE 시뮬레이터로서, 능동 소자 모델 및 Verilog-A 컴팩트 모델링을 제공하며, 스키매틱, 레이아웃, TCAD 분석 툴과 긴밀하게 연결됩니다. 복잡한 고정밀 아날로그, 믹스드 시그널 회로 시뮬레이션, 메모리, 커스텀 디지털 설계 및 최신 반도체 공정의 셀 라이브러리 특성화 등에 적용할 수 있는 검증된 통합 솔루션입니다.

기생성분 감축

Jivaro Pro는 세계 유수의 IDM 및 팹리스에서 채택하여, 포스트 레이아웃 시뮬레이션 시간 및 리소스 관리의 문제점을 해결하고 있습니다. Jivaro Pro는 기생 성분 감소에 대해 특허를 획득한 수학적 접근방식으로 정확도를 유지하면서, 회로의 복잡도를 줄일 수 있습니다.

기생성분 분석

Viso는 고객 디자인의 목표 성능에 영향을 미칠 수 있는 기생 효과에 대해 신속하고 포괄적인 이해를 제공합니다. 강력한 분석 기능을 통해, Viso는 누화의 영향, 신호 미약, 넷의 불균형 대칭, 지연 저하, IR 드롭 문제 등과 같은 다양한 문제를 해결합니다.

기생성분 추출 비교

PEX Certify PEX Diff, PEX Link로 구성되어, 대규모의 추출 넷리스트를 비교하여 차이를 검증하고 정량화하도록 설계되었습니다. PEX Certify는 시간이 오래 걸리는 회로 시뮬레이션을 실행할 필요없이 기생 성분에 대한 통계와 정교한 분석으로 추출된 두 개의 넷리스트가 일치하는지 빠르게 판단할 수 있습니다.

편차 및 수율 분석

VarMan은 설계자가 통계적 편차를 정확하게 설명하여 올바른 결정을 할 수 있게 하는 포괄적인 분석 툴 셋트입니다. 머신 러닝 기술을 채용하여, 아날로그, RF, 스탠더드 셀, IO, 메모리 설계에 효율적이고, 안정적인 솔루션을 제공합니다.

SPICE 모델 생성

Utmost IV는 최신 CMOS 및 화합물 반도체 소자의 특성 분석 및 모델링에 대응할 수 있는 업계 최고의 솔루션입니다. 반도체 소자의 특성 분석과 아날로그, 믹스드 시그널, RF 애플리케이션에 대해 정확한 고품질 SPICE 모델, 매크로 모델, Verilog-A 모델을 생성하기 위한 데이터베이스 중심의 편리한 환경을 제공합니다.

Viso를 활용한 기생 문제의 조사, 분석 및 해결

Si, GaN, SiC 기술에 대한 전력 소자 SPICE 모델링

SmartSpice를 활용하여 최신 TFT 기반 플랫 패널 설계

Utmost IV를 활용한 소자 모델링의 최신 기술

실바코 플로우를 활용한 FPD 및 검출기의 픽셀 어레이 설계 및 시뮬레이션