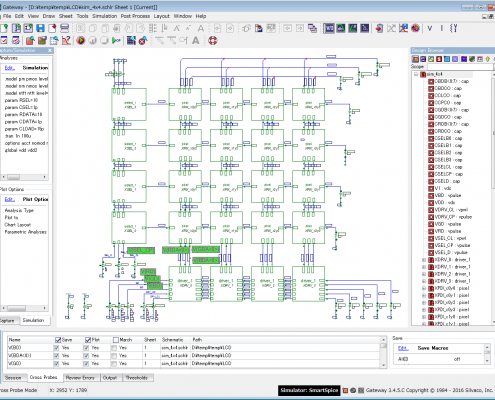

Gateway Schematic Editor

Gateway는 실바코의 계층형 스키매틱 에디터로서 사용하기 쉽고 기능이 풍부한 환경을 제공하여, 아날로그, 디지털, 믹스드 시그널 및 RF 디자인을 시각적으로 표현하고 캡처할 수 있습니다.

소개

Gateway는 직관적인 편집 기능, 복잡한 대규모 계층 디자인 또는 플랫 디자인 지원, 기존 넷리스트의 심볼 자동 생성, 업계 표준 넷리스트 및 인터페이스 형식에 대한 지원 등을 갖춘 생산적인 환경입니다.

Gateway는 다음과 같은 툴에 대한 인터페이스로 디자인 캡처, 시뮬레이션, 레이아웃 및 검증에 필요한 다양한 뷰를 생성합니다. 이는 SmartSpice, Silos, SmartView 파형 뷰어, Atlas, Victory Device, Expert, SmartDRC/LVS를 포함합니다.

강력한 스크립트 기능으로 인터페이스를 원하는 대로 바꿀 수 있으며, 개인 또는 설계 팀의 필요에 맞는 전용 기능을 생성할 수 있습니다.

특징

- 계층형 멀티 뷰, 멀티 시트 에디터로 복잡한 대규모 설계 지원

- 와이어, 버스, 버스 분할, 버스 병합 등 효울적인 편집 기능

- 와이어-와이어, 와이어-핀, 명칭에 의한 와이어, 묵시적/전체적 연결 지원

- 파형 디스플레이와 스키매틱 사이의 크로스 프로빙

- 계층을 통한 정보 관찰: 레벨을 통해 신호를 추적

- 전기적 드로잉 규칙 및 넷리스트 위반을 나타내는 규칙 검사를 설정

- 소자 파라미터, DC 바이어스 및 임계값 표시

- IP 보호를 위한 보안 지원

장점

- 직관적이고 편리한 환경을 사용하여 신속한 설계 및 편집

- 넷리스트 형식을 지원하는 가져오기/내보내기 기능을 통해서, 동일한 스키매틱 출처로부터 많은 디자인 플로우와 사용을 지원

- 버스, 인스턴스 및 노드 이름에 대한 이름 지정 기능을 사용하여 대규모 계층 설계 또는 평면 설계를 쉽게 개념화

적용

- 아날로그 및 디지털 블록, 믹스드 시그널, RF, 스탠더드 셀 및 IO

기술 사양

- 지원하는 넷리스트 형식

- SPICE

- CDL

- NDL

- Verilog IEEE 1364

- 지원하는 시뮬레이션 환경

- SmartSpice

- HSPICE®

- Silos

- Device Simulators like Atlas and Victory Device

- OpenAccess, iPDK 지원

- EDIF 2 0 0 을 통해 타사의 스키매틱 툴에 대한 인터페이스 지원

- 자바스크립트를 이용한 고급 스크립트 지원, 200개 이상의 함수를 활용할 수 있으며, 사용자 콜백 심볼에 대한 메뉴 및 GUI의 설정 가능

- 사용자 PDK 및 iPDK에 대한 지원 – 최신 정보는 실바코에 문의

Viso를 활용한 기생 문제의 조사, 분석 및 해결

Si, GaN, SiC 기술에 대한 전력 소자 SPICE 모델링

SmartSpice를 활용하여 최신 TFT 기반 플랫 패널 설계

Utmost IV를 활용한 소자 모델링의 최신 기술

실바코 플로우를 활용한 FPD 및 검출기의 픽셀 어레이 설계 및 시뮬레이션