임베디드 메모리 컴파일러 IP

실바코는 HPC 및 AI 메모리 솔루션 수요에 맞게 업계 최초의 프로세서 속도 캐시 메모리 컴파일러를 제공합니다. 실바코의 초고속 캐시 메모리는 고급 캐시 아키텍처와 로직 룰 비트셀을 특징으로 하는 적응형, 비일관성 캐시 IP입니다. 해당 아키텍처는 시스템 성능, 확장성, 전력 효율성, 데이터 지역성, 애플리케이션 응답성, 비용 최적화에 의한 시장 경쟁력을 제공하여, 독자적인 비즈니스 가치를 제공합니다.

실바코는 또한 고성능, 낮은 소비전력, 고밀도에 맞는 아키텍처로 폭넓은 임베디드 메모리 컴파일러 제품군을 제공하여, 다양한 공정 기술에 대해 탁월한 수율을 제공합니다. 실바코의 솔루션은 설계자가 성능, 전력, 공간 사이에 최적의 조합을 찾을 수 있도록 지원합니다.

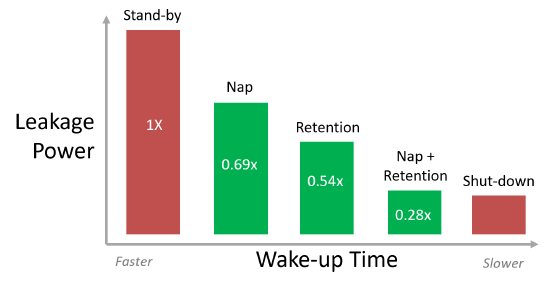

최첨단 전력 관리 기능을 활용하여, 가장 까다로운 낮은 누설 전류, 저전력, 저전압 설계 사양을 충족할 수 있습니다.

Cello와 Viola를 활용하여 Silterra의 스탠더드 셀과 I/O 라이브러리를 최적화

실바코 AMBA AHB 서브시스템과 커스터마이징, 보안, 검증 방법

Cello를 활용하여 FinFET 스탠더드 셀 레이아웃의 복잡도 관리

IoT 시스템용 고급 메모리를 지원하는 실바코의 옥타 SPI 메모리 컨트롤러

실바코의 55LPx Foundation IP 솔루션으로 초저전력 IoT 설계