# **SILVACO**

# **DTCO Integrated Tool Flow**

Single Run Time Environment

### Contents

- Introduction

- Select Cell Layout and Annotate using Rule File

- Clip Layout to Build Active Devices

- Device Simulation and SPICE Model Extraction

- 3D BEOL Structure Creation for RCX Field Solver

- SPICE Simulation within Same Input File

- DTCO Statistical Analysis Environment

- Summary

### Introduction

## DTCO: Connecting Semiconductor Physics to Circuit Design

# Process Simulation Solid Modeling

#### **Victory Process**

- Etch & Deposition

- Epitaxy

- Implantation

- Diffusion/Activation

- Oxidation

- Stress

#### **Victory Mesh**

- Solid Modeling

- Device Meshing

#### **Device Simulation**

#### **Victory Device**

- Drift/Diffusion

- Self-Heating

- Mixed Mode

- Radiation

- Reliability

#### **Victory Atomistic**

- NEGF

- Quantum transport

# Modeling Circuit Simulation & RCx

#### **Utmost IV**

SPICE Model Generation

#### **SmartSpice**

Circuit Simulation

## **Victory RCx Pro**

• 3D Field solver RCx

Model / Circuits to Customer

Design Technology Co-Optimization

Design

(GDSII)

**Process**

Info

©2023 Silvaco, Inc.

### Introduction

- Design Technology Co Optimization (DTCO) improves designs across multiple domains.

- 3D active device and BEOL parasitic extraction builders are now integrated and share the same:

- Layout tool

- Structure builder

- Structure mesh generator

- Rule file

- Simulation interface

- Syntax

- A single input file can now run a full TCAD to SPICE flow, enabling a powerful integrated DTCO environment

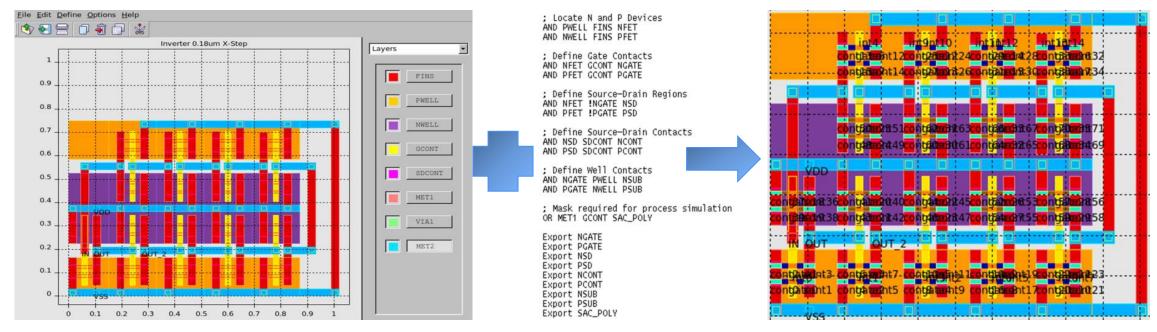

# Select Cell and Annotate using Rule File

- Supplied layout with basic labels (Vss, Vdd, In,

- Layout automatically annotated using the rule file

Example using a ring oscillator circuit

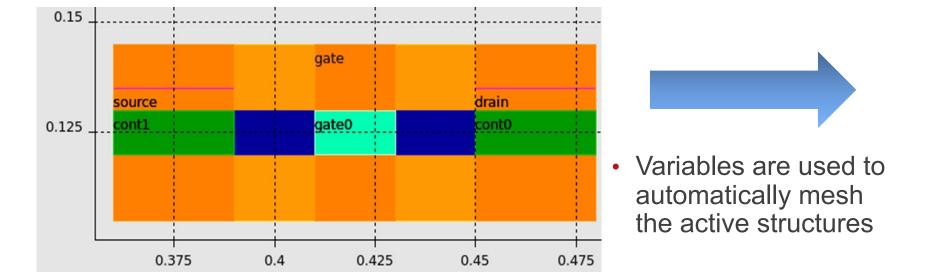

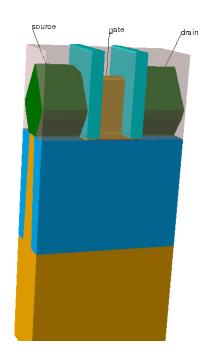

## Clip Layout to Build Active Devices

- From same layout, clip areas to build active devices

- Full Victory Process simulation capability available

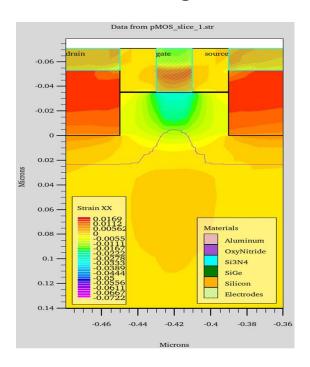

Example of stained SiGe extensions for pMOS

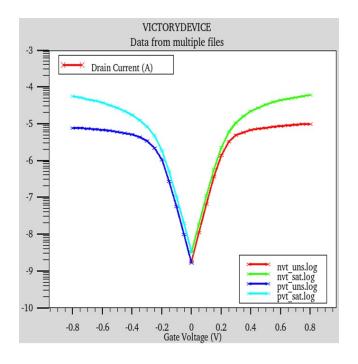

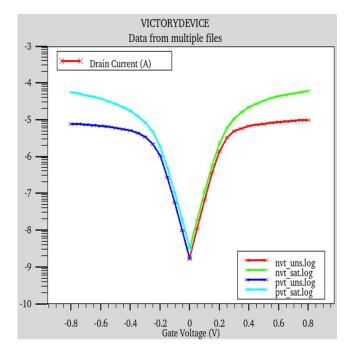

## Device Simulation and SPICE Model Extraction

- Simulate active device I V and capacitance curves

- Automated multi gate SPICE model extraction

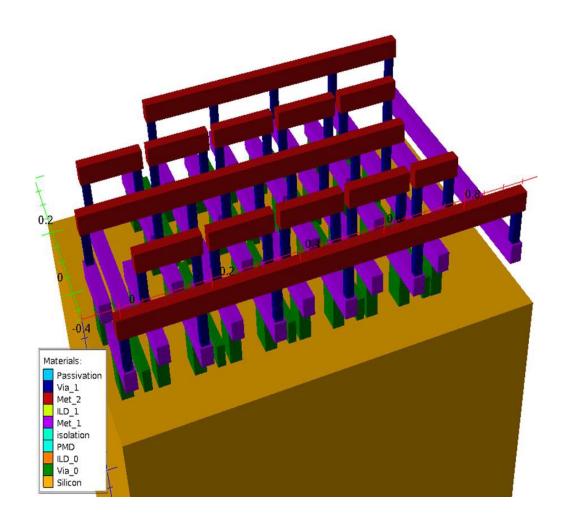

## 3D BEOL Structure for RCX Field Solver

- A Full 3D structure is created for BEOL field solver

- Active device netlist automatically extracted, then

- RC parasitics extracted and automatically back annotated

- Same structure builder/syntax as used for active devices

i

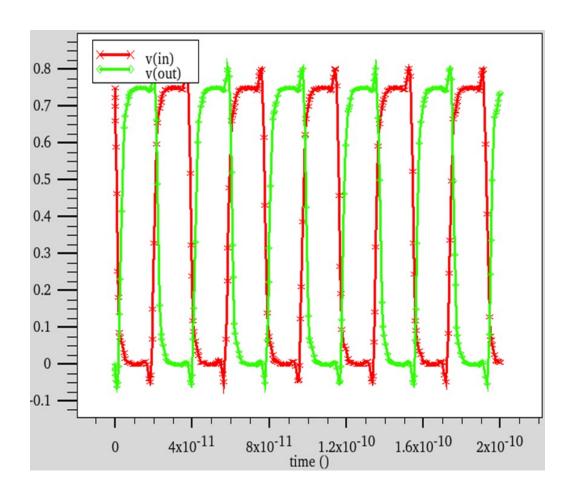

## SPICE Simulation within Same Input File

- Use ".INCLUDE" statement in SPICE to import created netlist

- SPICE simulations run and key performance parameters extracted for full flow optimization

- All run using the same interface and script

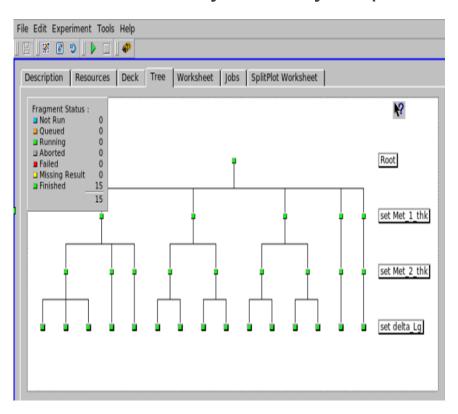

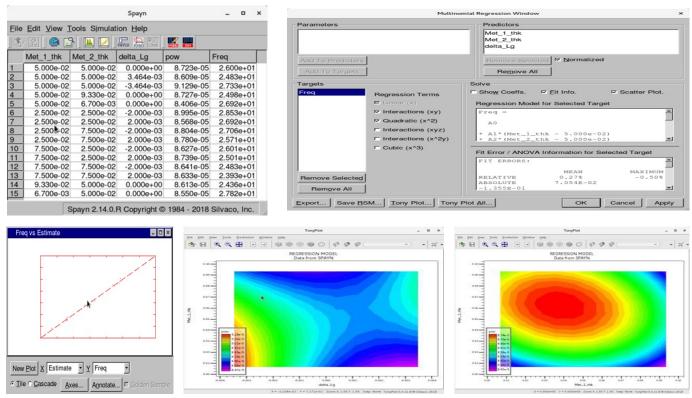

# **DTCO Statistical Analysis Environment**

- Design of Experiments and analysis environment

- Statistical analysis of layout/process/circuit dependencies

10

©2023 Silvaco, Inc.

## Summary

- Single fully integrated run time environment

- Anything can be a variable Layout, Process, BEOL

- Clear actionable results for Design Optimization

- Complete and full TCAD to SPICE simulation capability

- Parameterization models linking all design variables

- Powerful extract statements for parameter extraction

- All tools developed in house for smooth integration

- Worldwide support for your success