#### SILVACO FROM ATOMS TO SYSTEMS

# Parasitic Extraction Clever and Hipex-FS

Integrated Full Chip and Cell Level RCX Combine Rule Based and Field Solver Solutions

Copyright © 2022 Silvaco Inc.

#### Contents

- Introduction

- Simulation Methodologies

- Rule Based

- Generating Parasitic Database

- Field Solver

- Field Solver Methods

- Boundary Element or Finite Element ?

- Combining Both Rule and Field Solver Methods

- Summary

#### Introduction

- Many Solution Methodologies Exist for RCX Extraction

- No One Methodology is Suitable for all Circuit Blocks

- Combine Solution Methods for each Cell or Block

- Common Integrated Platform to Localize User Options

- Consider Intended User Skill Set, CAD versus TCAD

- Consider Size and Topology, versus Simulation Speed

- How Much Accuracy do you Really Need ?

- User Choices are Often Technology Dependent

### **Solution Methodologies**

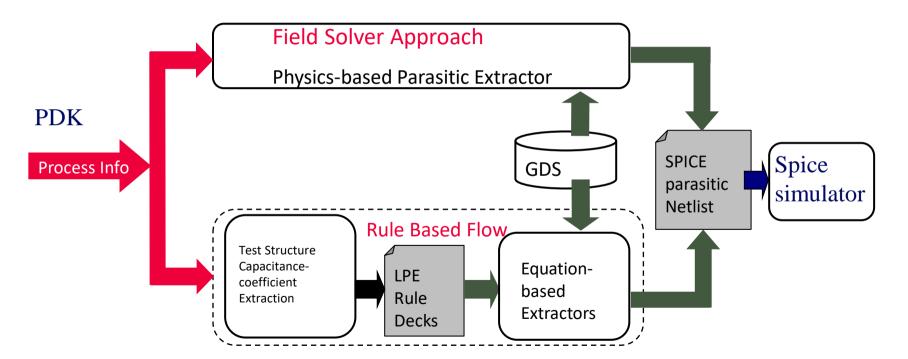

• Rule Based - or - Field Solver Based

### **Rule Based**

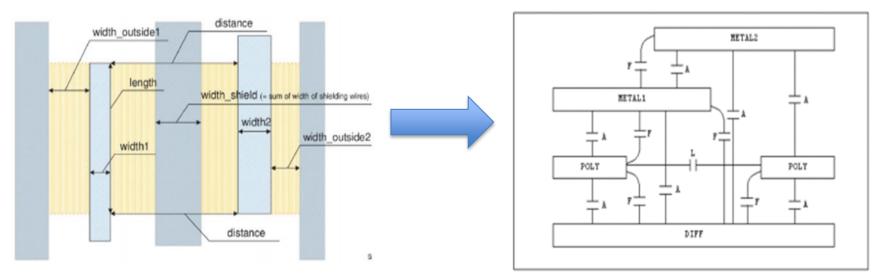

- Capacitance Extract Geometry from layout Polygons

- Resistance Count Conductor Length in "Squares"

- Coefficient Database Converts Polygons into C and R

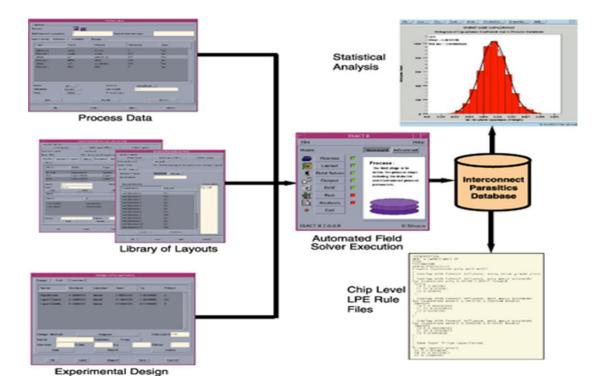

#### **Generating Parasitic Database**

However, generating the large capacitance coefficient database for rule-based extraction, also requires a specific field solver solution, one time per technology

#### **Field Solver Methods**

- Field Solver's have several methods to apply the physics to the Physical Representation of the Structure

- Field Solvers Extract Both Capacitance and Resistance

- Finite Difference and Finite Element Methods are:

- Optimal for Complex and Curved 3D Shapes

- Boundary Element and Random Walk Methods are:

- Optimal for Squared Off Simple "Manhattan" Shapes

- Simulation Speed versus Shape Complexity Trade-off

- Silvaco uses Field Solvers from Both Category Types

## **Boundary Element or Finite Element ?**

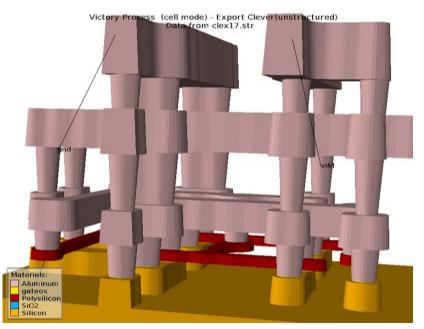

- For Uniform Layer Thickness and Manhattan Shapes

- Boundary Element Method

- For Complex 3D Shapes

- Finite Element Method

- Technology information for field solved sections can be defined in several ways:

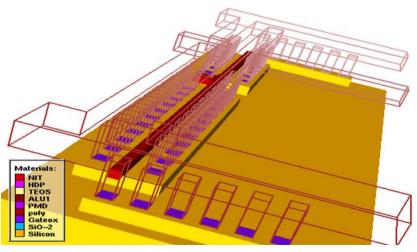

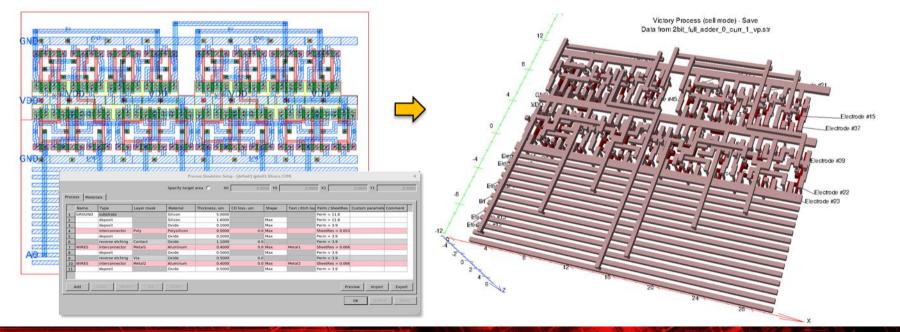

- 1/ Using TCAD tools and syntax (Left)

- 2/ Using a GUI in the Layout Tool (Below)

- 3/ A file provided from the PDK

- Choices for TCAD or CAD Engineers

|    | Name   | Type            | Layer mask | Material    | Thickness, um | CD loss, um | Shape | Text / Etch lay | Perm / SheetRes  | Custom paramete | Comment |

|----|--------|-----------------|------------|-------------|---------------|-------------|-------|-----------------|------------------|-----------------|---------|

| 1  | GROUND | substrate       |            | Silicon     | 5.0000        |             |       |                 | Perm = 11.8      |                 |         |

| 2  | 1      | deposit         |            | Silicon     | 1.6000        |             | Max   |                 | Perm = 11.8      |                 |         |

| 3  | 1      | deposit         |            | Oxide       | 0.1000        |             | Max   |                 | Perm = 3.9       |                 |         |

| 4  |        | interconnector  | Poly       | Polysilicon | 0.5000        | 0.0         | Max   |                 | SheetRes = 0.053 |                 |         |

| 5  |        | deposit         |            | Oxide       | 0.5000        |             | Max   |                 | Perm = 3.9       |                 |         |

| 6  |        | reverse etching | Contact    | Oxide       | 1.1000        | 0.0         |       |                 | Perm = 3.9       |                 |         |

| 7  | WIRES  | interconnector  | Metal1     | Aluminum    | 0.4000        | 0.0         | Max   | Metal1          | SheetRes = 0.066 |                 |         |

| 8  |        | deposit         |            | Oxide       | 0.5000        |             | Max   |                 | Perm = 3.9       |                 |         |

| 9  |        | reverse etching | Via        | Oxide       | 0.5000        | 0.0         |       |                 | Perm = 3.9       |                 |         |

| 10 | WIRES  | interconnector  | Metal2     | Aluminum    | 0.4000        | 0.0         | Max   | Metal2          | SheetRes = 0.066 |                 |         |

| 11 |        | deposit         |            | Oxide       | 0.5000        |             | Max   |                 | Perm = 3.9       |                 |         |

Copyright © 2022 Silvaco Inc.

Technology information plus layout is converted into a true 3D model of the BEOL for Field Solve

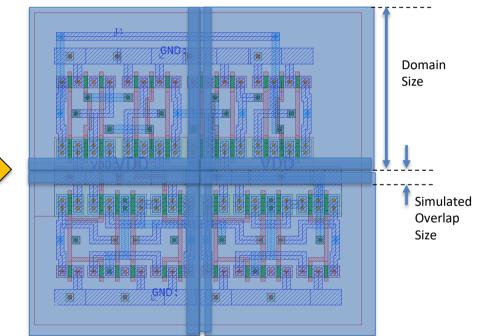

Domain decomposition allows much larger circuit sections to be field solved

• Simulating a larger overlap improves accuracy a little at the expense of simulation speed.

ectode #20 Electode #31

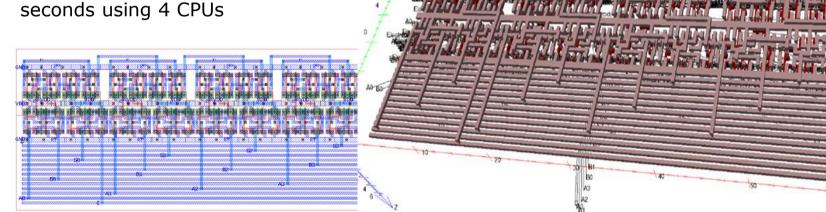

Example of full 4-bit adder below, using boundary element method, simulation time 26 minutes, 41 seconds using 4 CPUs

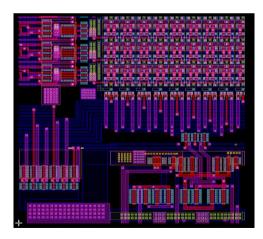

#### True Mix and Match Capability in One Tool

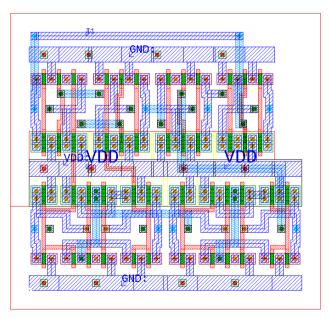

User selects which section of the layout is solved using finite element or boundary element field solvers, with the remainder using traditional rule-based extraction

| Parasitic Extraction (Capacitance)                                                                      |                                                  | Stellar    |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|

| Field Solver c Stellar c Clever 	☐ Include.dummy net                                                    |                                                  |            |

| Clever version 3.11.26.R IF Clever Clever version                                                       | ever processor number: 2 🚔 (Max=36)              |            |

| c Stripes<br>Stripe width (um) 300<br>Vicinity width (um) 100                                           |                                                  |            |

| Mix-and-Match (Block dimensions / So     MinX MinY MaxX MaxY Over     100.000 420.000 566.000 460.000 4 | ver type and options / Decomposition parameters) | Rule-basec |

#### Summary

- Rule Based Extraction Use for Most of the Full Chip

- Field Solver Extraction Complex R and C Topology

- Where Highest Accuracy is Required for Critical Cells

- Mix and Match Techniques within One Design

Typical Maximum Cell Size illustration for using Field Solve Techniques