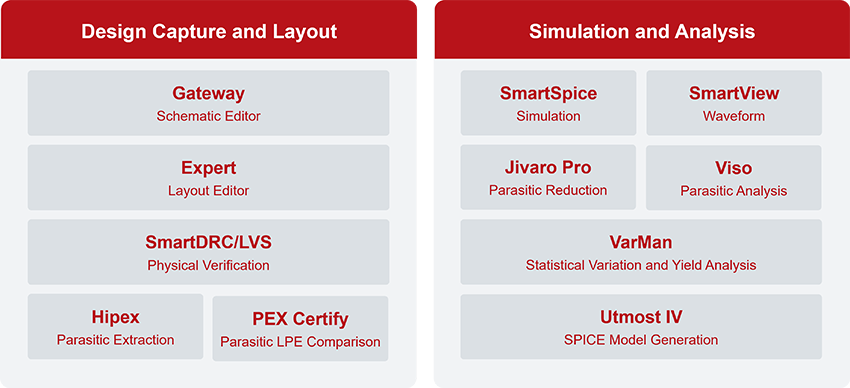

Full Analog IC-CAD Design Flow

Silvaco offers a full IC-CAD design flow including design capture, circuit simulation, layout design, physical verification, parasitic extraction and reduction, and post-layout analysis including statistical variation, and yield analysis.

Schematic Editor

Layout Editor

Physical Verification

Parasitic Extraction

Circuit Simulation

Waveform Analyzer

Parasitic Reduction

Parasitic Analyzer and Debugger

Statistical Variation and Yield Analysis

Device Characterization and SPICE Modeling

Parasitic Extraction Comparison

Schematic Editor

Gateway is a highly productive environment with intuitive editing, capacity to support large and complex hierarchical or flat designs, ability to automatically generate symbols from existing legacy netlists and support for industry standard netlist and interface formats. It features tight integrations to Silvaco TCAD and analog custom design tools.

Layout Editor

Expert is a hierarchical IC layout editor featuring high capacity and flexible use across many silicon technologies in analog, mixed-signal, RF and digital circuits. As a key part of Silvaco’s custom IC design suite, Expert is seamlessly integrated with Gateway schematic design and SmartDRC/LVS physical verification environments. Links to Calibre® RealTime provide sign-off quality DRC interactively and on demand. Expert’s intuitive interface, easy setup and interactive rule checking enable designers to quickly produce correct layouts resulting in fast tapeouts.

DRC/LVS Physical Verification

SmartDRC/LVS performs physical verification of analog, digital and mixed-signal ICs including design rule checks (DRC), layout connectivity extraction and layout vs schematic (LVS) comparison. Its unique architecture delivers high performance and capacity using multiple CPUs, accurate processing of complex shapes, and exceptional user productivity with fast interactive verification and intuitive debug.

Full-Chip Parasitic Extraction

Hipex provides an accurate and fast solution for the extraction of parasitic capacitance and resistance from hierarchical layouts of analog, mixed-signal, memory IC and SoC designs. As part of Silvaco’s complete Physical IC design Verification flow, it is tightly integrated with Expert layout editor for DRC/LVS and RC parasitic extraction. It supports both fast pattern matching and field-solver solver modes.

Circuit Simulation

SmartSpice is a high-performance parallel SPICE simulator that provides a complete set of active device models, Verilog-A compact modeling, and tight integration with the schematic, layout and TCAD analysis tools. It is a proven, comprehensive solution for applications including simulation of complex high precision analog and mixed-signal circuits, memory, custom digital design and characterizing cell libraries of advanced semiconductor processes.

Parasitic Reduction

Jivaro Pro has been adopted by leading IDM and fabless companies worldwide to address the increasing challenges of managing the time and resource challenges of post-layout simulations. Jivaro Pro applies patented mathematical approaches of parasitic reduction to reduce circuit complexity while maintaining accuracy.

Parasitic Analysis

Viso facilitates a rapid and comprehensive understanding of parasitic effects that can impact the performance goals of your design. Through robust analyses, Viso addresses various issues such as crosstalk effects, signal weaknesses, unbalanced net symmetries, delays degradation, IR drop problems, and more.

Parasitic Extraction Comparison

PEX Certify, composed of PEX Diff and PEX Link, is designed to compare large, extracted netlists to qualify and quantify differences. PEX Certify can very quickly determine if two extracted netlists correspond using statistics and sophisticated analysis of the parasitics without running long-lasting circuit simulations.

Variation and Yield Analysis

VarMan is a comprehensive suite of analysis tools that allow designers to accurately address statistical variations and to make the right implementation decision upfront. VarMan is a new-generation tool that employs machine-learning technology and provides efficient and reliable solutions for analog, RF, standard cells, IO, and memory designs.

SPICE Model Generation

Utmost IV is the industry’s premier solution to address these challenges for the characterization and modeling of cutting-edge CMOS and compound semiconductor devices. It provides an easy-to-use, database-driven environment for the characterization of semiconductor devices and the generation of accurate, high-quality SPICE models, macro-models and Verilog-A models for analog, mixed-signal and RF applications.

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors