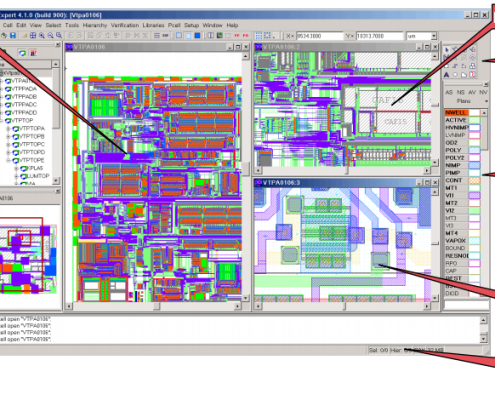

Expert Layout Editor

Silvaco’s Expert is a hierarchical IC layout editor featuring high capacity and flexible use across many silicon technologies in analog, mixed-signal, RF and digital circuits. As a key part of Silvaco’s custom IC design suite, Expert is seamlessly integrated with Gateway schematic design and SmartDRC/LVS physical verification environments. Links to Calibre RealTime provide sign-off quality DRC interactively and on demand. Expert’s intuitive interface, easy setup and interactive rule checking enable designers to quickly produce correct layouts resulting in fast tapeouts.

Introduction

Key challenges for circuit designers today include complex and changing IC technology requirements, the increasing number of design rules that must be verified and corrected, exploding design databases and always tight schedules.

Silvaco’s Expert Custom IC was developed to deliver the flexibility, productivity and performance, to meet these growing challenges. Its configurability and all-angle features make it suitable for wide range of IC technology requirements including CMOS, BiCMOS, GaAs and many others. Industry standard design formats are supported, and many process design kits (PDKs) are available, including popular iPDKs (interoperable PDKs). It is easy to install and technology file setup is facilitated by importing existing Virtuoso information, when available.

Expert’s database architecture provides extremely fast loading, viewing and editing operations for multimillion+ transistor designs – even on basic workstations. Multi-window hierarchical editing, multi-user capabilities and powerful scripting and API speed design team productivity.

Integrations with Silvaco and 3rd party tools reduce design time by enabling real-time interactive DRC, error viewing and rapid corrections to be made to the layout.

Features

- Customizable GUI, scripting and multi-user, shared library environment

- Edit in place, exploded view and flattened data

- DRC assist allows designer to enable checking of certain design rules during editing operations; errors can be displayed and interactively corrected

- Expert Node Probing offers node highlighting for connectivity visualization. It highlights all layout objects electrically connected with the object you click

- Netlist driven layout and parameterized cells (Pcells) generation using JavaScript or LISA scripting language

- Any angle rules for accurate measurement

- Tight integration with Gateway schematic editor to allow cross probing between logic design and physical design

- Extensive custom set of PDKs plus support for iPDK

- Performs Layout Vs Layout Verification (LVL)

- Integrated with Calibre Interactive and Calibre RVE for physical verification

- Netlist driven layout (NDL) improves turnaround time (TAT) of layout design

- Equal resistance routing for TFT and Flat panel use

- Encryption is available to protect valuable customer and third party intellectual property

- Integrated with Silvaco’s verification suite SmartDRC/LVS (DRC/LVS/NET) and parasitic extraction tool Hipex

- Tightly integrated with Silvaco’s field solver- based 3D RC extraction tool Victory RCx Pro

Benefits

- Highly productive layout environment due to intuitive and powerful editing capabilities, interactive DRC and error viewing

- Fast GDSII file loading, editing and viewing of extremely large databases

- Flexibility and configurability to use on many types of silicon technology

Applications

- Analog, Digital, mixed-signal and RF

Technical Specifications

- Input/output formats supported: GDSII, LEF/DEF, DXF, OASIS, CIF, Applicon, Open Access databases, .eld, .sld

- OpenAccess iPDK support

- Scripting Support: JavaScript, Lisa

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors