SmartSpice Circuit Simulator

Silvaco’s SmartSpice™ is a high performance parallel SPICE simulator that delivers industry leading accuracy. It is a proven, comprehensive solution for applications including simulation of complex high precision analog and mixed-signal circuits, memory, custom digital design and characterizing cell libraries of advanced semiconductor processes.

Silvaco’s SmartSpice uses an intelligent architecture deploying multiple solvers, stepping algorithms and computation techniques. The result is accurate, robust convergence and industry leading performance and capacity – over 8 million active devices. It is HSPICE® and Spectre® compatible and supports calibrated SPICE models for advanced technologies (TFT, OTFT, SOI, HBT, FRAM, FinFET, etc.). Integrated with Silvaco Gateway schematic editor and SmartView waveform viewer, SmartSpice fits seamlessly into front-end analog IC design flows. It supports mutli-threaded parallel simulation and distributed multi-processing across network CPUs for accelerated analysis.

Applications

- Analog, mixed-signal

- Memory design

- FPD design

- Custom digital

- Library Characterization

Real-time Circuit Simulation Rubberband Capability

With the rubberband feature of SmartSpice and Gateway, analog design improvement is made easy. Changing values of models or device instance parameters in any combination provides realtime feedback on the change in circuit performance through the rubberband capability.

Native Optimization

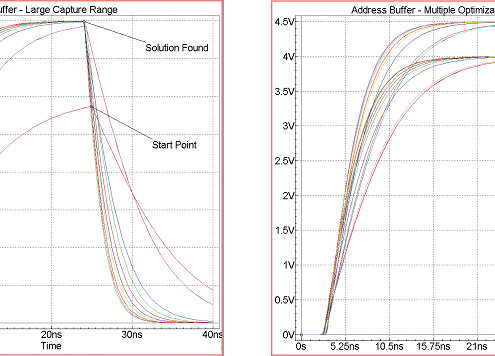

SmartSpice performs parametric optimization of circuits. The optimizer provides a comprehensive interface and an interactive display system for visualizing the optimization process as it is executed. It supports both performance measure and function curve optimization.

Performance Measure Optimization

- Values and parameters of circuit components are automatically altered so that individual electrical characteristics meet specifications.

- Optimizer can fine-tune delay, rise/fall times, trip point, maximum and minimum current, and any other circuit performance measurement that can be calculated by a SmartSpice .MEASURE statement.

- Simultaneous multi-target optimization of several performance measures is supported

Function Curve Optimization

- Function curve optimization matches calculated curves with desired curves for DC, AC, and transient analyses. The desired curves can represent the results of TCAD simulations or physical measurement.

- There are no restrictions on the type of circuit analysis that can be performed. Circuits can be optimized in steady state, frequency, and time domain

Verilog-A Language Environment

The Verilog-A modeling extension language for SmartSpice provides circuit designers and model developers with an easy-to-use, comprehensive environment for the design and verification of complex analog and mixed-signal circuits and models. The environment supports top-down design and bottom-up verification of analog and mixed-signal designs via behavioral modeling. Compilation and encryption of Verilog-A source source code allows distribution of proprietary models and analog IP without source disclosure.

Key Features

- Integrated debugger and development environment accelerates compact behavioral model development

- Compatible with all analog features of the Verilog-AMS 2.3.1 language specification

- Implements small-signal and noise sources in multiple distributions (Gaussian, exponential, Poisson, chi-square, Student’s T, and Erlang)

- Executes analog operators, including time integral/derivative, partial derivative, transition, slew, Laplace transform and Z-transform

- Enables analog designers to build executables for designs of phase-locked loops, VCOs, A/D, D/A, etc. for prototyping purposes before detailed circuit design

- Allows designers to describe digital components for mixed-signal designs such as Sigma-Delta converters

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors