Embedded Memory Compiler IP

Silvaco offers an industry-first processor speed cache memory compiler to meet the demands of HPC and AI memory solutions. Silvaco’s Ultra High-Speed cache memory is an adaptable, non-coherent cache Intellectual Property (IP) featuring an advanced cache architecture and logic rules bitcell. This architecture enhances system performance, scalability, power efficiency, data locality, application responsiveness, cost optimization, and market competitiveness, providing a distinctive business value.

Silvaco also offers an extensive array of Embedded Memory Compilers with architectures tailored for high performance, low power consumption, and high density, while delivering robust yield across diverse process technologies. Our solutions empower designers to strike the right balance between performance, power efficiency, and spatial considerations.

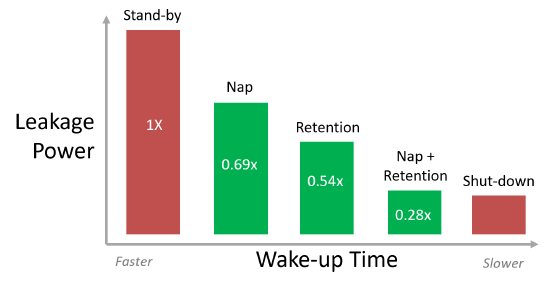

Leveraging cutting-edge power management features, our memory compilers can accommodate the most challenging low-power, low-leakage, and low voltage design specifications.

Learn How SilTerra Uses Cello and Viola for Standard Cells and I/O Library Optimization and Characterization

Learn About Silvaco’s AMBA AHB Subsystems and How to Customize, Secure, and Verify

Managing the Complexity of FinFET Standard Cell Layout with Cello

Designing with Silvaco’s Octal SPI Memory Controller with Advanced Memory Support for IoT Systems

Achieving Extreme Low Power IoT Designs with Silvaco’s 55LPx Foundation IP Solution