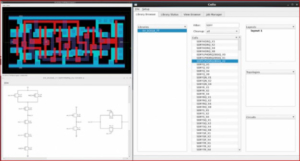

Learn How SilTerra Uses Cello and Viola for Standard Cells and I/O Library Optimization and Characterization

As an active semiconductor foundry, SilTerra requires frequent process and technology development and enhancements, which can result in an increased need for resources and longer time to market. To meet this ongoing challenge, high productivity library optimization and validation are required.

As an active semiconductor foundry, SilTerra requires frequent process and technology development and enhancements, which can result in an increased need for resources and longer time to market. To meet this ongoing challenge, high productivity library optimization and validation are required.

In this webinar, we will share the challenges of developing, optimizing, and validating different libraries, and demonstrate how Cello, Viola, and SmartSpice contribute in a unique and dynamic way to realize fast and accurate results. We also show how using Cello and Viola ultimately result in a significant reduction in library development and validation time, even with limited manpower and resources.

What You Will Learn

- The challenges of library optimization and validation

- How Cello and Viola reduce development time and manpower requirements

- How to optimize library characterization and validation

- How to increase productivity without increasing resource requirements

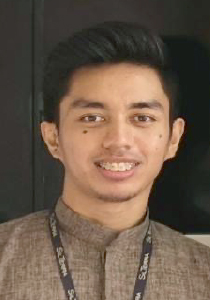

Presenter

Mr. Faris Amsyar Bin Ahmad Zhaki, IP Staff Engineer, SilTerra Malaysia Sdn. Bhd

Mr. Faris Amsyar Bin Ahmad Zhaki, IP Staff Engineer, SilTerra Malaysia Sdn. Bhd

Mr. Faris Amsyar Bin Ahmad Zhaki is an IP Staff Engineer with SilTerra focusing on Standard Cell and I/O library development and silicon validation for over five years. Mr. Faris Amsyar Bin Ahmad Zhaki holds a Bachelor of Electronics Engineering from University of Science, Malaysia.

WHO SHOULD ATTEND:

Semiconductor device, IP, Circuit, CAD, SoC, and system design engineers, product managers, and engineering management.

When: February 16, 2023

Where: Online

Time: 10:00am-10:30am-(PST)

Language: English