Hipex:基于规则的全芯片RC寄生提取

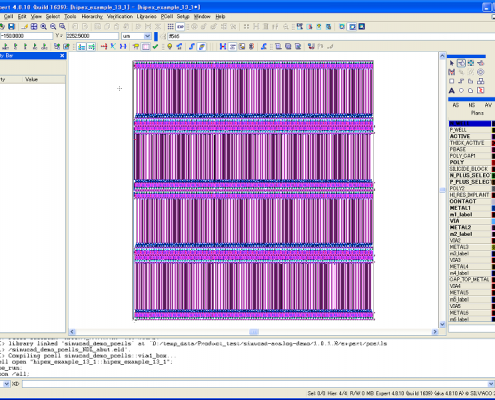

Hipex RC为从模拟、混合信号、存储器IC和SoC设计的层次化版图中提取寄生电容和电阻提供了一个准确、快速的解决方案。作为Silvaco完整模拟定制设计流程的一部分,RC寄生提取与DRC/LVs与Expert版图编辑器紧密集成。

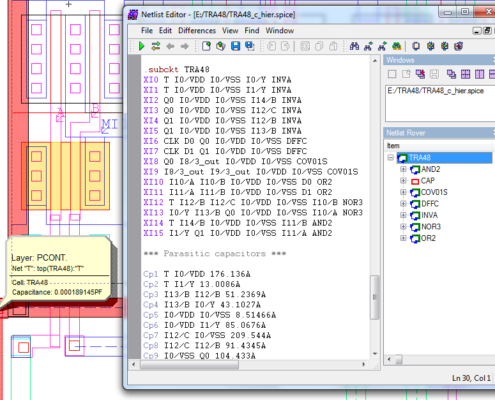

Hipex RC根据GDSII、单元网表和工艺规则技术文件,对整个芯片或选定的网络或节点执行寄生提取,然后用提取的寄生对原理图网表进行反标。

Hipex RC的器件提取功能允许生成保留原始版图的层次结构的分层网表,并支持广泛的标准和参数化用户定义的器件。此外,它还进行短路、开路和悬挂的电气规则检查(ERC)。

Hipex RC为高效并行的多处理器服务器构建,对于大型全芯片设计,它具有显著高效的内存利用率。

功能特性

- 具有快速2D提取器的性能来完成接近3D精度的电容计算

- 快速分析用户选择的关键网络或层,无需提取整个芯片

- 支持集中RC、仅C、仅R、耦合C和完全分布式RC提取

- 使用原理图节点名称、寄生电阻和电容对提取的网表进行反标

- 精确提取非45度和非90度器件及任意形状电阻器的器件

- 以P2P格式提供寄生RC提取,支持计算每根走线上的总电容和点对点的电阻

如何使用 Viso 检查、分析和解决复杂的寄生问题

Si、GaN和SiC功率器件的SPICE建模

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors