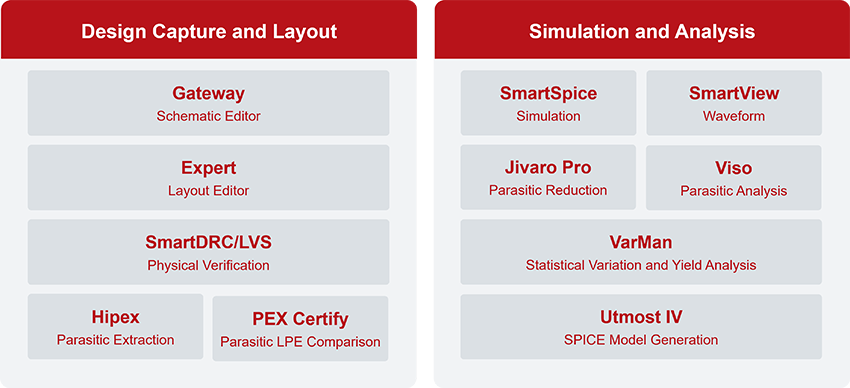

模拟 IC-CAD 设计全流程

Silvaco提供一套完整的IC-CAD设计流程,包括电路原理图编辑、电路仿真、版图设计、物理验证、寄生提取和缩减,以及版图后分析如偏差和良率分析。

Gateway:电路编辑

Expert:版图编辑

SmartDRC/LVS:物理验证

Hipex:寄生提取

SmartSpice:电路仿真

SmartView:波形分析

Jivaro Pro:寄生参数缩减

Viso:寄生分析与调试

VarMan:统计偏差与良率分析

Utmost IV:器件特征化与SPICE建模

PEX Certify:寄生参数提取比较

电路编辑器

Gateway 提供一个高效的环境,具有直观的编辑功能,能够支持大型复杂的层次化或平面设计,能够从现有的网表中自动生成符号,并支持行业标准的网表和接口格式。它与Silvaco TCAD和模拟定制设计工具紧密集成。

版图编辑

Expert 是一款层次化IC版图编辑器,容量大、用途灵活,可用于模拟、混合信号、射频和数字电路等的多种硅基工艺技术。作为Silvaco定制IC设计套件的关键部分,Expert与Gateway原理图设计和SmartDRC/LVS物理验证环境无缝集成。可以调用Calibre®,提供实时交互式的、Sign-off级的高质量DRC验证。Expert的界面直观、设置简单,具有交互式规则检查,能够帮助设计师快速生成正确的版图,从而实现快速的流片。

DRC/LVS 物理验证

SmartDRC/LVS 执行模拟、数字和混合信号IC的物理验证,包括设计规则检查(DRC)、版图连接性提取和版图与原理图(LVS)比较。其独特的体系结构使用多个CPU提供高性能和高容量,精确处理复杂形状,并通过快速交互验证和直观调试实现卓越的用户高效性。

全芯片寄生提取

Hipex 为从模拟、混合信号、存储器IC和SoC设计的层次化版图中提取寄生电容和电阻提供了一个高精度、快速的解决方案。作为Silvaco完整的物理IC设计验证流程的一部分,它与版图编辑器Expert集成在一起,执行DRC/LVS和RC寄生提取。它支持快速图形匹配和场解析器模式。

电路仿真

SmartSpice 是一款高性能并行SPICE仿真器,它支持一整套有源器件模型、Verilog-A紧凑模型,与原理图、版图和TCAD分析工具紧密集成。它是一个经过验证的完整解决方案,适用于复杂的高精度模拟和混合信号电路的模拟、存储器、定制数字设计以及先进半导体工艺的单元库特征化。

寄生参数缩减

Jivaro Pro 已被全球多家领先的IDM和半导体设计公司采用,以解决后版图仿真中日益增加的时间和资源问题。Jivaro Pro使用了专利的寄生缩减数学方法,在降低电路复杂性的同时,还能保持电路的准确性。

寄生分析

Viso 用于帮助用户快速全面地理解可能影响设计性能目标的寄生效应。通过强大的分析功能,Viso能够解决串扰效应、信号弱点、不平衡的网络对称性、延迟退化和IR降压问题等多种问题。

寄生参数提取比较

PEX Certify 由PEX Diff和PEX Link组成,用于对比大型提取网表并分析和量化差异。通过使用统计和对寄生效应的复杂分析,PEX Certify能够快速判断两个提取网表是否相符,而无需进行耗时的电路仿真。

偏差与良率分析

VarMan 是一套全面的分析工具,支持设计工程师准确地考虑工艺的统计偏差,并提前做出正确的实施决策。VarMan是新一代工具,它使用机器学习技术,为模拟、射频、标准单元、IO和存储体设计提供高效可靠的解决方案。

SPICE 模型提取

Utmost IV 是业界解决前沿CMOS和化合物半导体器件表征和建模挑战的主要解决方案。它提供了一个易于使用、数据库驱动的环境,用于描述半导体器件的特性,并为模拟、混合信号和射频应用生成准确、高质量的SPICE模型、宏模型和Verilog-A模型。

如何使用 Viso 检查、分析和解决复杂的寄生问题

Si、GaN和SiC功率器件的SPICE建模

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors