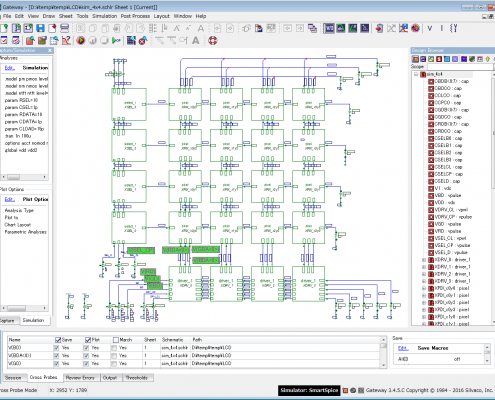

Gateway:电路图编辑

Gateway是一款层次化原理图编辑器,它提供了一个易于使用且功能丰富的环境,支持可视化的方式编辑模拟、数字、混合信号和射频设计。

概述

Gateway提供高效、直观的编辑环境,支持大型复杂的层次化或扁平设计,能够从现有的传统网表中自动生成符号,并支持行业标准的网表和接口格式。

Gateway为设计捕获、模拟、版图和验证创建多个视图,并与现行多种工具设有接口。其中包括SmartSpice、Silos、SmartView波形查看器、Atlas、Victory Device、Expert和SmartDRC/LVS。

强大的脚本功能使用户能够自定义界面并创建专用功能,以满足个人和设计团队的需求。

功能特性

- 层次化的多视图、多页编辑器支持大型和高度复杂的设计

- Edit-In-Place功能支持导线、总线、总线剥离和总线合并

- 线对线、线对引脚、按名称布线和隐式/全局连接

- 通过显示波形和原理图,交叉验证电路设计的可靠性

- 通过层次结构查看信息:由通孔跟踪信号的能力

- 可通过配置规则来检查电路绘制规则和网表之间的差异

- 器件参数、直流偏置和阈值显示

- 加密以保护知识产权

优势

- 使用直观易用的环境快速创建和编辑设计

- 灵活支持来自同一原理图源的多种设计流程和使用,导入/导出支持多种网表格式

- 利用总线、例化和节点名称的高级命名功能,轻松概念化大型层次化或平面设计

应用

- 模拟和数字模块、混合信号、射频、标准单元和IO等

技术规格

- 支持的网表格式:

- SPICE

- CDL

- NDL

- Verilog IEEE 1364

- 支持的仿真环境:

- SmartSpice

- HSPICE®

- Silos

- 器件仿真器,如Atlas和Victory Device

- 支持OpenAccess和iPDK

- 可以通过EDIF 200接口接入第三方电路设计工具

- 使用JavaScript的高级脚本功能可将模块扩展到200个,支持自定义菜单、自定义GUI和用户回调符号

- 如果您需要关于定制PDK或者iPDK的更多服务或最新消息,请联系:sales@silvaco.com。

如何使用 Viso 检查、分析和解决复杂的寄生问题

Si、GaN和SiC功率器件的SPICE建模

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors