Jivaro Pro – Parasitic Reduction

Turbocharge Your SPICE Simulations for Lightning-Fast Results

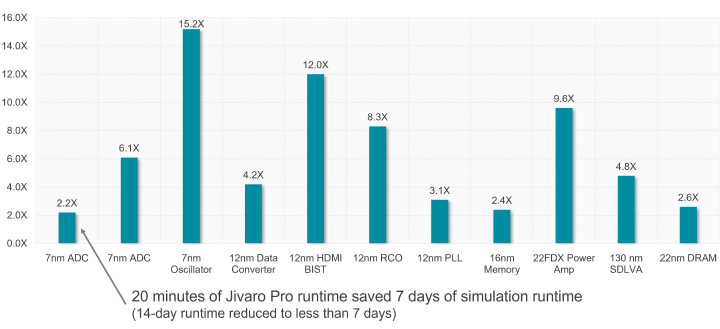

Leading IDM and fabless companies worldwide have adopted Jivaro Pro to address the increasing challenges of managing the time and resource challenges of post-layout simulations. Jivaro Pro applies patented mathematical approaches of parasitic reduction to reduce circuit complexity while maintaining accuracy.

Jivaro Pro SPICE Acceleration

Jivaro Pro Overview

Customer Experience

Harry Chan, CEO, eTopus

For technology nodes from 65nm down to 2nm, Jivaro Pro is independent of the extraction and simulation tools and plugs directly into any design flow. In contrast to rules-based and embedded reduction methods, Jivaro Pro allows designers unparalleled flexibility in managing the tradeoff between accuracy and reduction. For ease of use, Jivaro Pro provides an automatic mode capability that adapts to your design. There are also over 30 adjustable parameters to enable broad control over speed and accuracy of results.

With Jivaro Pro, the designer is in complete control, allowing complete adaptability to the flow and the type of designs or challenges, providing a single solution for all use cases.

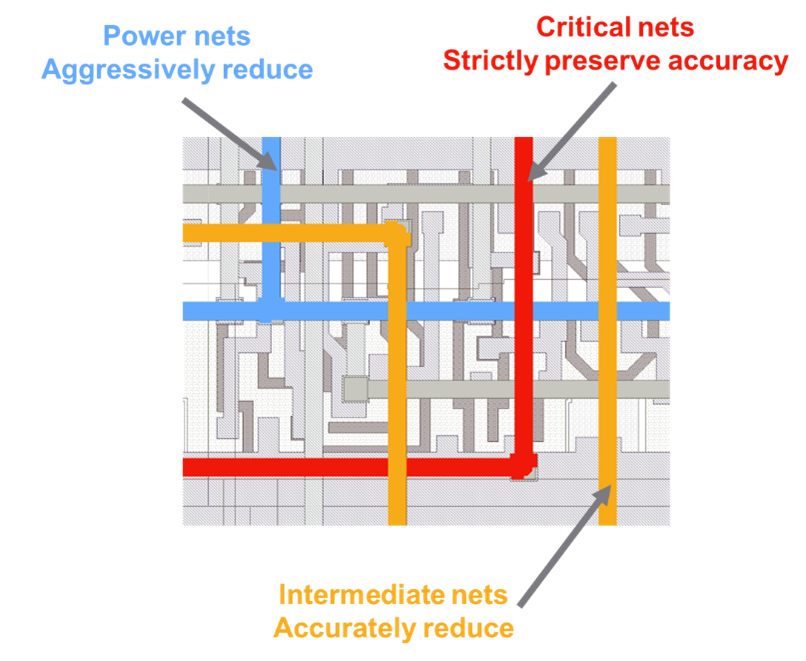

Targeted Reduction – Block or Net

Benefits

- Up to 15X post-layout SPICE simulation speedup

- Easy plug-n-play into existing flows

- Enables running the largest or previously impossible simulations

- Include power nets and metal fills in simulations for greater accuracy

- Customizable parasitic reduction strategies to meet your objectives

- Increase coverage via more simulations

- Minimize compute resources (i.e., CPU and Memory configuration)

Features

- Accepts R, RC, RCC, RLC, RLCK, controlled sources

- Supports DSPF, SPEF, SPICE3, HSPICE®, SPECTRE®, Calibre® View, OA databases

- Reduces temperature-dependent parasitic networks and multi-corner extracted netlists

- Reduction can be applied selectively on nets, sub-circuits or paths within the hierarchy

- Intuitive GUI for configuration and analysis

- Jivaro Pro is compatible with all major EDA tools