Overview

In nanometer design nodes parasitic effects play a crucial role and substantially impact the behavior of circuit design. These advanced technology nodes need better accuracy.

Silvaco’s tools for extracted netlist analysis and reduction combine performance, speed and accuracy. We offer a comprehensive suite of analysis tools to speed up the overall post-layout verification flow for analog, digital, RF, mixed-signal and memory design.

Jivaro Pro is a unique stand-alone solution dedicated to the reduction of parasitic networks. It helps back-end verification teams speed up post-layout SPICE simulation of huge extracted parasitic circuits, while keeping high accuracy.

Viso analyzes the electrical properties of RC parasitic networks which crucially impact circuit behavior in nanometer processes. These impacts affect circuit gain, delay, maximum clock rate, cross-coupling, level of ESD protection and other features, which can cripple a design. Viso’s parasitics-focused approach enables quick analysis of interconnect in order to pinpoint problems. It provides timing estimation and accurate comparison of different extracted netlists.

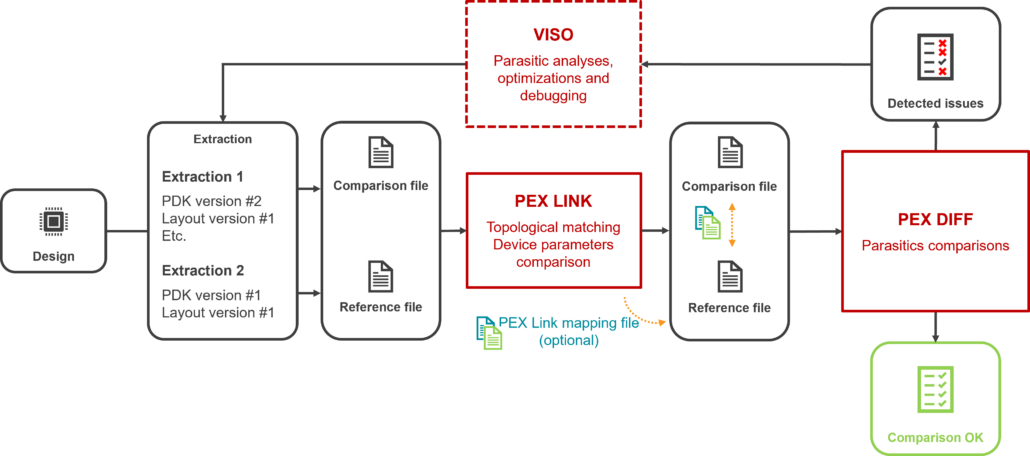

PEX Certify is used for layout comparison via extracted netlist. It compares two different extracted netlists and is mainly used for layout parasitic extraction (LPE) flow qualification.

Parasitic Extraction Analysis and Debug Flow