005_verilog-a_cap : Verilog-A simple Capacitor

Requires: SmartSpice & Smartview

Minimum Versions: SmartSpice 3.6.8.R

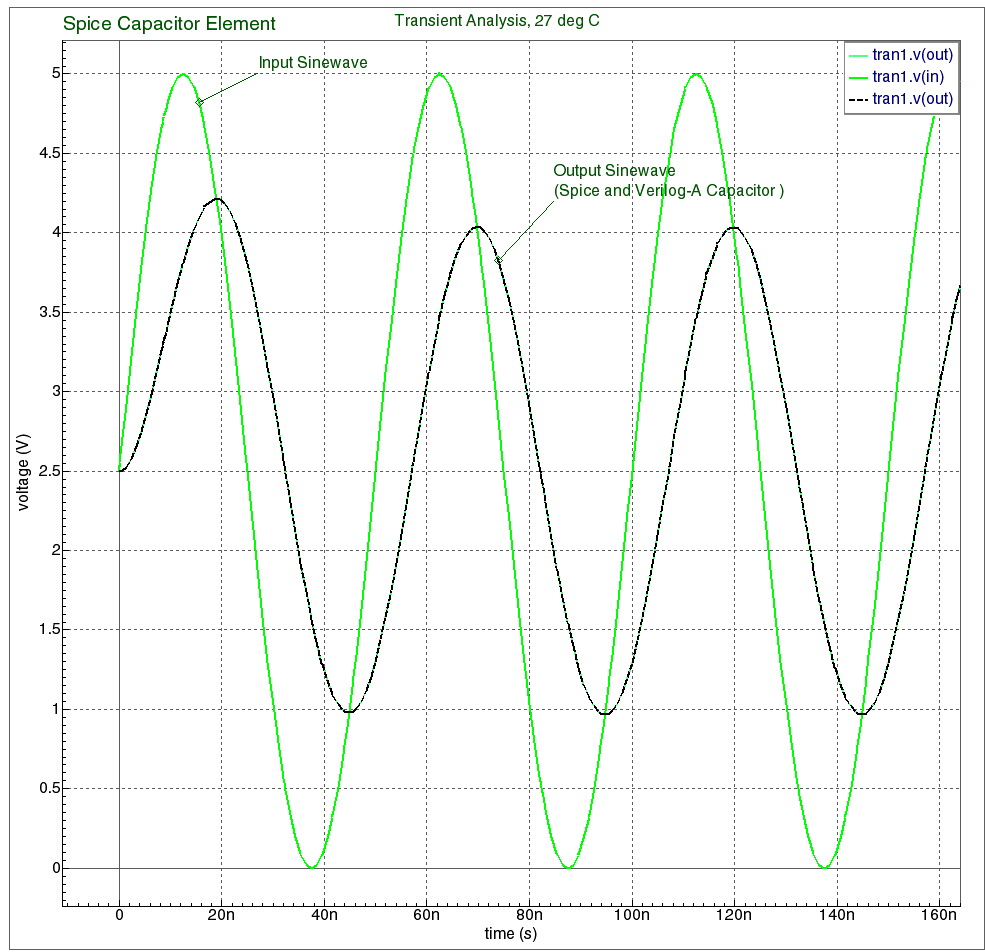

This example shows how to implement a capacitor in Verilog-A and compares the waveform in a simple circuit transient simulation with a native spice element.

The Verilog-A input deck consists of a sinewave voltage source into a series resistor then a parrallel connection of capacitor and resistor to ground. In this case the capacitor element is from a Verilog-A file. A plot shows the input and output simulated waveforms.

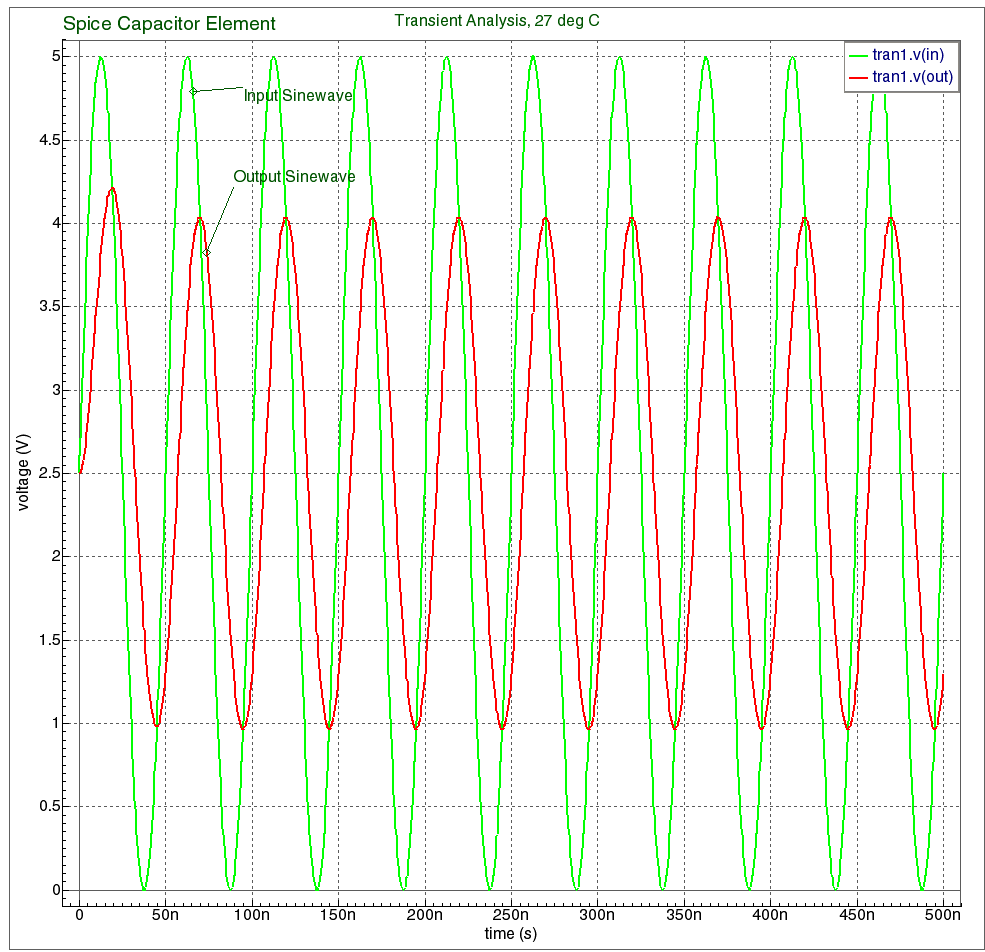

Next the spice input deck which is the same circuit but this time with a standard spice capacitor element can be simulated. This plot shows a similar output waveform.

Comparing the 2 simulation waveforms we can see a good agreement between the 2 inplementations of the capacitor element.

capacitor_deck_va.in

** Capacitor test case .param L= 50e-2 .ic v(out)=0 .hdl "capacitor.va" V1 in 0 sin( 2.5 2.5 20meg) R1 in out 0 5000k R2 out 0 1000k * C1 out 0 1000u * YVLG_capacitor out 0 capacitor L=L .tran 0.1n 0.5u .probe all .end

capacitor.va

//Capacitor

`include "discipline.h"

`include "constants.h"

module capacitor(p, n);

inout p, n;

electrical p, n;

parameter real Q = 1.602176e-19;

parameter real L = 50e-6;

analog

I(p,n) <+ ddt(V(p,n)) * (2e9*Q*L) ;

endmodule

capacitor_deck_se.in

** Capacitor test case .ic v(out)=0 **.verilog "capacitor.va" V1 in 0 sin( 2.5 2.5 20meg) R1 in out 0 5000k R2 out 0 1000k * C1 out 0 1000u * **YVLG_capacitor 0 out capacitor .tran 0.1n 0.5u .probe all .end