Thermal Optimization on GaN HFET Using Flip Chip and Through Wafer via Structures

GaN heterojunction field effect transistors (HFETs) have been under extensive investigation because of their projected superb performances as high-power RF devices. The inherently high breakdown field arising from the wide bandgap guarantees not only the high power input/output characteristics but also extreme device shrinkage which is a huge advantage for increasing the highest operation frequency. Two-dimensional electron gas (2-DEG) with the charge density ten times higher than that of GaAs-based HFET and the mobility well exceeding Si enables a very low on-state resistance indispensable to RF devices. Although the superiority of the device characteristics has been demonstrated, the self heating effect has hindered the production of high power and high speed GaN-based switching devices. This effect can be significantly reduced by the cost effective heat-sink approach (Flip chip or through wafer via)[1,2].

3D Simulation of Ion Enhanced Chemical Etching with VICTORY Process

VICTORY Process is a tool for 3D simulation of the semiconductor industry’s technological processes. It allows stable and accurate modeling of the changes in a structure’s 3D geometry within etching reactors under various conditions. VICTORY Process achieves this by combining a powerful and robust hard-coded numerical engine, based on the Level Set method, with a flexible Open Modeling library which is extendable by users to suit their specific requirements.

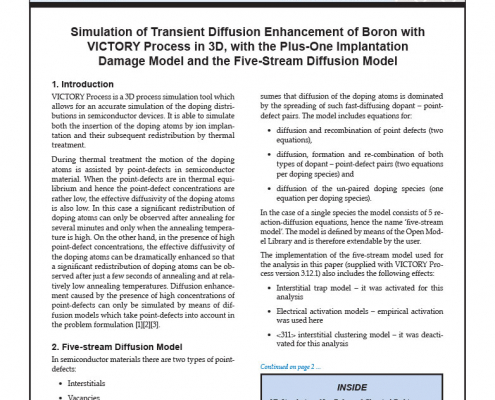

Simulation of Transient Diffusion Enhancement of Boron with VICTORY Process in 3D, with the Plus-One Implantation Damage Model and the Five-Stream Diffusion Model

VICTORY Process is a 3D process simulation tool which allows for an accurate simulation of the doping distributions in semiconductor devices. It is able to simulate both the insertion of the doping atoms by ion implantation and their subsequent redistribution by thermal treatment.

The Studies of Regular Texture Thickness and Finger Pattern of the Front Surface by Using Silvaco TCAD Tools

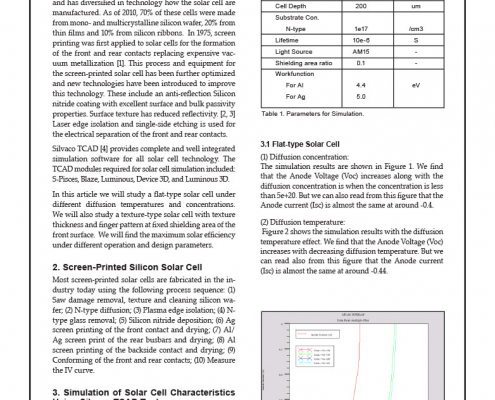

The photovoltaic industry has rapidly grown since 2000 and has diversified in technology how the solar cell are manufactured. As of 2010, 70% of these cells were made from mono- and multicrystalline silicon wafer, 20% from thin films and 10% from silicon ribbons. In 1975, screen printing was first applied to solar cells for the formation of the front and rear contacts replacing expensive vacuum metallization [1]. This process and equipment for the screen-printed solar cell has been further optimized and new technologies have been introduced to improve this technology. These include an anti-reflection Silicon nitride coating with excellent surface and bulk passivity properties. Surface texture has reduced reflectivity. [2, 3] Laser edge isolation and single-side etching is used for the electrical separation of the front and rear contacts.

Extracting Concentrations from Arbitrary Shaped Well Regions

It is often the case when simulating charged coupled devices (CCDs) or image sensors, that a designer wishes to know how many electrons or holes are contained within an arbitrary shaped n or p-well region for a given bias point or after exposure to light for a certain time and intensity.

Simulation of 3D Anisotropic Crystal Etching with VICTORY Process

Anisotropic crystal etching is the common technique used in Micro Electromechanical systems (MEMS) manufacturing. It uses the property of some single crystal materials, like silicon, of having different etching rates in different crystal directions when the material is etched in special chemicals, such as potassium hydroxide (KOH). Predicting the resulting shape of the structure under such conditions requires full three-dimensional simulation of the evolution of the etched surface.

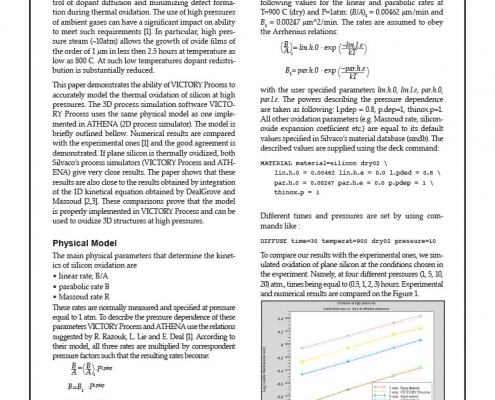

Using VICTORY Process to Simulate Thermal Oxidation of Silicon at High Pressures of Ambient Gases

Developing ULSI silicon technology requires good control of dopant diffusion and minimizing defect formation during thermal oxidation. The use of high pressures of ambient gases can have a significant impact on ability to meet such requirements [1]. In particular, high pressure steam (~10atm) allows the growth of oxide films of the order of 1 μm in less then 2.5 hours at temperature as low as 800 C. At such low temperatures dopant redistribution is substantially reduced.

Hints, Tips, and Solutions – Export 3D Structures from VICTORY Cell/Process to ANSOFT ANSYS

SILVACO provides the tool ANSYSExporter which establishes the link between SILVACO software and ANSOFT ANSYS. ANSYSExporter is fully integrated within the SILVACO environment and can be called by means of a deck statement from DeckBuild or used as a stand-alone tool via command line.

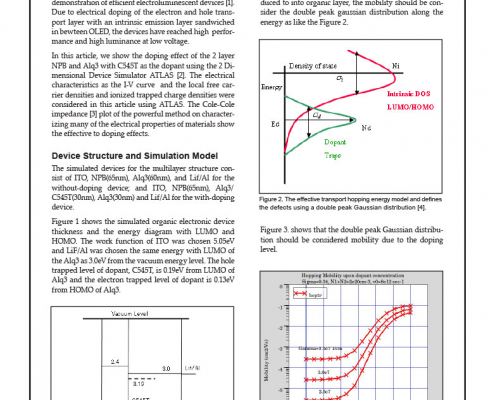

The Doping Effect Simulation on the OLED Devices Using ATLAS

Organic light emitting diodes (OLEDs) have attracted great attention for full-color flat-panel displays since the demonstration of efficient electroluminescent devices [1]. Due to electrical doping of the electron and hole transport layer with an intrinsic emission layer sandwiched in bewteen OLED, the devices have reached high performance and high luminance at low voltage.

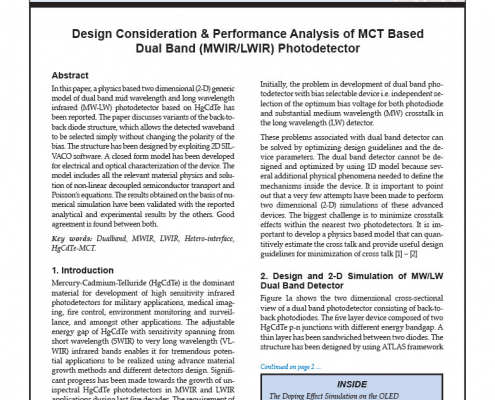

Design Consideration & Performance Analysis of MCT Based Dual Band (MWIR/LWIR) Photodetector

In this paper, a physics based two dimensional (2-D) generic model of dual band mid wavelength and long wavelength infrared (MW-LW) photodetector based on HgCdTe has been reported. The paper discusses variants of the back-to-back diode structure, which allows the detected waveband to be selected simply without changing the polarity of the bias. The structure has been designed by exploiting 2D SILVACO software. A closed form model has been developed for electrical and optical characterization of the device. The model includes all the relevant material physics and solution of non-linear decoupled semiconductor transport and Poisson’s equations. The results obtained on the basis of numerical simulation have been validated with the reported analytical and experimental results by the others. Good agreement is found between both.