Simulation Standard Technical Journal

A Journal for Process and Device Engineers

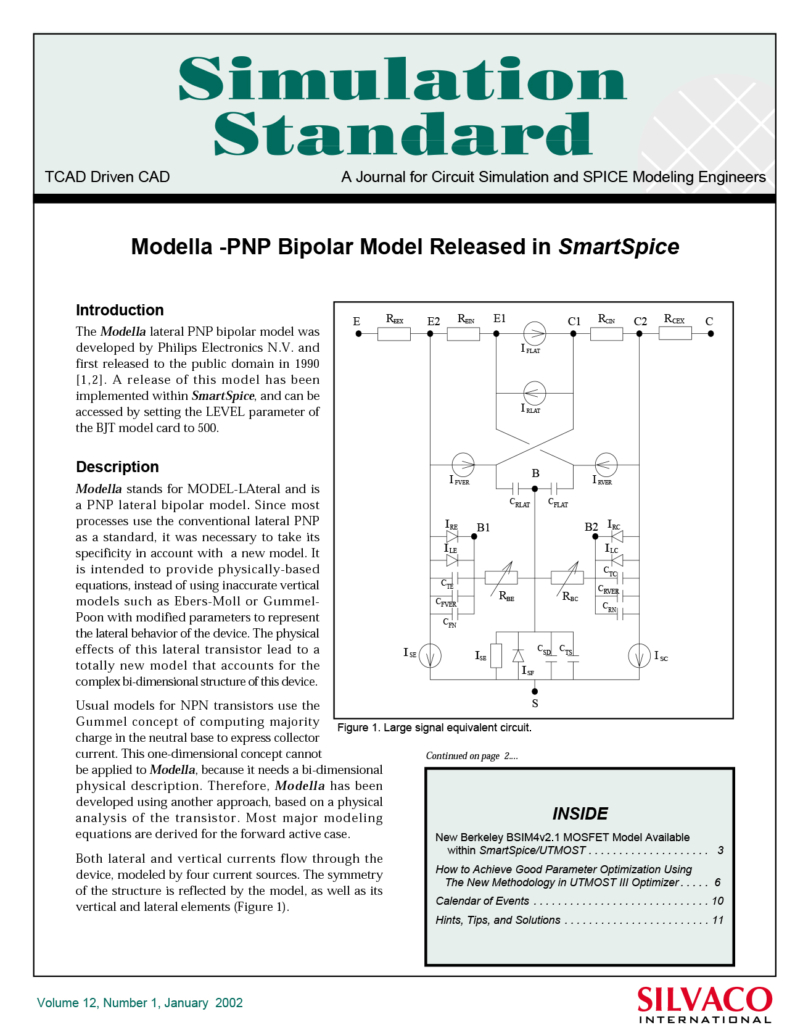

Modella PNP Bipolar Model Released in SmartSpice

The Modella lateral PNP bipolar model was developed by Philips Electronics N.V. and first released to the public domain in 1990 [1,2]. A release of this model has been implemented within SmartSpice, and can be accessed by setting the LEVEL parameter of the BJT model card to 500.

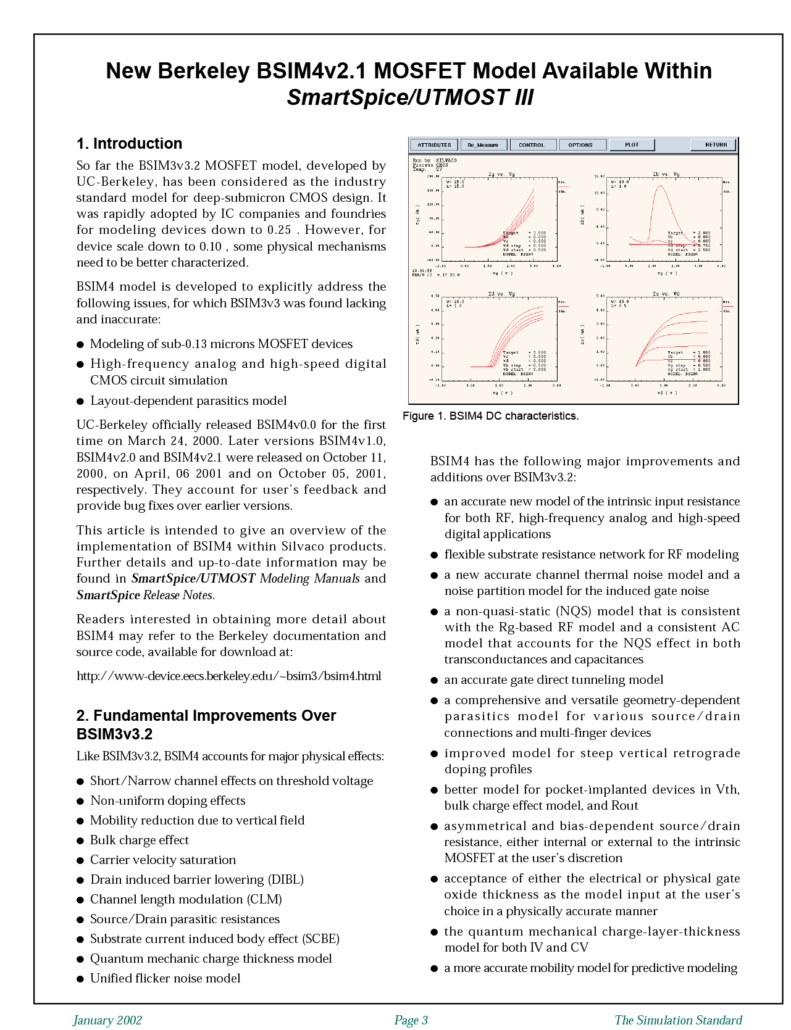

New Berkeley BSIM4v2.1 MOSFET Model Available Within SmartSpice/UTMOST III

So far the BSIM3v3.2 MOSFET model, developed by UC-Berkeley, has been considered as the industry standard model for deep-submicron CMOS design. It was rapidly adopted by IC companies and foundries for modeling devices down to 0.25 . However, for device scale down to 0.10 , some physical mechanisms need to be better characterized.

How to Achieve Good Parameter Optimization Using The New Methodology in UTMOST III Optimizer

Optimization is the task of finding the absolute best set of admissible conditions to achieve your objective, formulated in mathematical terms. The goal of optimization is, given a system, to find the setting of it's parameters so that to obtain the optimal performance. The performance of the system is given by an evaluation function. Optimization problems are commonly found in a wide range of fields, and it is also of central concern to many problems.

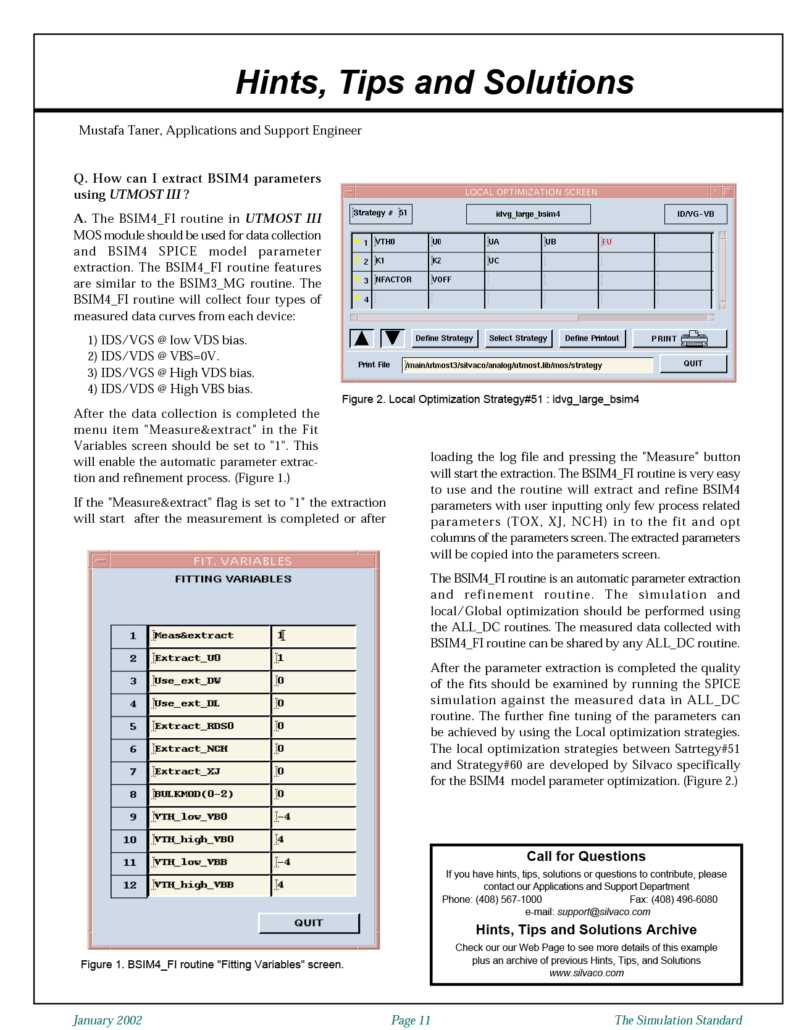

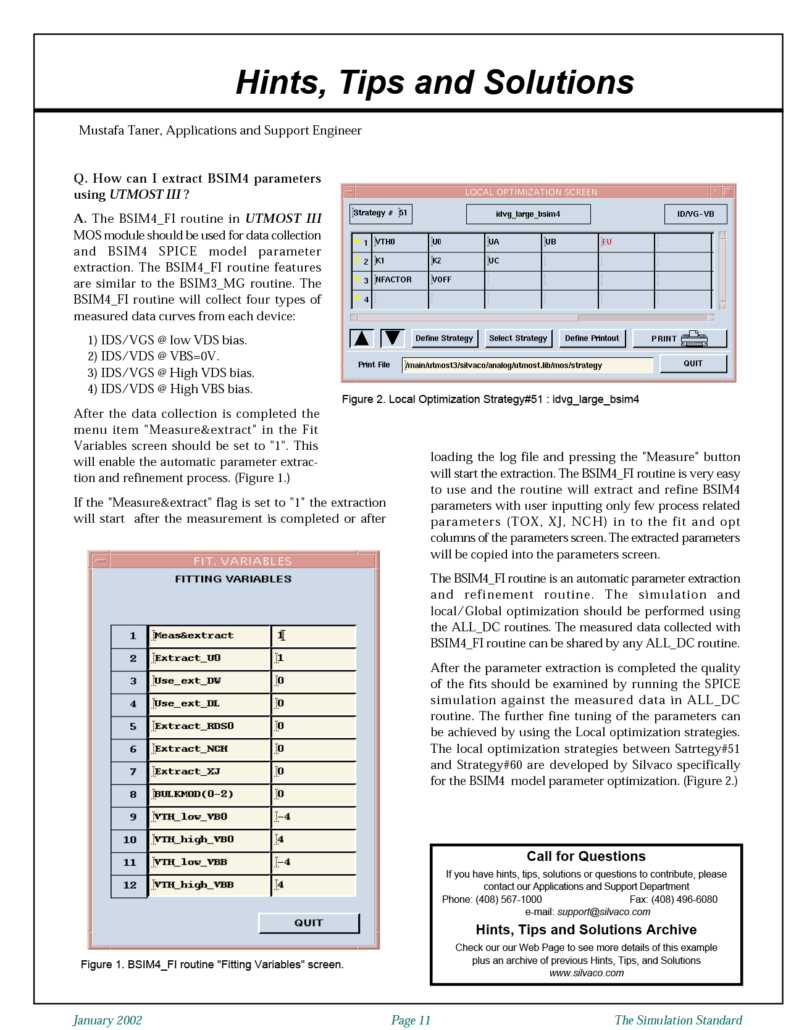

How to extract BSIM4 parameters using UTMOST III

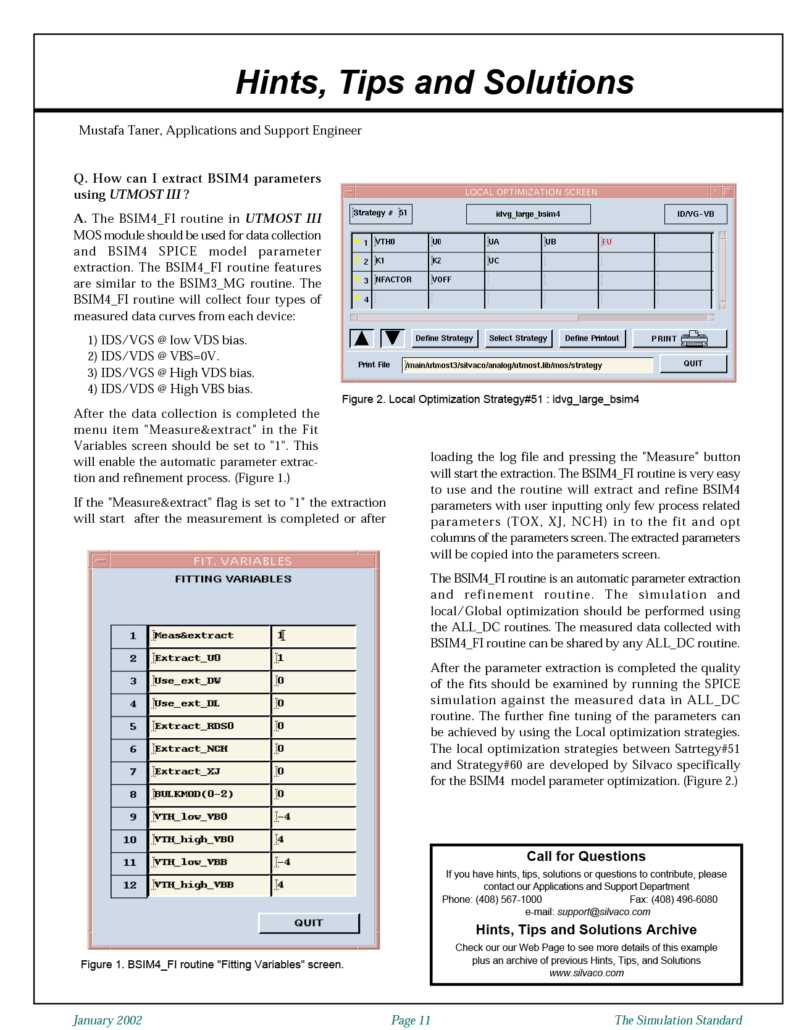

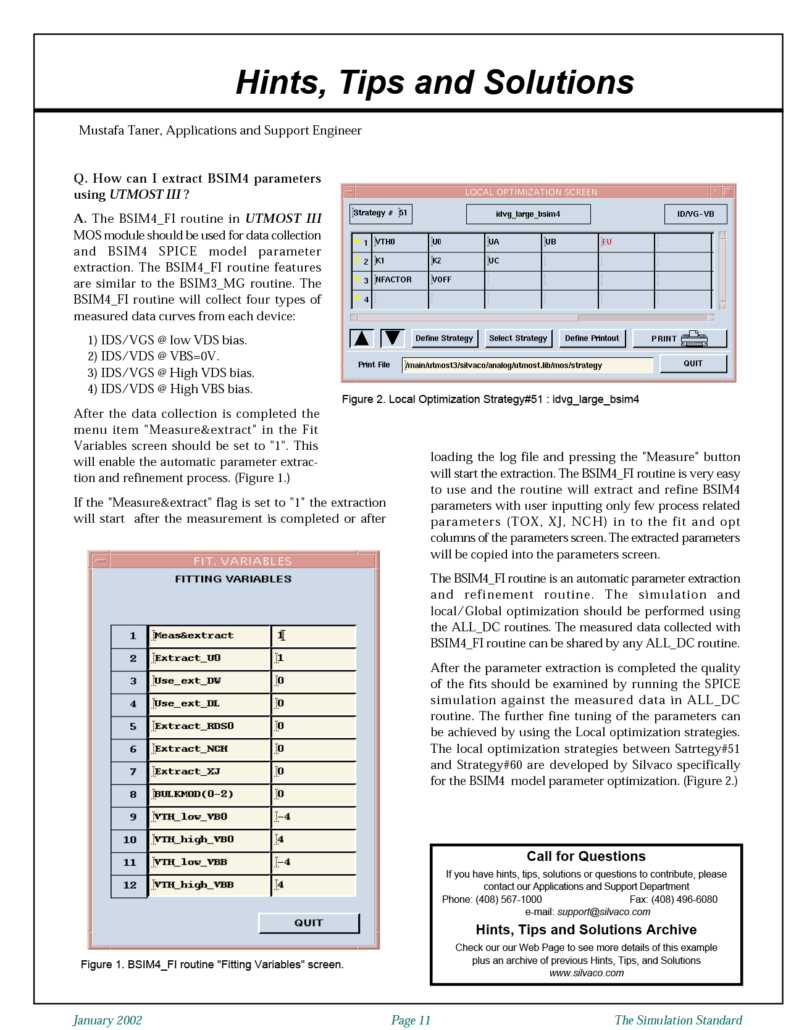

The BSIM4_FI routine in UTMOST III MOS module should be used for data collection and BSIM4 SPICE model parameter extraction. The BSIM4_FI routine features are similar to the BSIM3_MG routine. The BSIM4_FI routine will collect four types of measured data curves from each device.

Connectivity Options for DRC Spacing Check Operations in Savage

An IC layout has to satisfy many technological design requirements. One of these is spacing, i.e., a layout object has to be separated from another one by some minimal distance. In addition, any spacing requirement (e.g. minimal distance between layout objects) varies depending on the particular features of the layout objects, e.g. the layer the objects belong to, the purpose of these objects, etc.

Recent improvements in Expert, Savage, Guardian and Maverick

Most of recent improvements in Expert, Savage, Guardian and Maverick are aimed at the enhancement of the usability of these tools. All features described are developed according to the requests of our customers.