Simulation Standard Technical Journal

A Journal for Process and Device Engineers

Getting an Accurate FFT Spectral Plot in SmartSpice

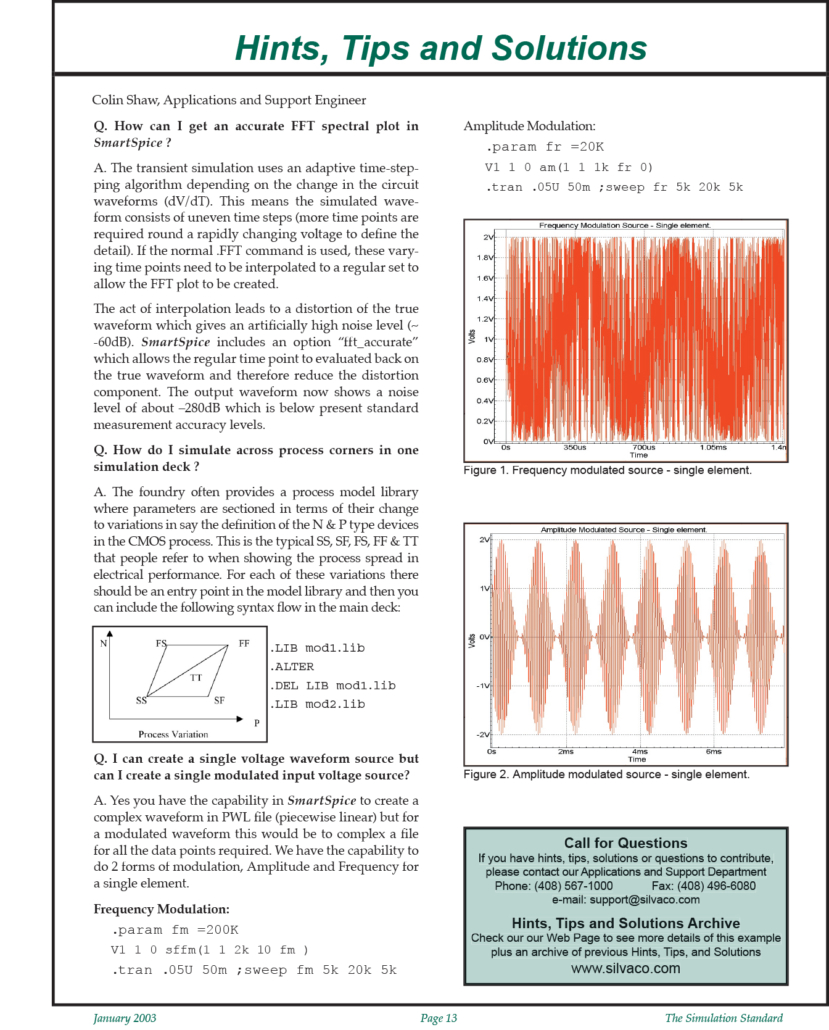

The transient simulation uses an adaptive time-stepping algorithm depending on the change in the circuit waveforms (dV/dT). This means the simulated waveform consists of uneven time steps (more time points are required round a rapidly changing voltage to define the detail). If the normal .FFT command is used, these varying time points need to be interpolated to a regular set to allow the FFT plot to be created.

Real-time DRC Verification by DRC Guard

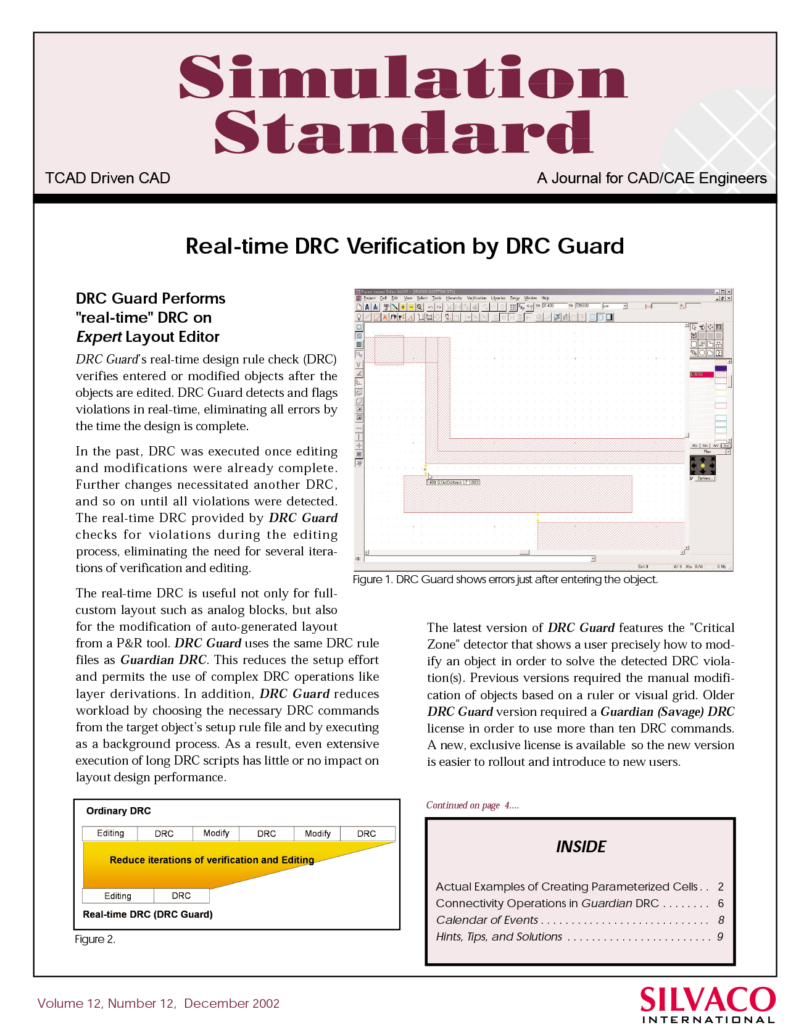

DRC Guard Performs "real-time" DRC on Expert Layout Editor. DRC Guard’s real-time design rule check (DRC) verifies entered or modified objects after the objects are edited. DRC Guard detects and flags violations in real-time, eliminating all errors by the time the design is complete.

Actual Examples of Creating Parameterized Cells

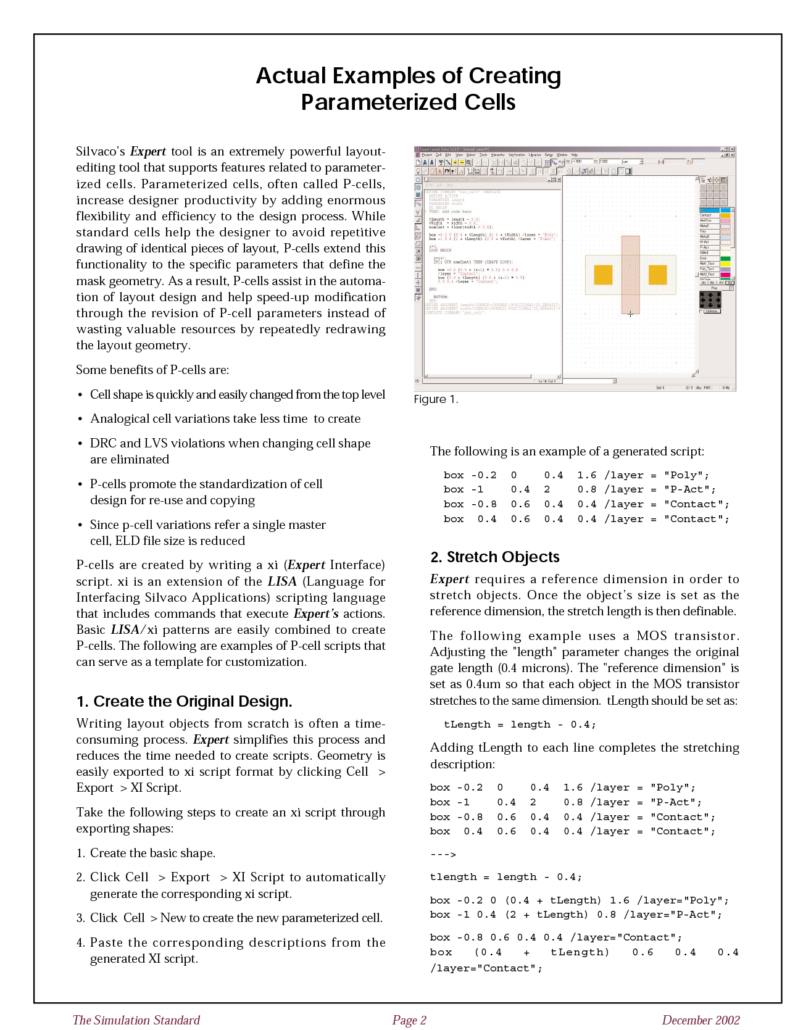

Silvaco’s Expert tool is an extremely powerful layout-editing tool that supports features related to parameterized cells. Parameterized cells, often called P-cells, increase designer productivity by adding enormous flexibility and efficiency to the design process. While standard cells help the designer to avoid repetitive drawing of identical pieces of layout, P-cells extend this functionality to the specific parameters that define the mask geometry. As a result, P-cells assist in the automation of layout design and help speed-up modification through the revision of P-cell parameters instead of wasting valuable resources by repeatedly redrawing the layout geometry.

Connectivity Operations in Guardian DRC

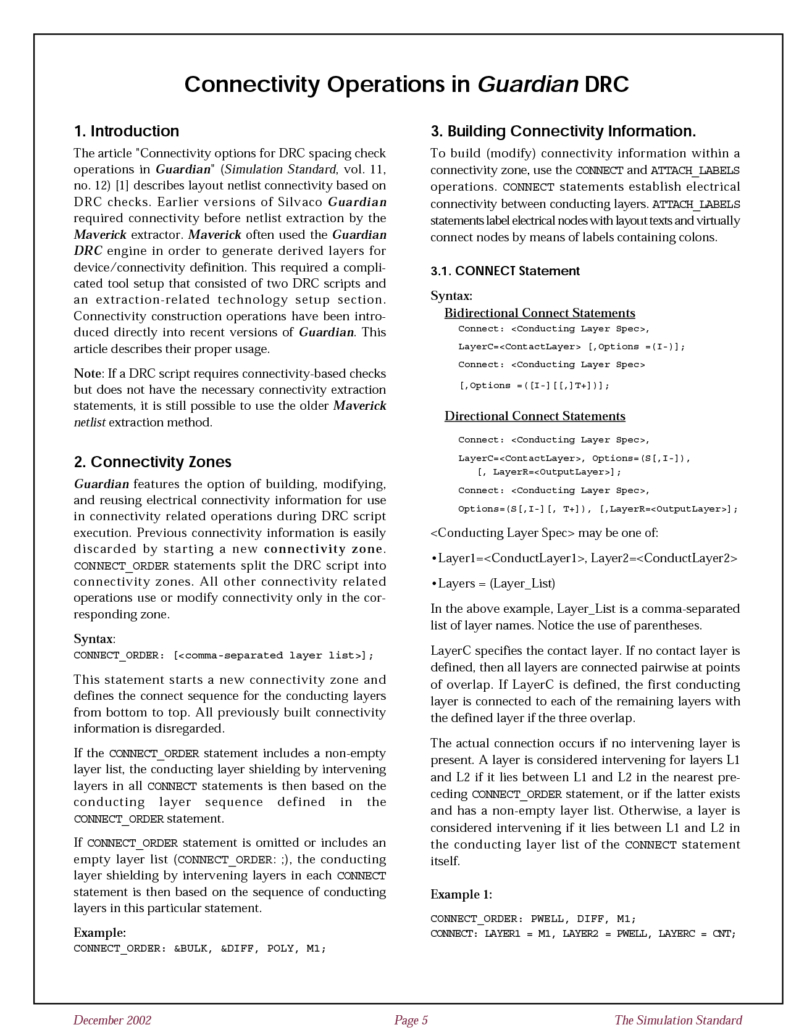

The article "Connectivity options for DRC spacing check operations in Guardian" (Simulation Standard, vol. 11, no. 12) [1] describes layout netlist connectivity based on DRC checks. Earlier versions of Silvaco Guardian required connectivity before netlist extraction by the Maverick extractor. Maverick often used the Guardian DRC engine in order to generate derived layers for device/connectivity definition. This required a complicated tool setup that consisted of two DRC scripts and an extraction-related technology setup section. Connectivity construction operations have been introduced directly into recent versions of Guardian. This article describes their proper usage.

How does Snap-to-grid Works for Cell Instances

We have lots of cells that become off-grid when we do cut-and-paste from other cells. We tried to use the "Tools->Snap Selected to Grid" command, but the cell doesn't get moved at all. How does Snap to grid works for Instances? Does it work for Instances?

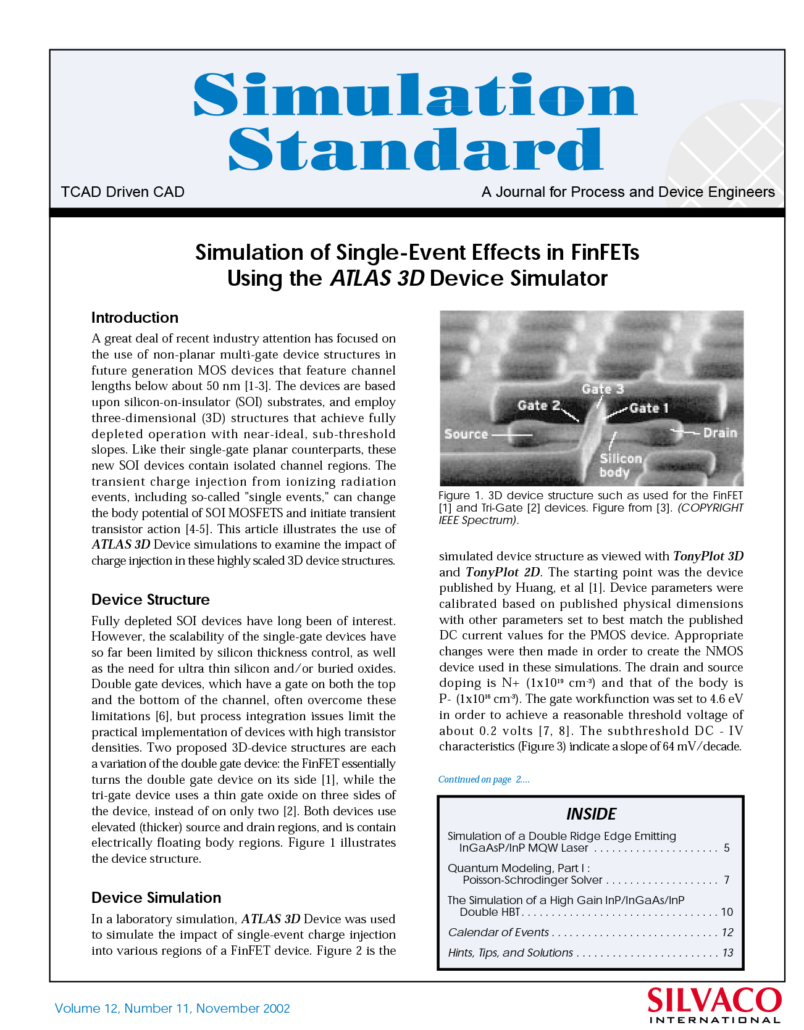

Simulation of Single-Event Effects in FinFETs Using the ATLAS Device Simulator

A great deal of recent industry attention has focused on the use of non-planar multi-gate device structures in future generation MOS devices that feature channel lengths below about 50 nm [1-3]. The devices are based upon silicon-on-insulator (SOI) substrates, and employ three-dimensional (3D) structures that achieve fully depleted operation with near-ideal, sub-threshold slopes. Like their single-gate planar counterparts, these new SOI devices contain isolated channel regions. The transient charge injection from ionizing radiation events, including so-called "single events," can change the body potential of SOI MOSFETS and initiate transient transistor action [4-5]. This article illustrates the use of ATLAS 3D Device simulations to examine the impact of charge injection in these highly scaled 3D device structures.