opt_ex12 : HiSIM_HV2 LDMOS Model Extraction

Requires: Utmost IV, SmartSpice, SmartView

Minimum Versions: Utmost IV 1.10.6.R, SmartSpice 4.17.1.C, SmartView 2.28.2.R

This example describes how to extract a standard HiSIM_HV2 model parameters. To extract a model which is scalable with geometry, multiple different device sizes must be included. In this example, three devices with the different channel width are used. And the device channel length is the drawn poly gate length which overlaps the intrinsic channel and the drift resistance regions. The following process parameters are defined in the model library. The values of ldrift1, ldrif2 and tox are fixed during the optimization.

- tox:Physical oxide thickness

- nsubc:Substrate impurity concentration

- nover:Impurity concentration of loverld at drain, and at source if cosym=1 and the value is declared

- loverld:Overlap length at drain side, and at source if cosym=1

- lovers:Overlap length at source side

- ldrift1:Length of light doped drift region at drain, and at source if cosym=1

- ldrift2:Length of heavily doped drift region at drain side, and at source if cosym=1

- xldld:Gate-overlap length at drain side

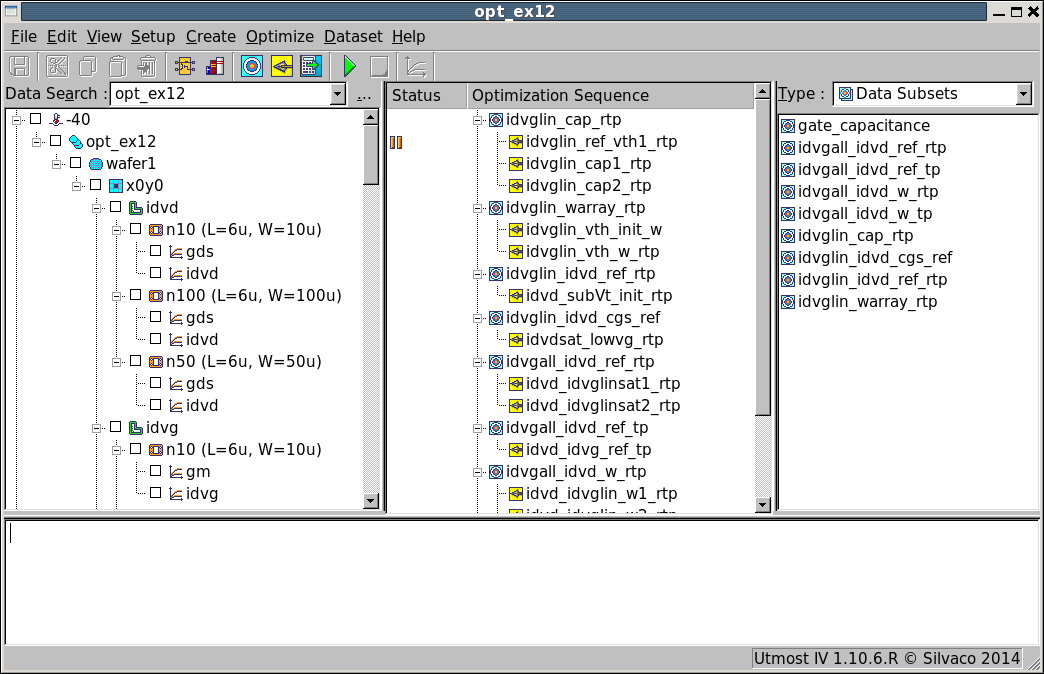

The project file opt_ex12.prj and the data file opt_ex12.uds for this example should be loaded into your database. When opened, the project will look as shown in opt_ex12_project.png .

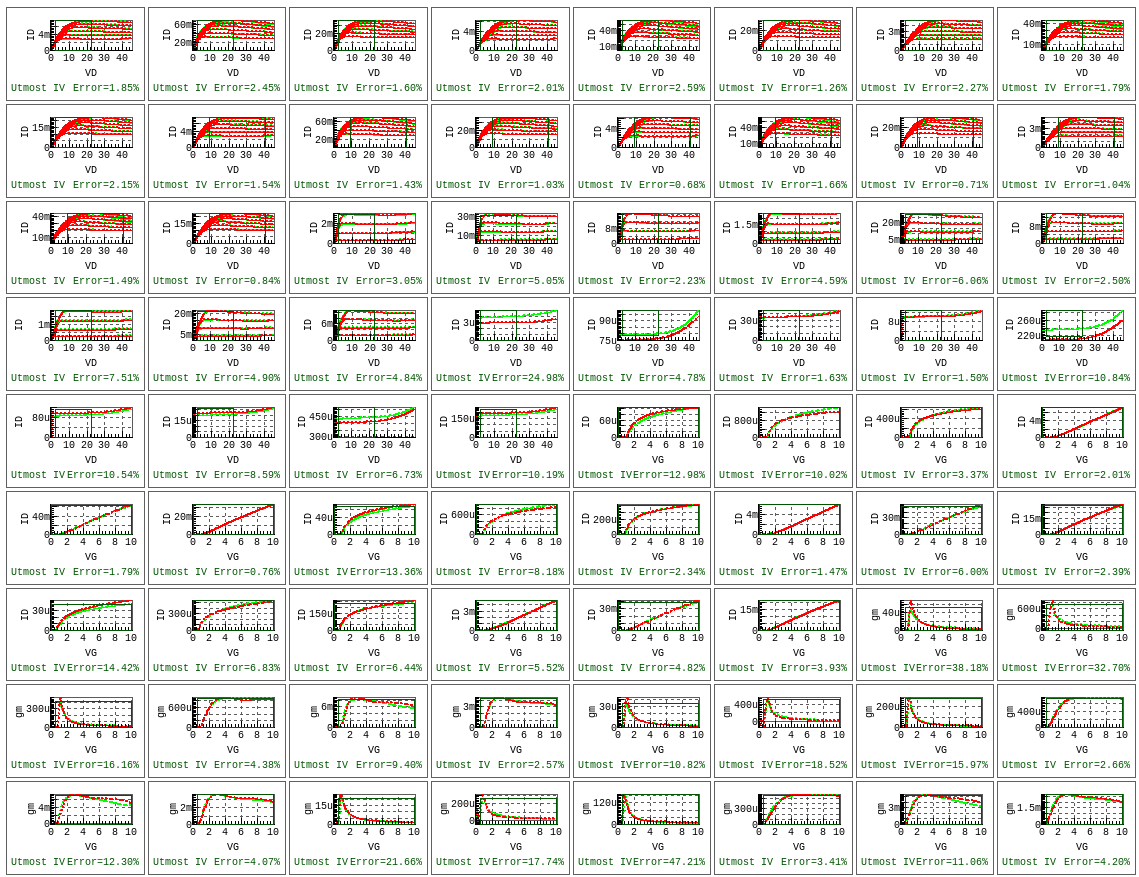

The optimization sequence, which fully automates the extraction of HiSIM_HV2 model parameters, consists of nine sections. The section one and two extract the threshold voltage region model parameters of HiSIM_HV2. The third section is prepared to get the initial model parameters for the substrate current model. The section four aims to optimize the drift region resistance parameters and the low field mobility parameters at the small drain and the gate voltages. The bias dependency of the drift region resistance is optimized in the section five to fit the drain current versus the drain voltage characteristics. This completes the reference geometry model parameter extraction at the room temperature. The section six through the eight optimize the geometry and the temperature scaling model parameters to complete the scalable HiSIM_HV2 model over the temperature change. The section nine is to get the gate capacitance characteristics. The green and red curves of the plots show the target data and the simulations, respectively.

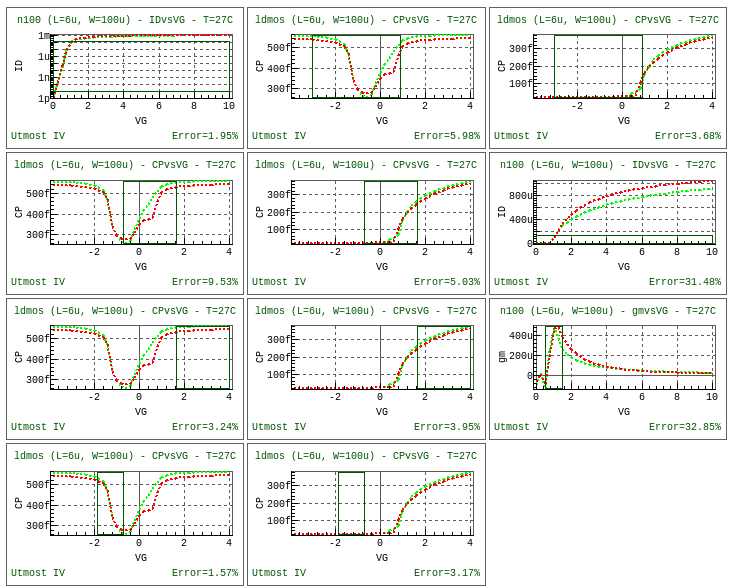

Section 1 : idvglin_cap_rtp

This section optimizes the parameters of the threshold voltage region for the ldmos reference geometry device. The data in this section is the drain current versus the gate voltage characteristics in the linear region and the cgg and cgs capacitance characteristics at the room temperature. The following model parameters are extracted.

- nsubc:Substrate impurity concentration

- vfbc:Flat band voltage

- muecb0:Coulomb scattering

- muecb1:Coulomb scattering

- mueph0:Phonon scattering

- mueph1:Phonon scattering

- xldld:Gate-overlap length at drain side

- loverld:Overlap length at drain side, and at source if COSYM=1

- lovers:Overlap length at source side

- nover:Impurity concentration of LOVERLD at drain, and at source if COSYM=1

- vfbover:Flat-band voltage in overlap region

- cgso:Gate-to-source overlap capacitance

- cgdo:Gate-to-drain overlap capacitance

After this step has been completed, the fit to measured data will be as shown in opt_ex12_01.png .

Section 2 : idvglin_warray_rtp

In this section, the parameters for narrow width effect are optimized using the devices of multiple width values. The following model parameters are extracted.

- nsubcw:Modification of substrate concentration for narrow width

- wl2:Threshold voltage shift due to small size effect

- wvth0:Threshold voltage shift

- muephw:Width dependence of phonon mobility reduction

Also, the following model parameters used at the previous step are included in this section to ensure the entire fitting.

- muecb0

- muecb1

- mueph0

- mueph1

After this step has been completed, the fit to measured data will be as shown in opt_ex12_02.png .

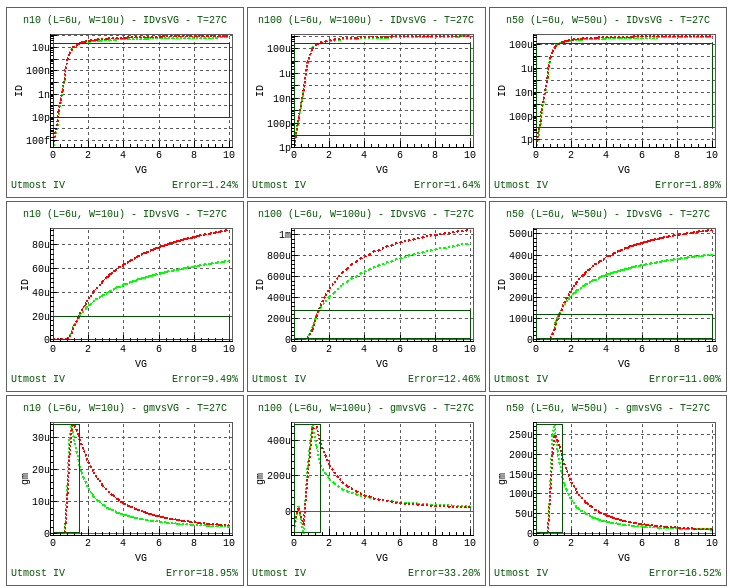

Section 3 : idvglin_idvd_ref_rtp

The section aims for getting the initial values of the substrate current model and the channel length modulation parameters using the drain current versus the drain voltage at the lowest vgs voltage. The following model parameters are extracted.

- ndep:Depletion charge contribution on effective-electric field

- ninv:Inversion charge contribution on effecitve-electric field

- bb:High-field-mobility degradation

- sub1:Substrate current coefficient of magnitude

- sub2:Substrate current coefficient of exponential term

- svds:Substrate current coefficient of exponential term

- svgs:Substrate current dependence on vgs

- clm1:Hardness coefficient of channel/contact junction

- clm2:Coefficient of qb contribution

- clm3:Coefficient of qi contribution

- sc2:Vds dependence of short-channel effect

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- muecb0

- muecb1

- mueph0

- mueph1

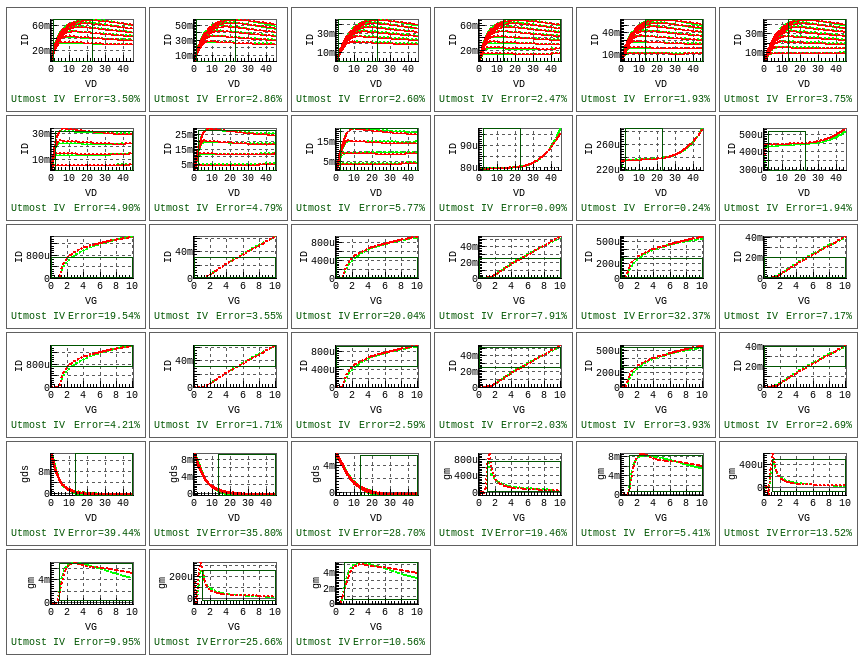

After this step has been completed, the fit to measured data will be as shown in opt_ex12_03.png .

Section 4 : idvglin_idvd_cgs_ref_rtp

The previous three sections concentrated mostly on the drain current versus the gate voltage at the linear region. The intention was to get the precise threshold voltage model parameters which are suitable for the different geometry devices. This section extracts several model parameters of the drift region resistance and the mobility model parameters for the reference geometry device. The datasets in this section are the drain current versus the gate voltage characteristics in the linear region, the drain current versus the drain voltage at the low vgs voltages and the cgs gate capacitance versus the gate voltage. The cgs capacitance is used to observe the effect of the drift region resistance parameters. The following model parameters are extracted.

- muesr0:Surface roughness scattering

- muesr1:Surface roughness scattering

- ninvd:Reduced resistance effect for small Vds

- vmax:Saturation velocity

- rdrdl1:Effective ldrift of current in drift region for cordrift=1

- rdrcx:Coefficient of current flow from xov for cordrift=1

- rdrmue:Field-dependent mobility in drift region for cordrift=1

- rdrqover:Inclusion of the overlap change in rdrift for cordrift=1

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- muecb0

- muecb1

- mueph0

- mueph1

- ndep

- ninv

- bb

After this step has been completed, the fit to measured data will be as shown in opt_ex12_04.png .

Section 5 : idvgall_idvd_ref_rtp

The previous step etracted the several drift region resistance parameters as the initial values for the succeeding optimization steps. This section will use the drain current versus the drain voltage data for the reference geometry to optimize all parameters of the drift resistance model. This step completes the single geometry model at the nominal temperature. The following parameters are extracted.

- vover:Velocity overshoot effect

- rdrcar:High field injection in drift region for cordrift=1

- rdrdjunc:Junction depth at channel/drift region for cordrift=1

- rdrvmax:Saturation velocity in drift region for cordrift=1

- rdrbb:High field mobility in drift region

- rth0:Thermal resistance

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- nsubc

- vfbc

- meucb0

- muecb1

- mueph0

- mueph1

- muesr0

- muesr1

- ndep

- ninv

- ninvd

- bb

- vmax

- rdrcx

- rdrdl1

- rdrqover

- clm1

- clm2

- clm3

- sub1

- sub2

- svds

- svgs

After this step has been completed, the fit to measured data will be as shown in opt_ex12_05.png .

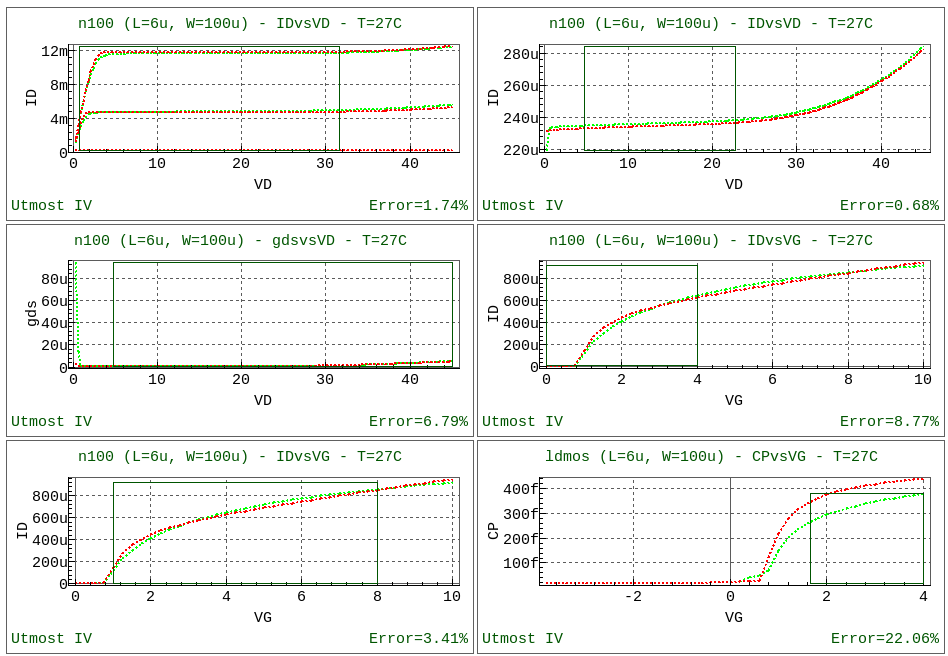

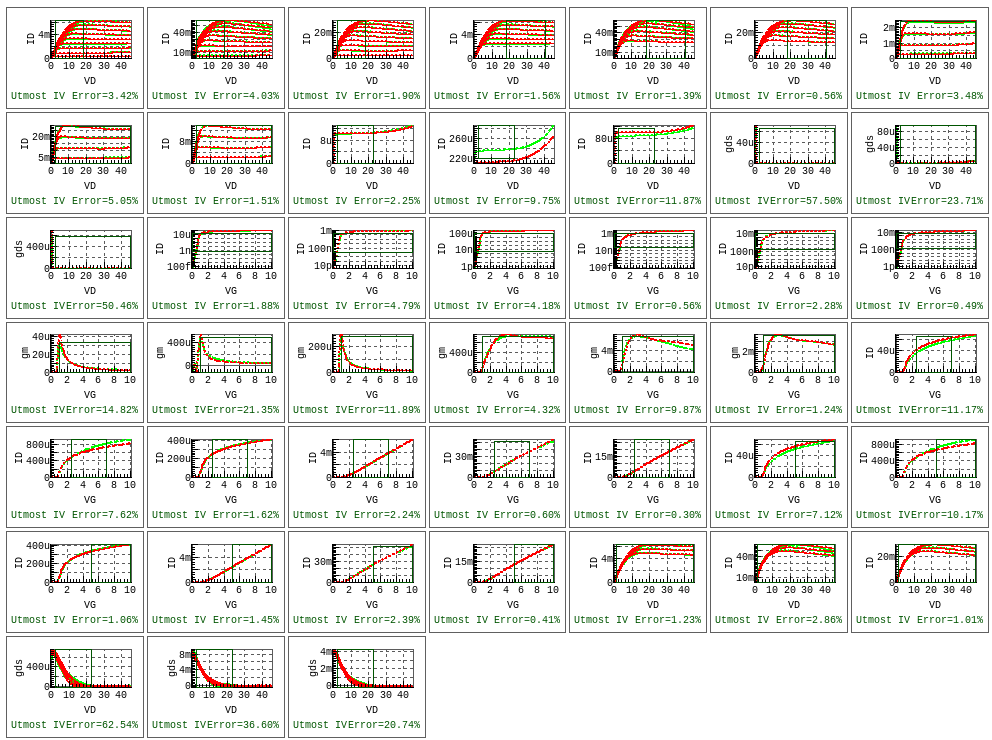

Section 6: idvgall_idvd_ref_tp

This section extracts the temperature model parameters using both the drain current versus the gate voltage characteristics in the linear and the saturation regions and the drain current versus the drain voltage for the reference geometry device at three temperatures. The following parameters are extracted.

- bgtmp1:Temperature dependence of bandgap

- bgtmp2:Temperature dependence of bandgap

- muetmp:Temperature dependence of phonon scattering

- vmaxt1:Temperature dependence of velocity

- vmaxt2:Temperature dependence of velocity

- vtmp:Temperature dependence of the saturation velocity

- rdrmuetmp:Temperature dependence of resistance for cordrift=1

- rdrvtmp:Temperature dependence of resistance for cordrift=1

- rthtemp1:Temperature dependence of thermal resistance

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- vfbc

- ndep

- ninv

- rdrmue

- rdrvmax

After this step has been completed, the fit to measured data will be as shown in opt_ex12_06.png .

Section 7 : idvgall_idvd_w_rtp

The previous section completed the single geometry temperature model. All geometry devices at the room temperature are used to fit the geometry scaling parameters in this section. The following model parameters are extracted.

- xwd:Gate-overlap width

- muepwp:Width dependence of phonon mobility reduction

- muesrw:Change of surface roughness related mobility

- mueswp:Change of surface roughness related mobility

- muephs:Mobility modification due to small size

- ninvdw:Width dependence of high field mobility

- ninvdwp:Width dependence of high field mobility

- rdrvmaxw:Saturation velocity wgate dependence for cordrift=1

- rdrvmaxwp:Saturation velocity wgate dependence for cordrift=1

- rth0w:Width dependence of thermal resistance

- rth0wp:Width dependence of thermal resistance

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- vfbc

- mueph0

- mueph1

- muesr0

- muesr1

- ninvd

- bb

- vmax

- vover

- rth0

- muephw

- wvth0

- sub1

- sub2

- svds

- svgs

- rdrdl1

- rdrcx

- rdrdjunc

- rdrmue

- rdrqover

- rdrvmax

- rdrbb

After this step has been completed, the fit to measured data will be as shown in opt_ex12_07.png .

Section 8 : idvgall_idvd_w_tp

The section is to complete the dc characteristics for all geometry devices at all temperatures. The following model parameters are extracted.

- ninvdt1:Temperature dependence of universal mobility model

- ninvdt2:Temperature dependence of universal mobility model

- rthtemp2:Temperature dependence of thermal resistance

The following model parameters used at the previous steps are included in this section.

- bgtmp1

- bgtmp2

- muetmp

- vtmp

- vmaxt1

- vmaxt2

- rthtemp1

- rdrmuetmp

- rdrvtmp

- mueph0

- mueph1

- muesr0

- muesr1

- ninvd

- vmax

- vover

- rdrmue

- rdrvmax

- rth0

After this step has been completed, the fit to measured data will be as shown in opt_ex12_08.png .

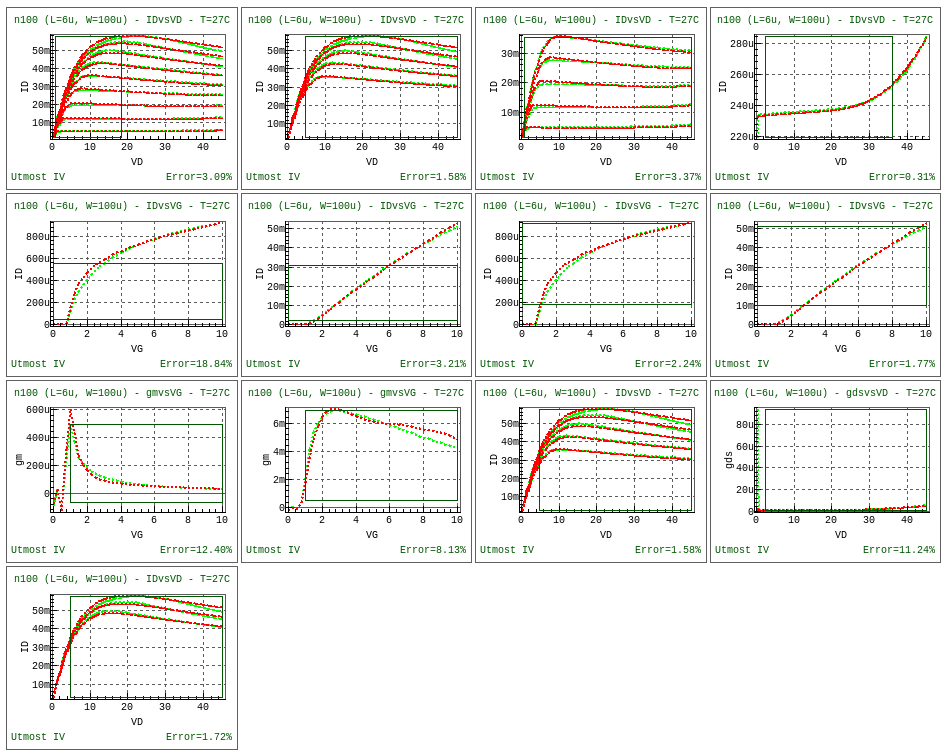

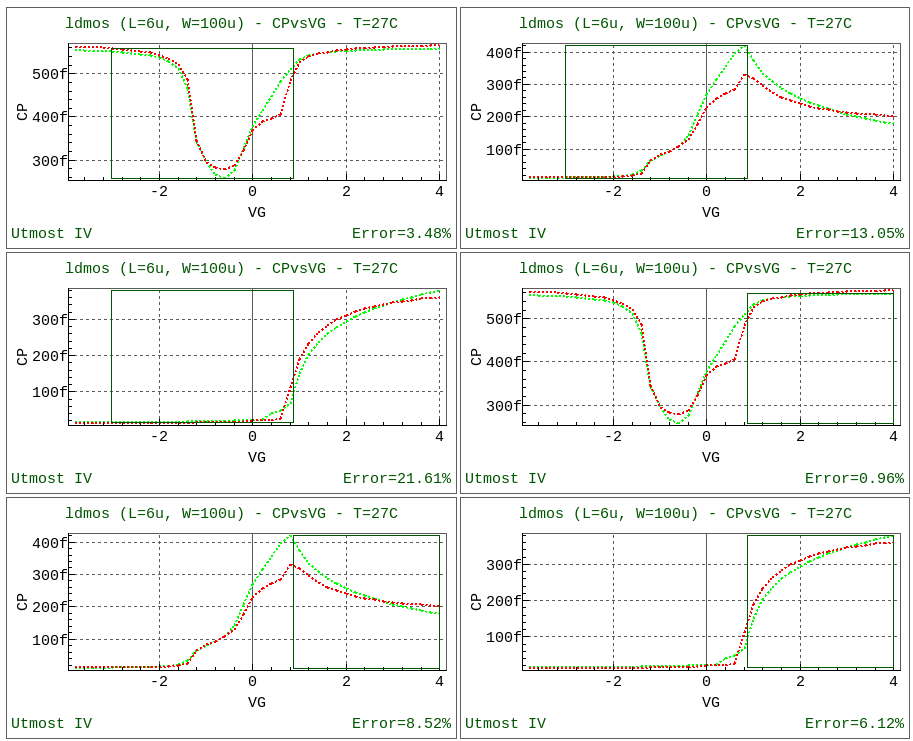

Section 9 : gate_capacitance

This section is to finalize the gate capacitance characteristic fitting. The following model parameters are extracted.

- xwdc:Gate overlap in width for capacitance calculation

- cvdsover:Parameter for cgg for vds!=0

The parameters used in the previous section are the following;

- cgdo

- cgso

- loverld

After this step has been completed, the fit to measured data will be as shown in opt_ex12_09.png .

The sequence is prepared for the best fit. No repeated run would be necessary. When complete, the model card can be exported into an external model library file as shown in opt_ex12.lib.

Note for reducing the run time.

Utmost IV is able to control the number of parallel runs of SmartSpice. The increase of number of SmartSpice executions shortens the run time for the multi-core machines. Edit -> Preferences -> Simulator .

opt_ex12.lib

.MODEL HiSIM_HV2 NMOS ( +LEVEL = 73 VERSION = 2.1 coovlp = 1 +coovlps = 1 coisub = 1 coiigs = 0 +cogidl = 0 coisti = 0 coadov = 1 +conqs = 0 corg = 0 corbnet = 0 +coflick = 0 cothrml = 0 coign = 0 +coiprv = 1 copprv = 1 codfm = 0 +coselfheat = 1 +cotemp = 0 +cosubnode = 0 +cosym = 0 cordrift = 1 coqovsm = 1 +coerrrep = 1 eg0 = 1.1785 bgtmp1 = 0.000340352 +bgtmp2 = -5.68918e-07 muetmp = 1.78362 tnom = 27 +vtmp = -0.169935 vmaxt1 = -0.000606117 vmaxt2 = -1.86801e-06 +ninvdt1 = 0.000732181 ninvdt2 = 1e-05 rthtemp1 = 5e-05 +rthtemp2 = 1.79221e-08 tox = 2.98e-08 xl = 0 +xw = 0 xld = 0 xldld = 3.87576e-06 +xwd = 9.00512e-08 xwdld = 0 xwdc = 1e-07 +tpoly = 2e-07 ll = 0 lld = 0 +lln = 0 wl = 0 wld = 0 +wln = 0 nsubc = 5.41312e+16 nsubp = 1e+18 +nsubsub = 1e+15 lp = 0 npext = 5e+17 +lpext = 1e-50 vfbc = -1.13187 vbi = 1.1 +kappa = 3.9 ldrift1 = 3e-06 ldrift2 = 1.7e-06 +ldrift1s = 0 ldrift2s = 1e-06 ddrift = 1e-06 +loverld = 2.55926e-06 lovers = 7.83537e-08 vbsmin = -10.5 +vgsmin = -100 muecb0 = 32874.2 muecb1 = 1157.34 +mueph0 = 0.263574 mueph1 = 29798 muephl = 0 +mueplp = 1 muesr0 = 2.11124 muesr1 = 1.52449e+14 +muesrl = 0 mueslp = 1 ndep = 0.0893114 +ndepl = 0 ndeplp = 1 ninv = 0.148841 +ninvd = 0.22999 ninvdw = 0.752123 ninvdwp = 0.0866919 +bb = 2.6751 vmax = 1.33085e+07 vover = 0.322467 +voverp = 0.3 rsh = 0 rshg = 0 +rbpb = 50 rbpd = 50 rbps = 50 +rbdb = 50 rbsb = 50 rdrdl1 = 1.14488e-07 +rdrdl2 = 0 rdrcx = 0.00678317 rdrcar = 0 +rdrdjunc = 1.92221e-06 rdrmue = 469.945 rdrvmax = 2.88406e+07 +rdrvmaxl = 0 +rdrvmaxlp = 1 +rdrvmaxw = -0.5 +rdrvmaxwp = 0.5 +rdrmuel = 0 rdrmuelp = 1 rdrbb = 1.50533 +rdrqover = 97405.3 rdrvtmp = -1.05428 +rdrmuetmp = 1.8348 +gbmin = 1e-12 rth0 = 1.42262 cth0 = 1e-07 +rth0w = -6.89456 rth0wp = 0.985914 rth0nf = 0 +powrat = 1 +prattemp1 = 0 +prattemp2 = 0 +shemax = 500 nfalp = 1e-19 nftrp = 1e+10 +cit = 0 falph = 1 sub1 = 0.0228145 +sub1l = 0.0025 sub1lp = 1 sub2 = 99.2565 +sub2l = 2e-06 svds = 0.74873 slg = 3e-08 +slgl = 0 slglp = 1 svbs = 0.5 +svbsl = 0 svbslp = 1 svgs = 0.700039 +svgsl = 0 svgslp = 1 svgsw = 0 +svgswp = 1 ibpc1 = 0 ibpc2 = 0 +ibpc1l = 0 ibpc1lp = -1 subld1 = 0 +subld2 = 0 subld1l = 0 subld1lp = 1 +xpdv = 0 xpvdth = 0 xpvdthg = 0 +mphdfm = -0.3 parl2 = 1e-08 sc1 = 0 +sc2 = 0 sc3 = 0 sc4 = 0 +scp1 = 0 scp2 = 0 scp3 = 0 +scp21 = 0 bs1 = 0 bs2 = 0.9 +clm1 = 0.0100247 clm2 = 4 clm3 = 0.5 +clm5 = 1 clm6 = 0 wfc = 0 +wvth0 = 0.114255 nsubcw = 1.32378 nsubcwp = 1 +nsubp0 = 0 nsubwp = 1 muephw = -3.78296 +muepwp = 1.00032 muesrw = 0.156143 mueswp = 0.76807 +vthsti = 0 vdsti = 0 scsti1 = 0 +scsti2 = 0 nsti = 1e+16 wsti = 0 +wstil = 0 wstilp = 1 wstiw = 0 +wstiwp = 1 wl1 = 0 wl1p = 1 +nsubpsti1 = 0 +nsubpsti2 = 0 +nsubpsti3 = 1 +muesti1 = 0 muesti2 = 0 muesti3 = 1 +saref = 1e-06 sbref = 1e-06 wl2 = 1.61006 +wl2p = 1 muephs = -2 muepsp = 1 +vovers = 0 voversp = 0 qme1 = 0 +qme2 = 2 qme3 = 0 pgd1 = 0 +pgd2 = 1 pgd4 = 0 gleak1 = 50 +gleak2 = 1e+07 gleak3 = 0.06 gleak4 = 4 +gleak5 = 7500 gleak6 = 0.25 gleak7 = 1e-06 +egig = 0 igtemp2 = 0 igtemp3 = 0 +glksd1 = 1e-15 glksd2 = 1000 glksd3 = -1000 +glkb1 = 5e-16 glkb2 = 1 glkb3 = 0 +glpart1 = 0.5 fn1 = 50 fn2 = 0.00017 +fn3 = 0 fvbs = 0.012 gidl1 = 2 +gidl2 = 3e+07 gidl3 = 0.9 gidl4 = 0 +gidl5 = 0.2 vzadd0 = 0.01 pzadd0 = 0.005 +ddltmax = 10 ddltslp = 0 ddltict = 10 +js0 = 5e-07 js0sw = 0 nj = 1 +njsw = 1 xti = 2 xti2 = 0 +divx = 0 ctemp = 0 cisb = 0 +cisbk = 0 cvb = 0 cj = 0.0005 +cjsw = 5e-10 cjswg = 5e-10 mj = 0.5 +mjsw = 0.33 mjswg = 0.33 pb = 1 +pbsw = 1 pbswg = 1 vdiffj = 0.0006 +tcjbd = 0 tcjbdsw = 0 tcjbdswg = 0 +tcjbs = 0 tcjbssw = 0 tcjbsswg = 0 +xqy = 0 xqy1 = 0 xqy2 = 2 +nover = 1.00038e+16 vfbover = 0.0690316 qovadd = 0 +novers = 1e+16 ovslp = 2.1e-07 ovmag = 0.6 +cgso = 8.7044e-11 cgdo = 5.45398e-11 cgbo = 0 +cvdsover = 0.367234 dly1 = 1e-10 dly2 = 0.7 +dly3 = 8e-07 pt2 = 0 pt4 = 0 +pt4p = 1 ptl = 0 ptlp = 1 +ptp = 3.5 gdl = 0 gdld = 0 +gdlp = 0 gdsleak = 0 lbinn = 1 +wbinn = 1 lmax = 1 lmin = 0 +wmax = 1 wmin = 0 )

opt_ex12.uds