07 : Selected Nets Extraction

Minimum Required Versions: Expert Expert 5.2204.3.R, Hipex 3.8.7.R, Guardian 4.8.36.R

Hipex-RC provides ways to reduce the size of a parasitic RC netlist for post layout simulation of a large layout block. One of them is the selected nets extraction function. This function is effective for reducing the run time of Hipex-RC. When this function is used, Hipex-RC extracts parasitic resistors and capacitors only for the selected nets of the critical path.

1. Starting the example

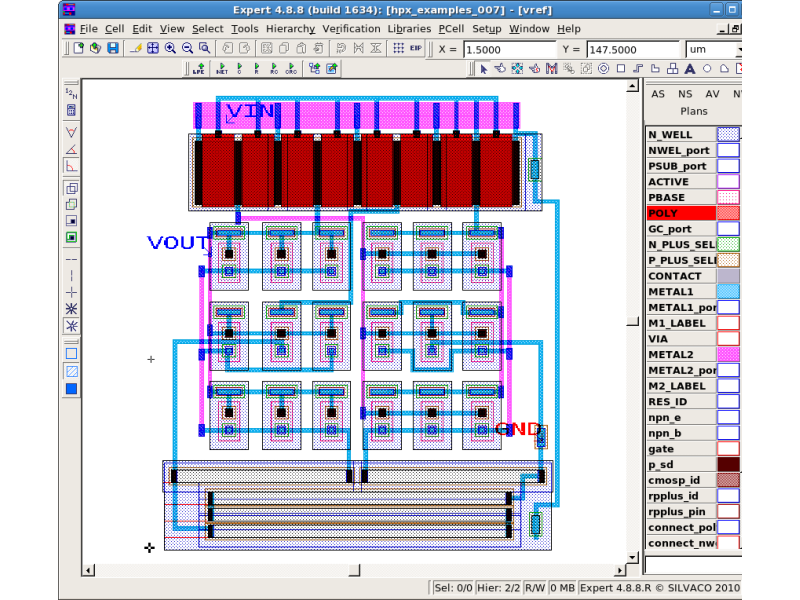

-Load hpx_ex_007.eld

-Open the "vref" cell as shown in figure1.

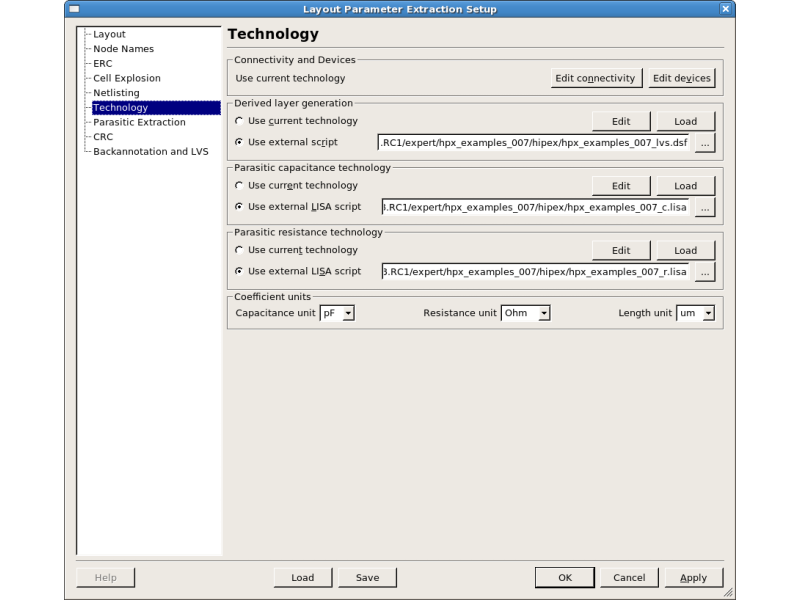

2. Loading the extraction technology

-Select the menu item Verification->Extraction->Setup , or click the "LPE setup" icon. Select "Technology" and specify the three files in "hipex" folder as shown in figure2.

Make sure the following settings are specified.

Derived layer generation file: hpx_examples_007_lvs.dsf

Parasitic capacitance technology file: hpx_examples_007_c.lisa

Parasitic resistance technology file: hpx_examples_007_r.lisa

-Select the menu item Setup->Technology->Device Setup , and within appeared "Device Setup" dialog select device "IND". Then, go to "File Name" section at the bottom of the dialog, and select file hpx_examples_007.lisa from "hipex" folder. This file contains the definition of the custom device

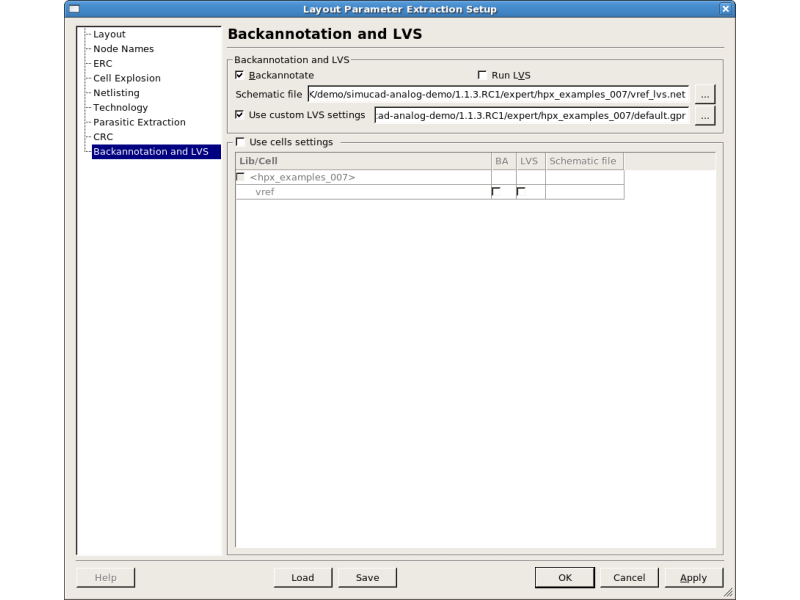

3. Setting up backannotation to the schematic netlist

Hipex-RC can annotate schematic net names to the parasitic RC netlist for post layout simulation.

Select "Backannotation and LVS" in the "Layout Parameter Extraction Setup" window. Setup the schematic netlist and the LVS settings file as shown in figure3.

Make sure the following settings are specified.

Schematic netlist: vref_lvs.net

LVS settings file: default.gpr

(The LVS settings file is saved in advance when the LVS verification with Guardian LVS is passed).

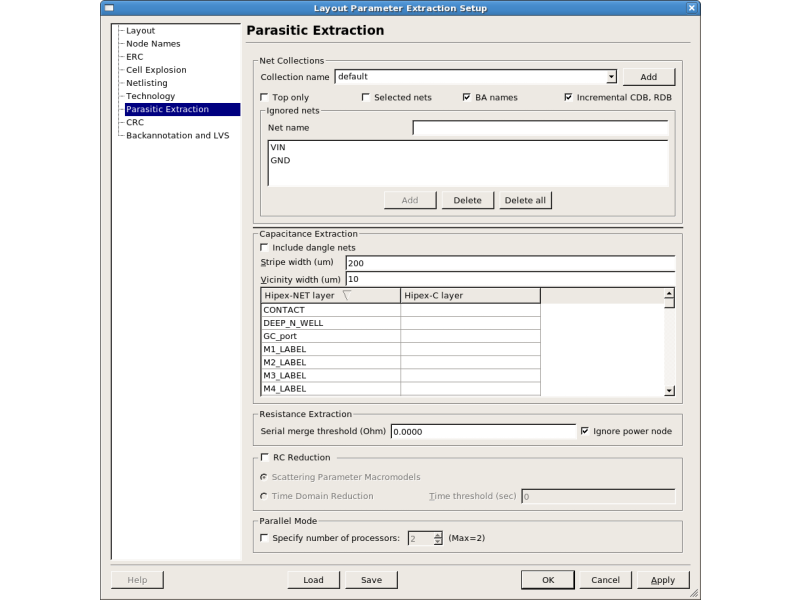

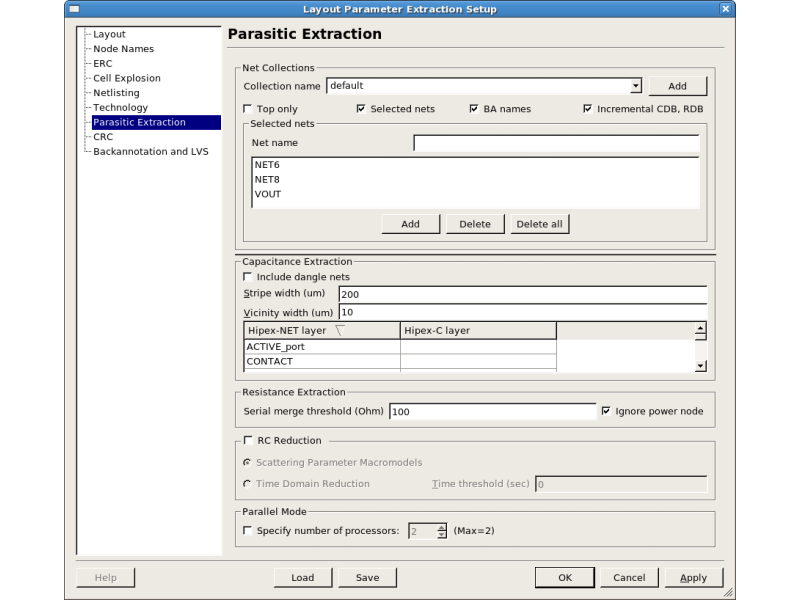

4. Setting up the selected nets for Hipex-RC

Select "Parasitic Extraction" in the "Layout Parameter Extraction Setup" window. Check the "Selected nets" and "BA names" checkboxes. Add target net names in the schematic as shown in figure4. Namely, select "NET6","NET8", and "VOUT" as the selected nets.

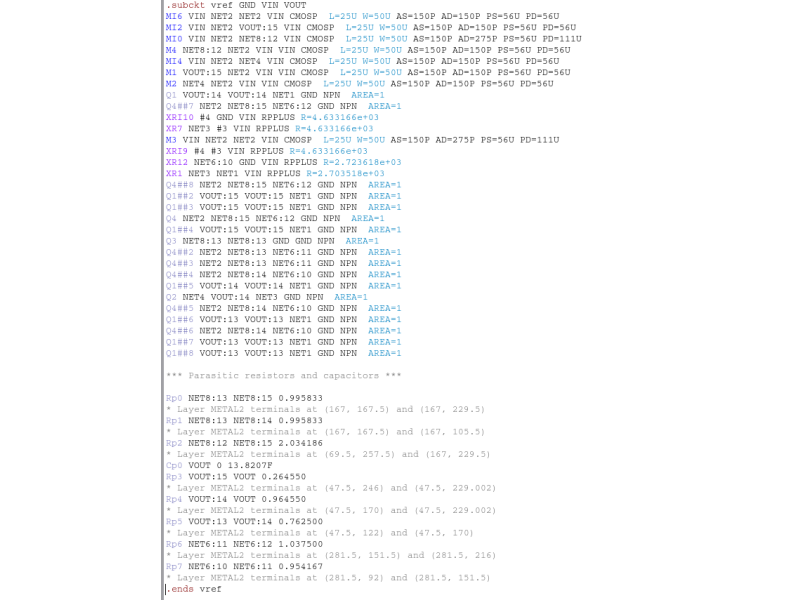

5. Running Hipex-NET and Hipex-RC

Select the menu item Verification->Extraction->Hipex-NET->Run , or click the "Run netlist extractor" icon. A layout netlist is generated as a result.

Then, select Verification->Extraction->Hipex-RC->Run , or click the "Run Hipex-RC" icon. The parasitic RC netlist as shown on figure5 is generated.

The netlist shows the extracted parasitic resistors and capacitors related only to the three nets.

6. About ignore nets setup

Hipex-RC provides not only the selected nets extraction function but also the ignored nets function. When this function is used, Hipex-RC doesn't extract parasitic resistors and capacitors for the ignored nets. An example setup is shown on figure6. This function can be used in the same way as the "selected nets" function, and is just as useful.

hpx_examples_007_c.lisa

cpx order substrate, poly1, metal6, metal5, metal4, metal3, metal2, metal1;

cpx Lateral metal1

/factor = 0.0358802,7.01689,3.32225

/max_distance = 3

/max_width = 0

/l_threshold = 0

;

cpx Area metal1 metal2

2.65626e-005

;

cpx Fringe metal1 metal2

4.15574e-005,0.320702,0.671211

/max_distance = 3

/max_width = 0

;

cpx Fringe metal2 metal1

2.32849e-005,0.674515,0.0001

/max_distance = 3

/max_width = 0

;

cpx Area metal1 metal3

1.11391e-005

;

cpx Fringe metal1 metal3

3.30439e-005,0.188656,1.04677

/max_distance = 3

/max_width = 0

;

cpx Fringe metal3 metal1

1.39623e-005,0.482325,0.0001

/max_distance = 3

/max_width = 0

;

cpx Area metal1 metal4

7.04721e-006

;

cpx Fringe metal1 metal4

2.91315e-005,0.13222,1.60862

/max_distance = 3

/max_width = 0

;

cpx Fringe metal4 metal1

1.02029e-005,0.457873,0.0442828

/max_distance = 3

/max_width = 0

;

cpx Area metal1 metal5

5.15393e-006

;

cpx Fringe metal1 metal5

2.63965e-005,0.103979,2.04571

/max_distance = 3

/max_width = 0

;

cpx Fringe metal5 metal1

8.08203e-006,0.401369,0.176259

/max_distance = 3

/max_width = 0

;

cpx Area metal1 metal6

4.06251e-006

;

cpx Fringe metal1 metal6

2.55413e-005,0.0918767,1.36021

/max_distance = 3

/max_width = 0

;

cpx Fringe metal6 metal1

6.70174e-006,0.371057,0.269995

/max_distance = 3

/max_width = 0

;

cpx Area metal1 poly1

2.65626e-005

;

cpx Fringe metal1 poly1

4.16003e-005,0.324475,0.66098

/max_distance = 3

/max_width = 0

;

cpx Fringe poly1 metal1

6.20891e-006,1.14039,1.06638

/max_distance = 3

/max_width = 0

;

cpx Area metal1 substrate

2.28684e-005

;

cpx Fringe metal1 substrate

4.00033e-005,0.301935,0.6695

/max_distance = 3

/max_width = 0

;

cpx Lateral metal2

/factor = 2.87372,14.324,4.09817

/max_distance = 3

/max_width = 0

/l_threshold = 0

;

cpx Area metal2 metal3

2.65626e-005

;

cpx Fringe metal2 metal3

4.14748e-005,0.316919,0.680858

/max_distance = 3

/max_width = 0

;

cpx Fringe metal3 metal2

2.88581e-005,0.548685,0.0001

/max_distance = 3

/max_width = 0

;

cpx Area metal2 metal4

1.11391e-005

;

cpx Fringe metal2 metal4

3.2822e-005,0.187093,1.02423

/max_distance = 3

/max_width = 0

;

cpx Fringe metal4 metal2

1.86321e-005,0.39867,0.000655802

/max_distance = 3

/max_width = 0

;

cpx Area metal2 metal5

7.04721e-006

;

cpx Fringe metal2 metal5

2.8634e-005,0.133856,1.47255

/max_distance = 3

/max_width = 0

;

cpx Fringe metal5 metal2

1.41837e-005,0.315184,0.179235

/max_distance = 3

/max_width = 0

;

cpx Area metal2 metal6

5.15393e-006

;

cpx Fringe metal2 metal6

2.73627e-005,0.11064,0.993631

/max_distance = 3

/max_width = 0

;

cpx Fringe metal6 metal2

1.15493e-005,0.27378,0.335871

/max_distance = 3

/max_width = 0

;

cpx Area metal2 poly1

1.11391e-005

;

cpx Fringe metal2 poly1

3.31559e-005,0.19132,1.04343

/max_distance = 3

/max_width = 0

;

cpx Fringe poly1 metal2

3.09488e-006,1.92499,0.0001

/max_distance = 3

/max_width = 0

;

cpx Area metal2 substrate

1.04324e-005

;

cpx Fringe metal2 substrate

3.25999e-005,0.182479,1.11013

/max_distance = 3

/max_width = 0

;

cpx Lateral metal3

/factor = 16.9639,18.1812,4.34947

/max_distance = 3

/max_width = 0

/l_threshold = 0

;

cpx Area metal3 metal4

2.65626e-005

;

cpx Fringe metal3 metal4

4.13121e-005,0.314694,0.672485

/max_distance = 3

/max_width = 0

;

cpx Fringe metal4 metal3

3.18446e-005,0.484687,0.0922895

/max_distance = 3

/max_width = 0

;

cpx Area metal3 metal5

1.11391e-005

;

cpx Fringe metal3 metal5

3.23603e-005,0.189379,0.929541

/max_distance = 3

/max_width = 0

;

cpx Fringe metal5 metal3

2.14639e-005,0.321993,0.17096

/max_distance = 3

/max_width = 0

;

cpx Area metal3 metal6

7.04721e-006

;

cpx Fringe metal3 metal6

3.00478e-005,0.140594,0.630696

/max_distance = 3

/max_width = 0

;

cpx Fringe metal6 metal3

1.67761e-005,0.252539,0.379062

/max_distance = 3

/max_width = 0

;

cpx Area metal3 poly1

7.04721e-006

;

cpx Fringe metal3 poly1

2.93665e-005,0.133438,1.6484

/max_distance = 3

/max_width = 0

;

cpx Fringe poly1 metal3

2.0743e-006,1.87101,0.0001

/max_distance = 3

/max_width = 0

;

cpx Area metal3 substrate

6.7576e-006

;

cpx Fringe metal3 substrate

2.90538e-005,0.129063,1.72374

/max_distance = 3

/max_width = 0

;

cpx Lateral metal4

/factor = 27.9705,19.8358,4.36927

/max_distance = 3

/max_width = 0

/l_threshold = 0

;

cpx Area metal4 metal5

2.65626e-005

;

cpx Fringe metal4 metal5

4.09763e-005,0.318422,0.613318

/max_distance = 3

/max_width = 0

;

cpx Fringe metal5 metal4

3.37177e-005,0.431092,0.212975

/max_distance = 3

/max_width = 0

;

cpx Area metal4 metal6

1.11391e-005

;

cpx Fringe metal4 metal6

3.46533e-005,0.19562,0.29801

/max_distance = 3

/max_width = 0

;

cpx Fringe metal6 metal4

2.33927e-005,0.283069,0.311585

/max_distance = 3

/max_width = 0

;

cpx Area metal4 poly1

5.15393e-006

;

cpx Fringe metal4 poly1

2.68931e-005,0.102796,2.22025

/max_distance = 3

/max_width = 0

;

cpx Fringe poly1 metal4

1.52826e-006,0.31447,4.60139

/max_distance = 3

/max_width = 0

;

cpx Area metal4 substrate

4.9973e-006

;

cpx Fringe metal4 substrate

2.66828e-005,0.100253,2.29093

/max_distance = 3

/max_width = 0

;

cpx Lateral metal5

/factor = 36.0895,20.8244,4.37456

/max_distance = 3

/max_width = 0

/l_threshold = 0

;

cpx Area metal5 metal6

2.65626e-005

;

cpx Fringe metal5 metal6

4.5747e-005,0.323023,0.133653

/max_distance = 3

/max_width = 0

;

cpx Fringe metal6 metal5

3.50076e-005,0.401176,0.29952

/max_distance = 3

/max_width = 0

;

cpx Area metal5 poly1

4.06251e-006

;

cpx Fringe metal5 poly1

2.48633e-005,0.0853638,2.61317

/max_distance = 3

/max_width = 0

;

cpx Fringe poly1 metal5

1.23351e-006,1.70834,0.0001

/max_distance = 3

/max_width = 0

;

cpx Area metal5 substrate

3.96456e-006

;

cpx Fringe metal5 substrate

2.47081e-005,0.0836769,2.67925

/max_distance = 3

/max_width = 0

;

cpx Lateral metal6

/factor = 14.3622,18.3981,4.14307

/max_distance = 3

/max_width = 0

/l_threshold = 0

;

cpx Area metal6 poly1

3.35256e-006

;

cpx Fringe metal6 poly1

2.41867e-005,0.0791816,1.71297

/max_distance = 3

/max_width = 0

;

cpx Fringe poly1 metal6

1e-006,0.0859697,0.983548

/max_distance = 3

/max_width = 0

;

cpx Area metal6 substrate

3.28557e-006

;

cpx Fringe metal6 substrate

2.40558e-005,0.0778986,1.75752

/max_distance = 3

/max_width = 0

;

cpx Lateral poly1

/factor = 1e-006,11.9201,4.11329

/max_distance = 3

/max_width = 0

/l_threshold = 0

;

cpx Area poly1 substrate

0.00345313

;

cpx Fringe poly1 substrate

0.000116307,2.18888,0.176024

/max_distance = 3

/max_width = 0

;

hpx_examples_007.lisa

!DEVICE IND metal1(PLUS) metal1(MINUS) !! PROPERTY W,S,NR,RAD define procedure IND do begin TURNS = 0.0; RADIUS = 0.0; WIDTH = 0.0; SPACE = 0.0; NW=0; !!!!!!Number of Rings TURNS = (((device_count("NR_counter")-8)*0.25)/4)+0.25; !!!!!!Width of each turn NW=ceil(TURNS-0.25); WIDTH1 = (device_perimeter(REL_NONE, "width", ""))/((1+NW)*4); WIDTH = WIDTH1*1E6; !!!!!!Space between turns SPACE1 = ((device_perimeter(REL_NONE, "space", ""))/(2*(NW-1)))-WIDTH1; SPACE = SPACE1*1E6; !!!!!!!Inner radius of Inductor RADIUS1 = (device_perimeter(REL_NONE, "radius", ""))/4; RADIUS = RADIUS1*1E6; ! Transfer of calculated parameters to c-code device_set_property("TURN", TURNS); device_set_property("INR", RADIUS); device_set_property("WIDTH", WIDTH); device_set_property("SPACE", SPACE); end;

hpx_examples_007_lvs.dsf

/* *********************************************************** */

/* DRC Script */

/* Drcon DRC Deck Converter v4.5.2.B (build 1221) */

/* */

/* Source file: "LVS_RC_Calibre_0.18um_MM_1P6M_1.8V+3.3V.lvs.out" */

/* Thu Aug 21 15:09:46 2008 */

/* *********************************************************** */

Layers:

N_WELL (42 /* Original */)

, P_WELL (59 /* Original */)

, ACTIVE (43 /* Original */)

, THICK_ACTIVE (60 /* Original */)

, PBASE (58 /* Original */)

, POLY_CAP1 (28 /* Original */)

, POLY (46 /* Original */)

, SILICIDE_BLOCK (29 /* Original */)

, N_PLUS_SELECT (45 /* Original */)

, P_PLUS_SELECT (44 /* Original */)

, POLY2 (56 /* Original */)

, HI_RES_IMPLANT (34 /* Original */)

, CONTACT (25 /* Original */)

, METAL1 (49 /* Original */)

, VIA (50 /* Original */)

, METAL2 (51 /* Original */)

, VIA2 (61 /* Original */)

, METAL3 (62 /* Original */)

, VIA3 (30 /* Original */)

, METAL4 (31 /* Original */)

, CAP_TOP_METAL (35 /* Original */)

, VIA4 (32 /* Original */)

, METAL5 (33 /* Original */)

, VIA5 (36 /* Original */)

, METAL6 (37 /* Original */)

, DEEP_N_WELL (38 /* Original */)

, GLASS (52 /* Original */)

, PADS (26 /* Original */)

, RES_ID (1, 0 /* Original */)

, INDDMY_ID (2, 0 /* Original */)

;

/* 1 */ free_layer_definition_order: yes;

/* 2 */ Merge_Input: on;

/* 3 */ Database_Precision: 1000;

/* 4 */ Grid_Resolution: GridX = 1, GridY = 1;

/* 5 */ Unit: 1um;

/* 6 */ Incremental_Connect: no;

/* 7 */ Update_layout: input=no, technology=no, new=no, layers=

(pnp_id,pnp_e,pnp_c,npn_e,npn_b,gate,p_sd,n_sd,cmosp_id,cmosn_id,hvcmosp_id,

hvpmos_d,hvnmos_s,rpplus_id,rnpoly_id,rpoly_id,rnwell_id,rpplus_pin,connect_poly,

connect_nwell,substrate,sub_tie,well_tie,deepnwell_tie,p1p2_id,poly_con,poly2cap_con,

ind_id,connect_metal1,ind_plus,ind_minus,NR_counter,width,space,radius

);

Select: Layer1=PBASE, Layer2=N_PLUS_SELECT, LayerR=&PNP_PBASE, Relation=overlap, options=(not);

UnderSize: Value=1um, Layer=&PNP_PBASE, LayerR=&A;

Logicform: pnp_id=&A.dif.(ACTIVE);

Contours: Layer=pnp_id, LayerR=pnp_e, options=(holes);

Logicform: pnp_c=PBASE.and.ACTIVE.dif.(pnp_e.or.P_PLUS_SELECT.or.N_PLUS_SELECT);

Logicform: npn_e=PBASE.and.N_PLUS_SELECT.AND.ACTIVE;

LogicForm: npn_b=PBASE.and.ACTIVE.and.P_PLUS_SELECT;

Logicform: gate=POLY.and.ACTIVE;

Logicform: p_sd=(P_PLUS_SELECT.and.ACTIVE.AND.N_WELL).dif.(POLY.or.DEEP_N_WELL.or.RES_ID);

Logicform: n_sd=(N_PLUS_SELECT.and.ACTIVE).dif.(POLY.or.THICK_ACTIVE.or.N_WELL);

Logicform: cmosp_id=gate.and.P_PLUS_SELECT.and.N_WELL;

Logicform: cmosn_id=gate.and.N_PLUS_SELECT.dif.THICK_ACTIVE;

Logicform: hvcmosp_id=gate.and.P_PLUS_SELECT.and.THICK_ACTIVE.dif.P_WELL;

Select: Layer1=ACTIVE, Layer2=hvcmosp_id, Relation=overlap, LayerR=&A1;

Logicform: hvpmos_d=&A1.dif.(POLY.or.P_WELL.or.N_WELL);

Select: Layer1=ACTIVE, Layer2=hvcmosp_id, Relation=overlap, LayerR=&A2;

Logicform: hvpmos_s=&A2.dif.(hvcmosp_id.or.N_WELL.or.hvpmos_d);

Logicform: hvcmosn_id=gate.and.N_PLUS_SELECT.and.THICK_ACTIVE;

Select: Layer1=ACTIVE, Layer2=hvcmosn_id, Relation=overlap, LayerR=&A3;

Logicform: hvnmos_d=&A3.dif.(POLY.or.P_PLUS_SELECT.or.N_WELL);

Select: Layer1=ACTIVE, Layer2=hvcmosn_id, Relation=overlap, LayerR=&A4;

Logicform: hvnmos_s=&A4.dif.(hvcmosn_id.or.hvnmos_d.or.P_PLUS_SELECT);

Logicform: rpplus_id=N_WELL.and.P_PLUS_SELECT.and.ACTIVE.and.RES_ID;

Logicform: rnpoly_id=N_PLUS_SELECT.and.POLY.and.RES_ID;

Logicform: rpoly_id=(POLY.and.RES_ID).dif.N_PLUS_SELECT;

Logicform: rnwell_id=(N_WELL.and.RES_ID).dif.P_PLUS_SELECT;

LogicForm: &rpplus_pin1=(ACTIVE.and.P_PLUS_SELECT).dif.RES_ID;

Select: Relation=touch, Layer1=&rpplus_pin1, Layer2=rpplus_id, LayerR=rpplus_pin;

Logicform: connect_poly=POLY.dif.(RES_ID.or.POLY2);

Logicform: connect_nwell=N_WELL.dif.(RES_ID);

Substrate: LayerR=substrate;

Logicform: sub_tie=(ACTIVE.AND.P_PLUS_SELECT).dif.(DEEP_N_WELL.or.N_WELL);

Logicform: well_tie=(ACTIVE.AND.N_PLUS_SELECT.AND.N_WELL).dif.npn_e;

Logicform: &deepnwell_tie1=ACTIVE.AND.N_PLUS_SELECT.AND.DEEP_N_WELL;

Select: Relation=touch, Layer1=&deepnwell_tie1, Layer2=hvpmos_s, LayerR=&tempA;

LogicForm: deepnwell_tie=&deepnwell_tie1.dif.&tempA;

Logicform: p1p2_id=(POLY2.and.POLY).dif.ACTIVE;

Logicform: poly_con=(POLY.dif.POLY2).and.CONTACT;

Logicform: poly2cap_con=POLY.AND.POLY2.and.CONTACT;

LogicForm: &ind_id1=METAL1.and.INDDMY_ID;

PERIMETER: Layer=&ind_id1, Value=75, Type=GT, LayerR=ind_id;

select: relation=vertex, Layer=METAL1, Options=(5:99999), LayerR=&metal1;

//LogicForm: connect_metal1=&metal1.dif.ind_id;

Corner: Layer=ind_id, Value=0.1, Options=(INSIDE,A90),LayerR=&temp11;

Select: Relation=flush, Layer1=&temp11, Layer2=INDDMY_ID, LayerR=&temp2;

Size: Layer=&temp2, within=ind_id, Options=(cut), step=0.5, Value=10, LayerR=ind_plus;

Corner: Layer=ind_id, Value=0.2, Options=(inside,A90), LayerR=&temp12;

Size: Layer=&temp12, within=ind_id, Options=(cut), step=0.5, Value=10, LayerR=&temp;

//Select: Relation=flush, Layer1=&temp, Layer2=INDDMY_ID, LayerR=ind_minus, Options=(not);

//Added new by AK 09/10/08

Select: Relation=vertex, Layer=&ind_id1, Options=(1:4), LayerR=&ind_minus1;

LogicForm: ind_minus2=METAL2.and.INDDMY_ID.and.&ind_minus1;

LogicForm: connect_metal1=(METAL1.dif.ind_id); //so that the 4-vertex M1 piece inside INDDMY will also get connectivity

Select: Relation=overlap, Layer1=METAL2, Layer2=ind_id, LayerR=ind_minus;

//New code ends

Corner: Layer=ind_id, Value=0.1, Options=(inside,any), LayerR=NR_counter;

LogicForm: width=(METAL1.and.METAL2.and.INDDMY_ID).dif.ind_minus2;

LogicForm: &space1=(METAL2.and.INDDMY_ID).dif.METAL1;

PERIMETER: Layer=&space1, LayerR=&space2, Value=79, Type=LT;

SELECT: Relation=touch, layer1=&space2, Layer2=ind_id, LayerR=&space3;

SELECT_edges: Relation=coincide, layer1=&space3, Layer2=ind_id, LayerR=&space4;

SELECT: Relation=touch, layer1=&space3, Layer2=&space4, LayerR=space, options=(2:2);

LogicForm: &space1A=(METAL2.and.INDDMY_ID).dif.METAL1;

PERIMETER: Layer=&space1A, LayerR=radius, Value=80, Type=GE;

hpx_examples_007_r.lisa

rpx define_parasitic Wire

/layer = METAL1

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.05

;

rpx define_parasitic Wire

/layer = METAL2

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.05

;

rpx define_parasitic Wire

/layer = METAL3

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.05

;

rpx define_parasitic Wire

/layer = METAL4

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.05

;

rpx define_parasitic Wire

/layer = METAL5

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.05

;

rpx define_parasitic Wire

/layer = METAL6

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.01

;

rpx define_parasitic Wire

/layer = POLY2

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 100.0

;

rpx define_parasitic Contact

/layer = VIA

/top = METAL1

/bottom = METAL2

/pres_area_resistivity_value = 0.05

;

rpx define_parasitic Contact

/layer = VIA2

/top = METAL2

/bottom = METAL3

/pres_area_resistivity_value = 0.05

;

rpx define_parasitic Contact

/layer = VIA3

/top = METAL3

/bottom = METAL4

/pres_area_resistivity_value = 0.05

;

rpx define_parasitic Contact

/layer = VIA4

/top = METAL4

/bottom = METAL5

/pres_area_resistivity_value = 0.05

;

rpx define_parasitic Contact

/layer = VIA5

/top = METAL6

/bottom = METAL5

/pres_area_resistivity_value = 0.04

;

rpx define_parasitic Wire

/layer = connect_poly

/max_length = 0.0

/contact_oversize = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 50.0

;

rpx define_parasitic Contact

/layer = poly2cap_con

/top = POLY2

/bottom = METAL1

/pres_area_resistivity_value = 0.05

;

rpx define_parasitic Contact

/layer = poly_con

/top = METAL1

/bottom = connect_poly

/pres_area_resistivity_value = 0.05

;

hpx_ex_007_net_cmd.lisa

!--------------------------------------------------------------------

!Net command file

!DESIGN : design

!TECHNO : techno

!USER :

!TIME : Fri May 29 00:52:07 2020

!--------------------------------------------------------------------

! HIPEX to CUP map table

cup layer "metal4" /hipex_layer="METAL4";

cup layer "metal5" /hipex_layer="METAL5";

cup layer "metal6" /hipex_layer="METAL6";

cup layer "metal2" /hipex_layer="METAL2";

cup layer "metal3" /hipex_layer="METAL3";

cup layer "poly1" /hipex_layer="connect_poly";

cup layer "substrate" /hipex_layer="substrate";

cup layer "metal1" /hipex_layer="connect_metal1";

! GDS LAYER MAP

hipex layer /gds_layer= 0 /gds_type= 0 /geom_layer="pnp_id";

hipex layer /gds_layer= 25 /gds_type= 0 /geom_layer="CONTACT";

hipex layer /gds_layer= 30 /gds_type= 0 /geom_layer="VIA3";

hipex layer /gds_layer= 31 /gds_type= 0 /geom_layer="METAL4";

hipex layer /gds_layer= 31 /gds_type= 1 /geom_layer="M4_LABEL";

hipex layer /gds_layer= 32 /gds_type= 0 /geom_layer="VIA4";

hipex layer /gds_layer= 33 /gds_type= 0 /geom_layer="METAL5";

hipex layer /gds_layer= 33 /gds_type= 1 /geom_layer="M5_LABEL";

hipex layer /gds_layer= 36 /gds_type= 0 /geom_layer="VIA5";

hipex layer /gds_layer= 37 /gds_type= 0 /geom_layer="METAL6";

hipex layer /gds_layer= 37 /gds_type= 1 /geom_layer="M6_LABEL";

hipex layer /gds_layer= 38 /gds_type= 0 /geom_layer="DEEP_N_WELL";

hipex layer /gds_layer= 42 /gds_type= 5 /geom_layer="NWEL_port";

hipex layer /gds_layer= 43 /gds_type= 5 /geom_layer="ACTIVE_port";

hipex layer /gds_layer= 46 /gds_type= 1 /geom_layer="POLY_LABEL";

hipex layer /gds_layer= 46 /gds_type= 5 /geom_layer="GC_port";

hipex layer /gds_layer= 49 /gds_type= 0 /geom_layer="METAL1";

hipex layer /gds_layer= 49 /gds_type= 1 /text_layer="M1_LABEL";

hipex layer /gds_layer= 49 /gds_type= 5 /geom_layer="METAL1_port";

hipex layer /gds_layer= 50 /gds_type= 0 /geom_layer="VIA";

hipex layer /gds_layer= 51 /gds_type= 0 /geom_layer="METAL2";

hipex layer /gds_layer= 51 /gds_type= 1 /text_layer="M2_LABEL";

hipex layer /gds_layer= 51 /gds_type= 5 /geom_layer="METAL2_port";

hipex layer /gds_layer= 56 /gds_type= 0 /geom_layer="POLY2";

hipex layer /gds_layer= 58 /gds_type= 0 /geom_layer="PBASE";

hipex layer /gds_layer= 59 /gds_type= 5 /geom_layer="PSUB_port";

hipex layer /gds_layer= 61 /gds_type= 0 /geom_layer="VIA2";

hipex layer /gds_layer= 62 /gds_type= 0 /geom_layer="METAL3";

hipex layer /gds_layer= 62 /gds_type= 1 /geom_layer="M3_LABEL";

hipex layer /gds_layer= 63 /gds_type= 0 /geom_layer="pnp_e";

hipex layer /gds_layer= 64 /gds_type= 0 /geom_layer="pnp_c";

hipex layer /gds_layer= 65 /gds_type= 0 /geom_layer="npn_e";

hipex layer /gds_layer= 66 /gds_type= 0 /geom_layer="npn_b";

hipex layer /gds_layer= 67 /gds_type= 0 /geom_layer="p_sd";

hipex layer /gds_layer= 68 /gds_type= 0 /geom_layer="n_sd";

hipex layer /gds_layer= 69 /gds_type= 0 /geom_layer="cmosp_id";

hipex layer /gds_layer= 70 /gds_type= 0 /geom_layer="cmosn_id";

hipex layer /gds_layer= 71 /gds_type= 0 /geom_layer="hvcmosp_id";

hipex layer /gds_layer= 72 /gds_type= 0 /geom_layer="hvpmos_d";

hipex layer /gds_layer= 73 /gds_type= 0 /geom_layer="hvpmos_s";

hipex layer /gds_layer= 74 /gds_type= 0 /geom_layer="hvcmosn_id";

hipex layer /gds_layer= 75 /gds_type= 0 /geom_layer="hvnmos_d";

hipex layer /gds_layer= 76 /gds_type= 0 /geom_layer="hvnmos_s";

hipex layer /gds_layer= 77 /gds_type= 0 /geom_layer="rpplus_id";

hipex layer /gds_layer= 78 /gds_type= 0 /geom_layer="rnpoly_id";

hipex layer /gds_layer= 79 /gds_type= 0 /geom_layer="rpoly_id";

hipex layer /gds_layer= 80 /gds_type= 0 /geom_layer="rnwell_id";

hipex layer /gds_layer= 81 /gds_type= 0 /geom_layer="rpplus_pin";

hipex layer /gds_layer= 82 /gds_type= 0 /geom_layer="connect_poly";

hipex layer /gds_layer= 83 /gds_type= 0 /geom_layer="connect_nwell";

hipex layer /gds_layer= 84 /gds_type= 0 /geom_layer="substrate";

hipex layer /gds_layer= 85 /gds_type= 0 /geom_layer="sub_tie";

hipex layer /gds_layer= 86 /gds_type= 0 /geom_layer="well_tie";

hipex layer /gds_layer= 87 /gds_type= 0 /geom_layer="deepnwell_tie";

hipex layer /gds_layer= 88 /gds_type= 0 /geom_layer="p1p2_id";

hipex layer /gds_layer= 89 /gds_type= 0 /geom_layer="poly_con";

hipex layer /gds_layer= 90 /gds_type= 0 /geom_layer="poly2cap_con";

hipex layer /gds_layer= 91 /gds_type= 0 /geom_layer="ind_id";

hipex layer /gds_layer= 92 /gds_type= 0 /geom_layer="ind_plus";

hipex layer /gds_layer= 93 /gds_type= 0 /geom_layer="ind_minus";

hipex layer /gds_layer= 94 /gds_type= 0 /geom_layer="NR_counter";

hipex layer /gds_layer= 95 /gds_type= 0 /geom_layer="width";

hipex layer /gds_layer= 96 /gds_type= 0 /geom_layer="space";

hipex layer /gds_layer= 97 /gds_type= 0 /geom_layer="radius";

hipex layer /gds_layer= 98 /gds_type=255 /geom_layer="connect_metal1";

hipex layer /gds_layer= 99 /gds_type= 0 /text_layer="$$HPX$PORT$METAL1";

hipex layer /gds_layer= 100 /gds_type= 0 /text_layer="$$HPX$PORT$METAL2";

hipex layer /gds_layer= 101 /gds_type= 0 /text_layer="$$HPX$INET$METAL1_port";

hipex layer /gds_layer= 102 /gds_type= 0 /text_layer="$$HPX$INET$GC_port";

hipex layer /gds_layer= 103 /gds_type= 0 /geom_layer="HPX$npn_e";

! TEXT TYPES

! PORT LAYERS

hipex port_layer "$$HPX$PORT$METAL1";

hipex port_layer "$$HPX$PORT$METAL2";

hipex port_layer "M1_LABEL";

hipex port_layer "M2_LABEL";

! SOFT LAYERS

! MISC (optional) statementsS

! CONNECTIVITY

hipex connect "ACTIVE_port" "p_sd";

hipex connect "ACTIVE_port" "n_sd";

hipex connect "ACTIVE_port" "hvpmos_d";

hipex connect "ACTIVE_port" "hvpmos_s";

hipex connect "ACTIVE_port" "hvnmos_d";

hipex connect "ACTIVE_port" "hvnmos_s";

hipex connect "DEEP_N_WELL" "deepnwell_tie";

hipex connect "GC_port" "connect_poly";

hipex attach "$$HPX$INET$GC_port" "GC_port";

hipex attach "$$HPX$PORT$METAL1" "METAL1";

hipex connect "METAL1_port" "connect_metal1";

hipex attach "M1_LABEL" "METAL1_port";

hipex attach "$$HPX$INET$METAL1_port" "METAL1_port";

hipex connect "METAL2" "METAL3" /contact="VIA2";

hipex attach "M2_LABEL" "METAL2";

hipex attach "$$HPX$PORT$METAL2" "METAL2";

hipex connect "METAL2_port" "METAL2";

hipex attach "M2_LABEL" "METAL2_port";

hipex connect "METAL3" "METAL4" /contact="VIA3";

hipex connect "METAL4" "METAL5" /contact="VIA4";

hipex connect "METAL5" "METAL6" /contact="VIA5";

hipex connect "NWEL_port" "connect_nwell";

hipex connect "PBASE" "npn_b";

hipex connect "PSUB_port" "substrate";

hipex connect "connect_metal1" "POLY2" /contact="poly2cap_con";

hipex connect "connect_metal1" "METAL2" /contact="VIA";

hipex connect "connect_metal1" "pnp_e" /contact="CONTACT";

hipex connect "connect_metal1" "pnp_c" /contact="CONTACT";

hipex connect "connect_metal1" "npn_e" /contact="CONTACT";

hipex connect "connect_metal1" "npn_b" /contact="CONTACT";

hipex connect "connect_metal1" "p_sd" /contact="CONTACT";

hipex connect "connect_metal1" "n_sd" /contact="CONTACT";

hipex connect "connect_metal1" "hvpmos_d" /contact="CONTACT";

hipex connect "connect_metal1" "hvpmos_s" /contact="CONTACT";

hipex connect "connect_metal1" "hvnmos_d" /contact="CONTACT";

hipex connect "connect_metal1" "hvnmos_s" /contact="CONTACT";

hipex connect "connect_metal1" "rpplus_pin" /contact="CONTACT";

hipex connect "connect_metal1" "connect_poly" /contact="poly_con";

hipex connect "connect_metal1" "sub_tie" /contact="CONTACT";

hipex connect "connect_metal1" "well_tie" /contact="CONTACT";

hipex connect "connect_metal1" "ind_plus";

hipex connect "connect_metal1" "ind_minus";

hipex attach "M1_LABEL" "connect_metal1";

hipex connect "connect_nwell" "well_tie";

hipex connect "deepnwell_tie" "connect_metal1" /contact="CONTACT";

hipex connect "ind_minus";

hipex connect "ind_plus";

hipex connect "substrate" "sub_tie";

! DEVICES TEXTS

! DEVICE DEFINITIONS

hipex define_device PMOS "cmosp_id" /drain="p_sd" /gate="connect_poly" /source="p_sd" /subs="connect_nwell" /model_name="CMOSP";

hipex define_device NMOS "cmosn_id" /drain="n_sd" /gate="connect_poly" /source="n_sd" /subs="substrate" /model_name="CMOSN";

hipex define_device C "p1p2_id" /pin1="POLY2" /pin2="connect_poly" /area_cap=0.0075 /perim_cap=0.00625 /model_name="PIPCAP";

hipex define_device PMOS "hvcmosp_id" /drain="hvpmos_d" /gate="connect_poly" /source="hvpmos_s" /subs="DEEP_N_WELL" /model_name="HVCMOSP";

hipex define_device NMOS "hvcmosn_id" /drain="hvnmos_d" /gate="connect_poly" /source="hvnmos_s" /subs="substrate" /model_name="HVCMOSN";

hipex define_device NPN "HPX$npn_e" /collector="connect_nwell" /base="PBASE" /emitter="npn_e" /subs="substrate" /area_unit=36 /model_name="NPN";

hipex define_device PNP "pnp_id" /collector="pnp_c" /base="connect_nwell" /emitter="pnp_e" /area_unit=38.3819 /model_name="PNP";

hipex define_device R "rnwell_id" /pin1="connect_nwell" /pin2="connect_nwell" /subs="substrate" /cont_res=0 /delta_l=0.4 /delta_w=-0.02 /head_res=0 /sheet_res=10000 /model_name="RNWELL" /netlist_prefix="X";

hipex define_device R "rpplus_id" /pin1="rpplus_pin" /pin2="rpplus_pin" /subs="connect_nwell" /cont_res=0 /delta_l=0.5 /delta_w=-0.05 /head_res=0 /sheet_res=200 /model_name="RPPLUS" /netlist_prefix="X";

hipex define_device R "rnpoly_id" /pin1="connect_poly" /pin2="connect_poly" /cont_res=0 /delta_l=0.4 /delta_w=0.02 /head_res=0 /sheet_res=50 /model_name="RNPOLY";

hipex define_device R "rpoly_id" /pin1="connect_poly" /pin2="connect_poly" /cont_res=0 /delta_l=0.4 /delta_w=0.02 /head_res=0 /sheet_res=50 /model_name="RPOLY";

hipex generic_device "ind_id" /pins=({{"ind_minus", "MINUS"}, {"ind_plus", "PLUS"}}) /auxs={"NR_counter", "width", "space", "radius"} /by_net /func="IND" /element_name="CUSTOM_SUBCKT" /subckt_filename="" /model_name="IND";

Include("/home/alexa/2020_06/07/hipex/hpx_examples_007.lisa");

! GEOMETRICAL OPERATIONS

hipex copy "npn_e" "HPX$npn_e";

! SOFT/WELL CHECKS

! MASKED DIELECTRIC LAYERS

hpx_ex_007_opt.lisa

!--------------------------------------------------------------------

!Run file

!DESIGN : design

!TECHNO : techno

!USER :

!TIME : Fri May 29 01:06:06 2020

!--------------------------------------------------------------------

TOP_CELL = "vref";

HIPEX_DB_DIRECTORY = "database";

!--------------------------------------------------------------------

!Extraction: LISA template command file

!--------------------------------------------------------------------

!--------------------------------------------------------------------

!Layout parameters

!--------------------------------------------------------------------

HIPEX_LAYOUT_FORMAT = "GDS";

HIPEX_LAYOUT_FILE = "vref$HPX.gds";

HIPEX_OVERLAP_INSTANCE_CHECK = "NO";

HIPEX_SUPPRESS_NOTEMPTY = "YES";

HIPEX_NON45_FLAG = "NO";

!--------------------------------------------------------------------

!Connectivity parameters

!--------------------------------------------------------------------

HIPEX_TERNARY_CONNECT_THROUGH_TOUCH = "NO";

!--------------------------------------------------------------------

!Output parameters

!--------------------------------------------------------------------

HIPEX_COMMENT_MODEL = "NO";

HIPEX_COMMENT_TOP_SUBCKT = "NO";

HIPEX_HIER_SPICE_WL_NAME = "/home/alexa/2020_06/07/vref_hier.spice";

HIPEX_MOSFET_LW_ONLY = "NO";

HIPEX_MOSFET_EXCLUDE_W_SD = "NO";

HIPEX_OUTPUT_SPICE_ATTRIBUTES = "YES";

HIPEX_CAP_OUTPUT_LW = "NO";

HIPEX_RES_OUTPUT_LW = "YES";

HIPEX_CAP_OUTPUT_AREA_PERIMETER = "YES";

HIPEX_OUTPUT_SPICE_FORMAT = "HSPICE";

HIPEX_PININFO = "NO";

HIPEX_PRINT_MESSAGES = "NO";

NETLIST_OUTPUT_PM = "NO";

NETLIST_DISTRIBUTION_MODE = "ACCURATE";

NETLIST_LINE_LENGTH = 80;

NETLIST_EXCLUDE_LIBRARY_PREFIX = "NO";

NETLIST_GLOBALS_IN_SUBCKT_PINS = "YES";

NETLIST_TEXTED_PINS = "YES";

NETLIST_LIBRARIES = {};

!--------------------------------------------------------------------

!ERC parameters

!--------------------------------------------------------------------

HIPEX_DANGLE_FLAG = "YES";

HIPEX_CAP_MESSAGE = "NO";

HIPEX_DIODE_MESSAGE = "NO";

HIPEX_RENAME_OPENS = "NO";

HIPEX_MULTILABEL_NAME = "";

HIPEX_SOFTCHECK_WARNINGS_AS_ERRORS = "NO";

!--------------------------------------------------------------------

!Node Name parameters

!--------------------------------------------------------------------

HIPEX_HIERARCHY_SEPARATOR = "/";

HIPEX_NODE_NAME_SEPARATOR = "_";

HIPEX_DEFAULT_INSTANCE_PREFIX = "I";

HIPEX_DEFAULT_NODE_PREFIX = "#";

HIPEX_DELETE_BAD_CHAR = "NO";

HIPEX_XY_LOCATION = "NO";

HIPEX_CASE_SENSITIVE_NET_NAMES = "YES";

HIPEX_AUTOGENERATE_LOCAL = "YES";

POWER_NODE = {"VDD"};

GROUND_NODE = {"VSS"};

GLOBAL_TEXT_LIST = {"VDD", "VSS"};

HIPEX_PIN_DELIMITER = ":";

!--------------------------------------------------------------------

!Explosion parameters

!--------------------------------------------------------------------

HIPEX_WIRING_EXPLODE = "NO";

HIPEX_KEEP_FLATTEN_CELLS = "YES";

HIPEX_TEXT_TOP = "NO";

HIPEX_AUTO_EXPLODE = "NO";

HIPEX SET_CELL_OPTIONS {"contact_9_qtldiz"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"RPPLUS_10_134_2680_1_134_6lzsa6"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"ntub_tie_10_f0oav3"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"sub_tie_10_wfndn"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"RPPLUS_10_135_2700_1_135_qhqlrr"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"RPPLUS_10_690_13800_3_230_n4hg94"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"NPN"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"contact_48_sj1nnm"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"contact_3_qtldit"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"CMOSP_100_25_2_TRUE_On_xviejz"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"M1_POLY1_20000_20000_1_1_40000_40000_4"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"M1_M2_20000_20000_4_1_50000_50000_4"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"M1_M2_20000_20000_2_1_50000_50000_4"} /EXPLODE;

HIPEX SET_CELL_OPTIONS {"vref"} /EXPLODE;

!--------------------------------------------------------------------

!Pins parameters

!--------------------------------------------------------------------

HIPEX_IGNORE_DANGLE_PINS = "NO";

!--------------------------------------------------------------------

!BackAnnotate parameters

!--------------------------------------------------------------------

HIPEX_BACKANNOTATE = "YES";

HIPEX_SCHEMATIC_FILE = "/home/alexa/2020_06/07/vref_lvs.net";

HIPEX_BACKANNOTATE_MAP_FILE = "/home/alexa/2020_06/07/vref_ba.map";

HIPEX_LVS_PROJECT_FILE = "/home/alexa/2020_06/07/default.gpr";

!--------------------------------------------------------------------

!Capacitance Extraction parameters

!--------------------------------------------------------------------

CPX_COUPLED_THRESHOLD = 0.0;

CPX_EXTRACT_DANGLES = "NO";

CPX_OUTPUT_DUMMY_CAPA = "NO";

CPX_FIELD_SOLVER = "NO";

!--------------------------------------------------------------------

!Field Solver C-extraction (Stellar) parameters

!--------------------------------------------------------------------

CPX_STEP_X = 0.5;

CPX_STEP_Y = 0.5;

CPX_STEP_Z = 0.5;

CPX_PRECISION = 0.01;

CPX_MAX_ITER = 100;

CPX_DECOMPOSITION = "YES";

CPX_DEC_STEP = "NO";

CPX_DEC_VALUE = -1.0;

CPX_BOX = "NO";

CPX_BOX_VALUES_XMIN = 0.0;

CPX_BOX_VALUES_XMAX = 0.0;

CPX_BOX_VALUES_YMIN = 0.0;

CPX_BOX_VALUES_YMAX = 0.0;

CPX_FILTER = "NO";

CPX_CAPA_MIN = 1e-20;

CPX_RENEW = "NO";

CPX_SAVE_FILE = "/home/alexa/2020_06/07/RenewSavedFile.sav";

CPX_THREED_GENERATION = "NO";

CPX_THREED_FILENAME = "/home/alexa/2020_06/07/3DStructureFile.str";

!--------------------------------------------------------------------

!Field Solver C-extraction (Clever) parameters

!--------------------------------------------------------------------

!--------------------------------------------------------------------

!Resistance Extraction parameters

!--------------------------------------------------------------------

RPX_SERIAL_MERGE_THRESHOLD = 0.0;

RPX_OUTPUT_XY = "YES";

RPX_OUTPUT_LAYER_NAMES = "YES";

RPX_SKIP_POWER = "YES";

RPX_USE_TEXTS_AS_SUBNODES = "NO";

RPX_USE_FIELD_SOLVER = "NO";

!--------------------------------------------------------------------

!Netlist RC Reduction parameters

!--------------------------------------------------------------------

NETLIST_CRC = "NO";

!--------------------------------------------------------------------

!Coefficient Units parameters

!--------------------------------------------------------------------

HIPEX SET_UNIT /CAPACITANCE "pF";

HIPEX SET_UNIT /RESISTANCE "Ohm";

HIPEX SET_UNIT /LENGTH "um";

run_c.lisa

INCLUDE ("hpx_ex_007_opt.lisa");

INCLUDE ("hpx_ex_007_net_cmd.lisa");

INCLUDE ("../hipex/hpx_examples_007_c.lisa");

HIPEX_SUMMARY_PATH = "/home/alexa/2020_06/07";

HDB READ;

print("Writing Stripe Database ...");

HDB WRITE_STRIPES /FULL "default" 200 10;

print("Stripes OK.");

CPX MAIN "default" /rewrite;

netlist spice/hier/c/ba "/home/alexa/2020_06/07/vref_c_hier.spice";

run_net.lisa

INCLUDE ("hpx_ex_007_opt.lisa");

INCLUDE ("hpx_ex_007_net_cmd.lisa");

HIPEX_SUMMARY_PATH = "/home/alexa/2020_06/07";

HIPEX_NET_MAIN();

HDB READ;

hdb backannotate "/home/alexa/2020_06/07/vref_lvs.net" "/home/alexa/2020_06/07/default.gpr";

netlist spice/hier/ba "/home/alexa/2020_06/07/vref_hier.spice";

run_rc.lisa

INCLUDE ("hpx_ex_007_opt.lisa");

INCLUDE ("hpx_ex_007_net_cmd.lisa");

INCLUDE ("../hipex/hpx_examples_007_r.lisa");

INCLUDE ("../hipex/hpx_examples_007_c.lisa");

HIPEX_SUMMARY_PATH = "/home/alexa/2020_06/07";

HDB READ;

print("Writing Stripe Database ...");

HDB WRITE_STRIPES /FULL/BA/SELECT/NETS="NET6","NET8","VOUT" "default" 200 10;

print("Stripes OK.");

print("Parasitic capacitance extraction...");

CPX MAIN "default" /rewrite;

print("Parasitic resistance extraction...");

RPX MAIN "default" /rewrite;

netlist spice/hier/rc/ba "/home/alexa/2020_06/07/vref_rc_hier.spice";

hpx_examples_007.tcn

TechnologyID = "Silvaco BCD (analog demo PDK)"

Version = 101

Unit = "um"

UnitValue = 1

Shapes

{

AllowOffGridWire = TRUE

AllowOffGridEllipse = TRUE

ApproximationType = POINTS

ApproximationValue = 50

AlignedY = FALSE

Circumscribed = FALSE

}

Layer

{

Name = "N_WELL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 2

}

CIFName = "CWN"

Stipple = "32"

Bitmap = "000000000800000008000000020000000100010088000000220000008800000022000000"

Color = (0,0,197)

GDS2Num = 42

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

Processing

{

DesignLayer = FALSE

Planar = FALSE

ProcessingStep = 1

Operation = 3

StepCoverage = 0

Undercut = 0

Angle = 90

}

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "NWEL_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 42

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "P_WELL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CWC"

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (255,255,0)

GDS2Num = 59

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "PSUB_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 59

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "ACTIVE_port"

Wire

{

MiterAngle = 20

Width = 2.5

Joint = MITER

End = BUTT

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 1

}

CIFName = "CAA"

Stipple = "0void"

Bitmap = "000000000800000008000000020000000100010000000000000000000000000000000000"

Color = (170,0,255)

GDS2Num = 43

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "ACTIVE"

Wire

{

MiterAngle = 20

Width = 2.5

Joint = MITER

End = BUTT

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 1

}

CIFName = "CAA"

Stipple = "0void"

Bitmap = "000000000800000008000000020000000100010000000000000000000000000000000000"

Color = (170,0,255)

GDS2Num = 43

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "THICK_ACTIVE"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CTA"

Stipple = "STP_H_DIAGCROSS"

Color = (255,0,0)

GDS2Num = 60

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "PBASE"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CBA"

Stipple = "STP_H_DENSE7"

Color = (255,0,127)

GDS2Num = 58

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "POLY_CAP1"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CPC"

Stipple = "blank"

Color = (149,106,74)

GDS2Num = 28

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "POLY"

Wire

{

MiterAngle = 20

Width = 2

Joint = MITER

End = BUTT

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 1

}

CIFName = "CPG"

Stipple = "0ckbrd_1~"

Bitmap = "0000000008000000080000000200000001000100AA005500AA005500AA005500AA005500"

Color = (255,0,0)

GDS2Num = 46

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

Processing

{

DesignLayer = FALSE

Planar = FALSE

ProcessingStep = 4

Operation = 1

StepCoverage = 0

Undercut = 0

Angle = 90

}

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "POLY_LABEL"

Wire

{

MiterAngle = 20

Width = 2

Joint = MITER

End = BUTT

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 1

}

CIFName = "CPG"

Stipple = "0ckbrd_1~"

Bitmap = "0000000008000000080000000200000001000100AA005500AA005500AA005500AA005500"

Color = (255,0,0)

GDS2Num = 46

GDS2DataType = 1

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "GC_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 46

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "SILICIDE_BLOCK"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CSB"

Stipple = "0void"

Bitmap = "000000000800000008000000020000000100010000000000000000000000000000000000"

Color = (255,0,0)

GDS2Num = 29

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "N_PLUS_SELECT"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 0.5

}

CIFName = "CSN"

Stipple = "32"

Bitmap = "000000000800000008000000020000000100010088000000220000008800000022000000"

Color = (0,170,0)

GDS2Num = 45

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "P_PLUS_SELECT"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 0.5

}

CIFName = "CSP"

Stipple = "32"

Bitmap = "000000000800000008000000020000000100010088000000220000008800000022000000"

Color = (170,85,0)

GDS2Num = 44

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "POLY2"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 1

}

CIFName = "CEL"

Stipple = "0ckbrd_1"

Bitmap = "00000000080000000800000002000000010001005500AA005500AA005500AA005500AA00"

Color = (151,158,170)

GDS2Num = 56

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

Processing

{

DesignLayer = FALSE

Planar = FALSE

ProcessingStep = 10

Operation = 1

StepCoverage = 0

Undercut = 0

Angle = 90

}

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "HI_RES_IMPLANT"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CHR"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 34

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "CONTACT"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 1

}

CIFName = "CCC"

Stipple = "0solid"

Bitmap = "0000000008000000080000000200000001000100FF00FF00FF00FF00FF00FF00FF00FF00"

Color = (188,182,205)

GDS2Num = 25

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

Processing

{

DesignLayer = FALSE

Planar = FALSE

ProcessingStep = 13

Operation = 2

StepCoverage = 0

Undercut = 0

Angle = 95

}

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL1"

Wire

{

MiterAngle = 20

Width = 3

Joint = MITER

End = BUTT

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 1.5

}

CIFName = "CM1"

Stipple = "26"

Bitmap = "0000000008000000080000000200000001000100AA005500AA005500AA005500AA005500"

Color = (0,170,255)

GDS2Num = 49

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

Processing

{

DesignLayer = FALSE

Planar = TRUE

ProcessingStep = 15

Operation = 1

StepCoverage = 0

Undercut = 0

Angle = 90

}

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL1_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 49

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "M1_LABEL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "0void"

Bitmap = "000000000800000008000000020000000100010000000000000000000000000000000000"

Color = (255,0,0)

GDS2Num = 49

GDS2DataType = 1

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "VIA"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 2

}

CIFName = "CV1"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 50

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

Processing

{

DesignLayer = FALSE

Planar = FALSE

ProcessingStep = 18

Operation = 2

StepCoverage = 0

Undercut = 0

Angle = 95

}

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL2"

Wire

{

MiterAngle = 20

Width = 3

Joint = MITER

End = BUTT

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 2

}

CIFName = "CM2"

Stipple = "STP_H_DENSE2"

Color = (255,85,255)

GDS2Num = 51

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

Processing

{

DesignLayer = FALSE

Planar = TRUE

ProcessingStep = 19

Operation = 1

StepCoverage = 0

Undercut = 0

Angle = 90

}

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL2_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 51

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "M2_LABEL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = 51

GDS2DataType = 1

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "VIA2"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CV2"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 61

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL3"

Wire

{

MiterAngle = 20

Width = 6

Joint = MITER

End = BUTT

}

CIFName = "CM3"

Stipple = "STP_H_DENSE5"

Color = (223,228,27)

GDS2Num = 62

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL3_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 62

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "M3_LABEL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = 62

GDS2DataType = 1

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "VIA3"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CV3"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 30

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL4"

Wire

{

MiterAngle = 20

Width = 6

Joint = MITER

End = BUTT

}

CIFName = "CM4"

Stipple = "blank"

Color = (207,155,46)

GDS2Num = 31

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL4_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 31

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "M4_LABEL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = 31

GDS2DataType = 1

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "CAP_TOP_METAL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CTM"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 35

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "VIA4"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CV4"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 32

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL5"

Wire

{

MiterAngle = 20

Width = 6

Joint = MITER

End = BUTT

}

CIFName = "CM5"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 33

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL5_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 33

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "M5_LABEL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = 33

GDS2DataType = 1

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "VIA5"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CV5"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 36

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL6"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CM6"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 37

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "METAL6_port"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = 37

GDS2DataType = 5

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "M6_LABEL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = 37

GDS2DataType = 1

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "DEEP_N_WELL"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CDNW"

Stipple = "STP_H_DENSE3"

Color = (0,0,100)

GDS2Num = 38

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "GLASS"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "COG"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 52

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "PADS"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XP"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = 26

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "Comments"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "CX"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "RES_ID"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = 1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "INDDMY_ID"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (255,0,0)

ColorName = "0"

GDS2Num = 2

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = FALSE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "pnp_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "pnp_e"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "pnp_c"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "npn_e"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "npn_b"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "gate"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "0void"

Bitmap = "000000000800000008000000020000000100010000000000000000000000000000000000"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "p_sd"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "0solid"

Bitmap = "0000000008000000080000000200000001000100FF00FF00FF00FF00FF00FF00FF00FF00"

Color = (85,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "n_sd"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "0solid"

Bitmap = "0000000008000000080000000200000001000100FF00FF00FF00FF00FF00FF00FF00FF00"

Color = (0,170,127)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "cmosp_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "26"

Bitmap = "0000000008000000080000000200000001000100AA005500AA005500AA005500AA005500"

Color = (131,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "cmosn_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "26"

Bitmap = "0000000008000000080000000200000001000100AA005500AA005500AA005500AA005500"

Color = (170,255,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "hvcmosp_id"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "STP_H_FDIAG"

Color = (255,0,0)

ColorName = "0"

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "hvpmos_d"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "hvpmos_s"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "hvcmosn_id"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "STP_H_FDIAG"

Color = (0,170,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "hvnmos_d"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "hvnmos_s"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "rpplus_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "rnpoly_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "rpoly_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "rnwell_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "rpplus_pin"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (170,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "connect_poly"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "connect_nwell"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "substrate"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Material

{

Resistivity = -1

Permittivity = -1

Thickness = 0.5

}

CIFName = "XXXX"

Stipple = "0void"

Bitmap = "000000000800000008000000020000000100010000000000000000000000000000000000"

Color = (255,255,255)

GDS2Num = -1

GDS2DataType = 0

Derive = "

Substrate: LayerR=substrate;

"

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "sub_tie"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "STP_H_DENSE4"

Color = (255,255,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "well_tie"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "blank"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "deepnwell_tie"

Wire

{

MiterAngle = 20

Width = 1

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "p1p2_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "poly_con"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "poly2cap_con"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

CIFName = "XXXX"

Stipple = "blank"

Bitmap = "000000000800000008000000020000000100010001000200040008001000200040008000"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "ind_id"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "blank"

Color = (0,0,255)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{

Name = "ind_plus"

Wire

{

MiterAngle = 20

Width = 0

Joint = EXTEND

End = EXTEND

}

Stipple = "STP_H_SOLID"

Color = (255,0,0)

GDS2Num = -1

GDS2DataType = 0

Scope = FLAT

UseGridParams = FALSE

ScratchLayer = TRUE

EdgeLayer = FALSE

LineStyle = 0

}

Layer

{