05 : Hipex DSPF/SPEF Parasitic Extraction

Minimum Required Versions: Expert 5.2204.3.R, Hipex 3.8.7.R

This example demonstrates running Hipex Parasitic Extraction on a layout in the Expert interactive layout environment, with output in DSPF/SPEF format

1: Setting up Parasitic Extraction in Expert

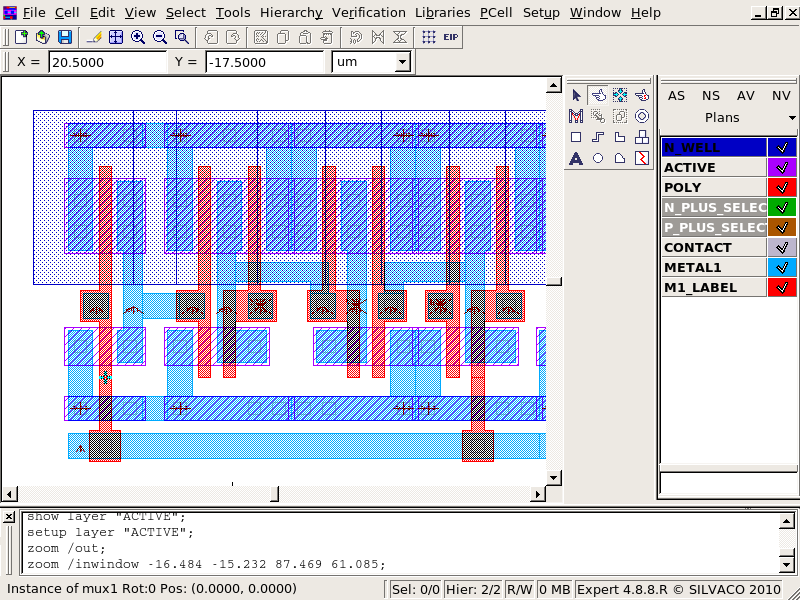

First start the Expert layout editor program, either with the command expert or by clicking the expert icon. From the main menu bar at the top, click File --> Open to pop up the Load Project menu, navigate to the directory into which the hipex_ex05.eld design database file was downloaded and Open it. This will call up the Open Cell(s) menus, and here double-click mux4 , the top-level cell. By default this shows the hierarchical view of the design; you can see the full details by clicking View --> Cell View --> Flat (see figure1 ).

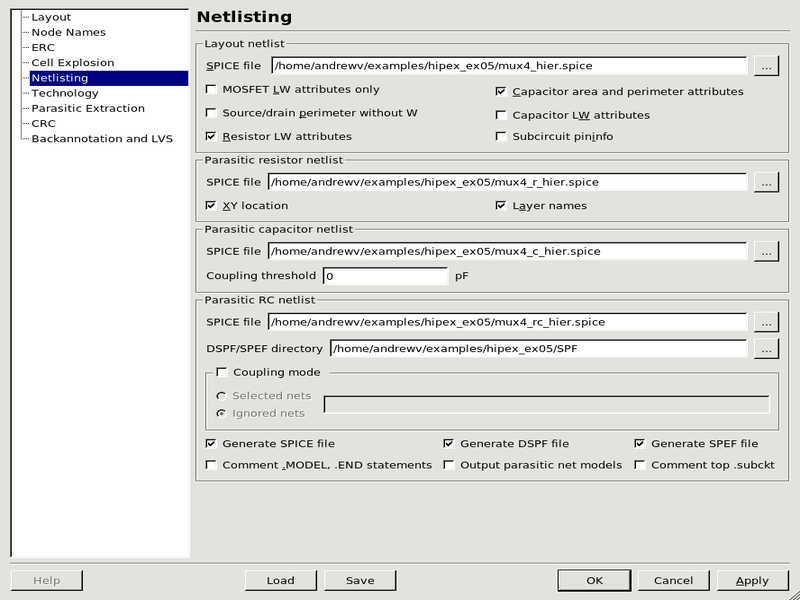

The next step is to load the required Hipex technology files and change any settings to customize the extraction. From the main Expert menu, click Verification --> Extraction --> Setup ; this pops up the Layout Parameter Extraction Setup panel. The pages within this panel are accessed using the menu on the left (see figure2 with Netlisting page shown)

The first page Layout shows the Database file and Top cell; by default these are set to the currently open database and cell. The second page, Node Names , controls how instance and net names are derived. Specifying Global node names (eg, VSS for Ground) will cause those names to be declared as *.GLOBAL in the extracted netlist.

The fourth page, Cell Explosion , controls the extraction of the design hierarchy. The default is to EXPLODE all cells, which has the effect of producing a flat netlist in this simple example; to create a fully hierarchical netlist, click Set all --> Hcell.

The fifth page, Netlisting, controls the details of the extracted netlists and parasitic files which will be generated. Default filenames for all the possible types of output are generated based of the current design/cell. In the final section for Parasitic RC netlist you can select the output netlist format; the standard SPICE format is enabled by default, but you can also enable DSPF and SPEF formats for digital timing or STA back-annotation. You may select any of the formats simultaneously.

The sixth page, Technology , is where you need to specify the technology files for the extractions. For Derived layer generation , select Use external script and use the file browser to specify the hipex_ex05_lvs.dsf file previously downloaded. This file controls the generation of device recognition layers from the drawn/mask layers. To do a parasitic capacitance or RC extraction, you must select Use external LISA script in the Parasitic capacitance technology section and use the file browser to specify the hipex_ex05_c.lisa file previously downloaded. To do a parasitic resistance or RC extraction, you must select Use external LISA script in the Parasitic resistance technology section and use the file browser to specify the hipex_ex05_r.lisa file previously downloaded.

The seventh page, Parasitic Extraction provides more advanced settings. For parasitic resistance extraction it allows you to specify a resistance serial merge threshold to prevent the listing of tiny resistors in the netlist. Any parasitic resistor of smaller value than the threshold will merge with a neighboring resistor if possible. Additionally the user can specify that parasitic resistors for power nets be ignored (Ignore power node).

When you have completed all required pages, click OK in the Layout Parameter Extraction Setup Panel

2: Parasitic Extraction

The netlist extraction can now be run, with Verification --> Extraction --> Hipex-Net --> Run from the main Expert window. This step is necessary even if only the parasitics are required, because the full connectivity must first be extracted to identify all the nodes.

After the netlist extraction has been done, it is now possible to continue to parasitic (R, C, or RC) extraction. These are run in almost exactly the same way as the Hipex-Net extraction with the commands from the main Expert window.

For parasitic capacitance extraction: Verification --> Extraction --> Hipex-C --> Run

For parasitic distributed RC extraction: Verification --> Extraction --> Hipex-RC --> Run

The progress panel, which these runs pop up, give you the option to open the netlist in the interactive Netlist Editor: This is only relevant to the spice netlist format; the DSPF/SPEF formats are only parasitic netlists and cannot support probing of the normal devices. The DSPF/SPEF netlists can instead be viewed from a separate menu entry, eg. Verification --> Extraction --> Hipex-RC --> View DSFP Netlist ( figure3 ). The DSPF/SPEF netlists will be placed in an SPF subdirectory, or as set in the Netlisting setup page.

Note that the normal mode for DSPF/SPEF file generation is full RC (as opposed to R or C). However it is also possible to generate an C-only DSPF/SPEF file. To do this, you must delete any RC databases; the simplest way to do this is to delete the database/cdb and database/rdb directories from *.xwd directory. Then run Hipex-C , and finally run the DSPF and/or SPEF netlister Verification->Extraction->Netlister->DSPF Netlist or Verification->Extraction->Netlister->SPEF Netlist. ( figure4 ).

hipex_ex05_net_cmd.lisa

!--------------------------------------------------------------------

!Net command file

!DESIGN : design

!TECHNO : techno

!USER :

!TIME : Fri May 29 22:35:21 2020

!--------------------------------------------------------------------

! HIPEX to CUP map table

cup layer "metal4" /hipex_layer="METAL4";

cup layer "metal5" /hipex_layer="METAL5";

cup layer "metal6" /hipex_layer="METAL6";

cup layer "metal2" /hipex_layer="METAL2";

cup layer "metal3" /hipex_layer="METAL3";

cup layer "poly1" /hipex_layer="connect_poly";

cup layer "substrate" /hipex_layer="substrate";

cup layer "metal1" /hipex_layer="connect_metal1";

! GDS LAYER MAP

hipex layer /gds_layer= 0 /gds_type= 0 /geom_layer="pnp_id";

hipex layer /gds_layer= 25 /gds_type= 0 /geom_layer="CONTACT";

hipex layer /gds_layer= 30 /gds_type= 0 /geom_layer="VIA3";

hipex layer /gds_layer= 31 /gds_type= 0 /geom_layer="METAL4";

hipex layer /gds_layer= 31 /gds_type= 6 /geom_layer="METAL4_port_text" /text_layer="METAL4_port_text_HPX_TEXT";

hipex layer /gds_layer= 32 /gds_type= 0 /geom_layer="VIA4";

hipex layer /gds_layer= 33 /gds_type= 0 /geom_layer="METAL5";

hipex layer /gds_layer= 33 /gds_type= 6 /geom_layer="METAL5_port_text" /text_layer="METAL5_port_text_HPX_TEXT";

hipex layer /gds_layer= 36 /gds_type= 0 /geom_layer="VIA5";

hipex layer /gds_layer= 37 /gds_type= 0 /geom_layer="METAL6";

hipex layer /gds_layer= 37 /gds_type= 6 /geom_layer="METAL6_port_text" /text_layer="METAL6_port_text_HPX_TEXT";

hipex layer /gds_layer= 38 /gds_type= 0 /geom_layer="DEEP_N_WELL";

hipex layer /gds_layer= 42 /gds_type= 5 /geom_layer="NWEL_port";

hipex layer /gds_layer= 46 /gds_type= 5 /geom_layer="GC_port";

hipex layer /gds_layer= 49 /gds_type= 1 /text_layer="M1_LABEL";

hipex layer /gds_layer= 49 /gds_type= 5 /geom_layer="METAL1_port";

hipex layer /gds_layer= 49 /gds_type= 6 /geom_layer="METAL1_port_text" /text_layer="METAL1_port_text_HPX_TEXT";

hipex layer /gds_layer= 50 /gds_type= 0 /geom_layer="VIA";

hipex layer /gds_layer= 51 /gds_type= 0 /geom_layer="METAL2";

hipex layer /gds_layer= 51 /gds_type= 1 /geom_layer="M2_LABEL";

hipex layer /gds_layer= 51 /gds_type= 5 /geom_layer="METAL2_port";

hipex layer /gds_layer= 51 /gds_type= 6 /geom_layer="METAL2_port_text" /text_layer="METAL2_port_text_HPX_TEXT";

hipex layer /gds_layer= 56 /gds_type= 0 /geom_layer="POLY2";

hipex layer /gds_layer= 58 /gds_type= 0 /geom_layer="PBASE";

hipex layer /gds_layer= 59 /gds_type= 5 /geom_layer="PSUB_port";

hipex layer /gds_layer= 61 /gds_type= 0 /geom_layer="VIA2";

hipex layer /gds_layer= 62 /gds_type= 0 /geom_layer="METAL3";

hipex layer /gds_layer= 62 /gds_type= 6 /geom_layer="METAL3_port_text" /text_layer="METAL3_port_text_HPX_TEXT";

hipex layer /gds_layer= 63 /gds_type= 0 /geom_layer="pnp_e";

hipex layer /gds_layer= 64 /gds_type= 0 /geom_layer="pnp_c";

hipex layer /gds_layer= 65 /gds_type= 0 /geom_layer="npn_e";

hipex layer /gds_layer= 66 /gds_type= 0 /geom_layer="npn_b";

hipex layer /gds_layer= 67 /gds_type= 0 /geom_layer="p_sd";

hipex layer /gds_layer= 68 /gds_type= 0 /geom_layer="n_sd";

hipex layer /gds_layer= 69 /gds_type= 0 /geom_layer="cmosp_id";

hipex layer /gds_layer= 70 /gds_type= 0 /geom_layer="cmosn_id";

hipex layer /gds_layer= 71 /gds_type= 0 /geom_layer="hvcmosp_id";

hipex layer /gds_layer= 72 /gds_type= 0 /geom_layer="hvpmos_d";

hipex layer /gds_layer= 73 /gds_type= 0 /geom_layer="hvpmos_s";

hipex layer /gds_layer= 74 /gds_type= 0 /geom_layer="hvcmosn_id";

hipex layer /gds_layer= 75 /gds_type= 0 /geom_layer="hvnmos_d";

hipex layer /gds_layer= 76 /gds_type= 0 /geom_layer="hvnmos_s";

hipex layer /gds_layer= 77 /gds_type= 0 /geom_layer="rpplus_id";

hipex layer /gds_layer= 78 /gds_type= 0 /geom_layer="rnpoly_id";

hipex layer /gds_layer= 79 /gds_type= 0 /geom_layer="rpoly_id";

hipex layer /gds_layer= 80 /gds_type= 0 /geom_layer="rnwell_id";

hipex layer /gds_layer= 81 /gds_type= 0 /geom_layer="rpplus_pin";

hipex layer /gds_layer= 82 /gds_type= 0 /geom_layer="connect_poly";

hipex layer /gds_layer= 83 /gds_type= 0 /geom_layer="connect_nwell";

hipex layer /gds_layer= 84 /gds_type= 0 /geom_layer="substrate";

hipex layer /gds_layer= 85 /gds_type= 0 /geom_layer="sub_tie";

hipex layer /gds_layer= 86 /gds_type= 0 /geom_layer="well_tie";

hipex layer /gds_layer= 87 /gds_type= 0 /geom_layer="deepnwell_tie";

hipex layer /gds_layer= 88 /gds_type= 0 /geom_layer="p1p2_id";

hipex layer /gds_layer= 89 /gds_type= 0 /geom_layer="poly_con";

hipex layer /gds_layer= 90 /gds_type= 0 /geom_layer="poly2cap_con";

hipex layer /gds_layer= 91 /gds_type= 0 /geom_layer="ind_plus";

hipex layer /gds_layer= 92 /gds_type= 0 /geom_layer="ind_minus";

hipex layer /gds_layer= 93 /gds_type=255 /geom_layer="connect_metal1";

hipex layer /gds_layer= 94 /gds_type= 0 /geom_layer="HPX$npn_e";

! TEXT TYPES

! PORT LAYERS

hipex port_layer "METAL1_port_text_HPX_TEXT";

copy_ "METAL1_port_text" "METAL1_port_text_HPX_PORT$";

hipex port_layer "METAL1_port_text_HPX_PORT$" {"METAL1_port_text"};

hipex port_layer "METAL2_port_text_HPX_TEXT";

copy_ "METAL2_port_text" "METAL2_port_text_HPX_PORT$";

hipex port_layer "METAL2_port_text_HPX_PORT$" {"METAL2_port_text"};

hipex port_layer "METAL3_port_text_HPX_TEXT";

copy_ "METAL3_port_text" "METAL3_port_text_HPX_PORT$";

hipex port_layer "METAL3_port_text_HPX_PORT$" {"METAL3_port_text"};

hipex port_layer "METAL4_port_text_HPX_TEXT";

copy_ "METAL4_port_text" "METAL4_port_text_HPX_PORT$";

hipex port_layer "METAL4_port_text_HPX_PORT$" {"METAL4_port_text"};

hipex port_layer "METAL5_port_text_HPX_TEXT";

copy_ "METAL5_port_text" "METAL5_port_text_HPX_PORT$";

hipex port_layer "METAL5_port_text_HPX_PORT$" {"METAL5_port_text"};

hipex port_layer "METAL6_port_text_HPX_TEXT";

copy_ "METAL6_port_text" "METAL6_port_text_HPX_PORT$";

hipex port_layer "METAL6_port_text_HPX_PORT$" {"METAL6_port_text"};

! SOFT LAYERS

! MISC (optional) statementsS

! CONNECTIVITY

hipex connect "DEEP_N_WELL" "deepnwell_tie";

hipex connect "GC_port" "connect_poly";

hipex connect "M2_LABEL" "ind_minus";

hipex attach "METAL1_port_text_HPX_TEXT" "METAL1_port_text";

hipex connect "METAL2" "METAL2_port_text";

hipex connect "METAL2" "METAL2_port";

hipex connect "METAL2" "METAL3" /contact="VIA2";

hipex attach "METAL2_port_text_HPX_TEXT" "METAL2";

hipex attach "METAL2_port_text_HPX_TEXT" "METAL2_port_text";

hipex connect "METAL3" "METAL3_port_text";

hipex connect "METAL3" "METAL4" /contact="VIA3";

hipex attach "METAL3_port_text_HPX_TEXT" "METAL3";

hipex attach "METAL3_port_text_HPX_TEXT" "METAL3_port_text";

hipex connect "METAL4" "METAL4_port_text";

hipex connect "METAL4" "METAL5" /contact="VIA4";

hipex attach "METAL4_port_text_HPX_TEXT" "METAL4";

hipex attach "METAL4_port_text_HPX_TEXT" "METAL4_port_text";

hipex connect "METAL5" "METAL5_port_text";

hipex connect "METAL5" "METAL6" /contact="VIA5";

hipex attach "METAL5_port_text_HPX_TEXT" "METAL5";

hipex attach "METAL5_port_text_HPX_TEXT" "METAL5_port_text";

hipex connect "METAL6" "METAL6_port_text";

hipex attach "METAL6_port_text_HPX_TEXT" "METAL6";

hipex attach "METAL6_port_text_HPX_TEXT" "METAL6_port_text";

hipex connect "NWEL_port" "connect_nwell";

hipex connect "PBASE" "npn_b";

hipex connect "PSUB_port" "substrate";

hipex connect "connect_metal1" "POLY2" /contact="poly2cap_con";

hipex connect "connect_metal1" "METAL1_port_text";

hipex connect "connect_metal1" "METAL1_port";

hipex connect "connect_metal1" "METAL2" /contact="VIA";

hipex connect "connect_metal1" "pnp_e" /contact="CONTACT";

hipex connect "connect_metal1" "pnp_c" /contact="CONTACT";

hipex connect "connect_metal1" "npn_e" /contact="CONTACT";

hipex connect "connect_metal1" "npn_b" /contact="CONTACT";

hipex connect "connect_metal1" "p_sd" /contact="CONTACT";

hipex connect "connect_metal1" "n_sd" /contact="CONTACT";

hipex connect "connect_metal1" "hvpmos_d" /contact="CONTACT";

hipex connect "connect_metal1" "hvpmos_s" /contact="CONTACT";

hipex connect "connect_metal1" "hvnmos_d" /contact="CONTACT";

hipex connect "connect_metal1" "hvnmos_s" /contact="CONTACT";

hipex connect "connect_metal1" "rpplus_pin" /contact="CONTACT";

hipex connect "connect_metal1" "connect_poly" /contact="poly_con";

hipex connect "connect_metal1" "sub_tie" /contact="CONTACT";

hipex connect "connect_metal1" "well_tie" /contact="CONTACT";

hipex connect "connect_metal1" "ind_plus";

hipex connect "connect_metal1" "ind_minus";

hipex attach "M1_LABEL" "connect_metal1";

hipex attach "METAL1_port_text_HPX_TEXT" "connect_metal1";

hipex connect "connect_nwell" "well_tie";

hipex connect "deepnwell_tie" "connect_metal1" /contact="CONTACT";

hipex connect "substrate" "sub_tie";

! DEVICES TEXTS

! DEVICE DEFINITIONS

hipex define_device PMOS "cmosp_id" /drain="p_sd" /gate="connect_poly" /source="p_sd" /subs="connect_nwell" /model_name="CMOSP";

hipex define_device NMOS "cmosn_id" /drain="n_sd" /gate="connect_poly" /source="n_sd" /subs="substrate" /model_name="CMOSN";

hipex define_device C "p1p2_id" /pin1="POLY2" /pin2="connect_poly" /area_cap=0.0075 /perim_cap=0.00625 /model_name="PIPCAP";

hipex define_device PMOS "hvcmosp_id" /drain="hvpmos_d" /gate="connect_poly" /source="hvpmos_s" /subs="DEEP_N_WELL" /model_name="HVCMOSP";

hipex define_device NMOS "hvcmosn_id" /drain="hvnmos_d" /gate="connect_poly" /source="hvnmos_s" /subs="substrate" /model_name="HVCMOSN";

hipex define_device NPN "HPX$npn_e" /collector="connect_nwell" /base="PBASE" /emitter="npn_e" /subs="substrate" /area_unit=36 /model_name="NPN";

hipex define_device PNP "pnp_id" /collector="pnp_c" /base="connect_nwell" /emitter="pnp_e" /area_unit=38.3819 /model_name="PNP";

hipex define_device R "rnwell_id" /pin1="connect_nwell" /pin2="connect_nwell" /subs="substrate" /cont_res=0 /delta_l=0.4 /delta_w=-0.02 /head_res=0 /sheet_res=10000 /model_name="RNWELL";

hipex define_device R "rpplus_id" /pin1="rpplus_pin" /pin2="rpplus_pin" /subs="connect_nwell" /cont_res=0 /delta_l=0.5 /delta_w=-0.05 /head_res=0 /sheet_res=200 /model_name="RPPLUS";

hipex define_device R "rnpoly_id" /pin1="connect_poly" /pin2="connect_poly" /cont_res=0 /delta_l=0.4 /delta_w=0.02 /head_res=0 /sheet_res=50 /model_name="RNPOLY";

hipex define_device R "rpoly_id" /pin1="connect_poly" /pin2="connect_poly" /cont_res=0 /delta_l=0.4 /delta_w=0.02 /head_res=0 /sheet_res=50 /model_name="RPOLY";

! GEOMETRICAL OPERATIONS

hipex copy "npn_e" "HPX$npn_e";

! SOFT/WELL CHECKS

! MASKED DIELECTRIC LAYERS

hipex_ex05_opt.lisa

!--------------------------------------------------------------------

!Run file

!DESIGN : design

!TECHNO : techno

!USER :

!TIME : Fri May 29 22:35:48 2020

!--------------------------------------------------------------------

TOP_CELL = "mux4";

HIPEX_DB_DIRECTORY = "database";

!--------------------------------------------------------------------

!Extraction: LISA template command file

!--------------------------------------------------------------------

!--------------------------------------------------------------------

!Layout parameters

!--------------------------------------------------------------------

HIPEX_LAYOUT_FORMAT = "GDS";

HIPEX_LAYOUT_FILE = "mux4$HPX.gds";

HIPEX_OVERLAP_INSTANCE_CHECK = "NO";

HIPEX_SUPPRESS_NOTEMPTY = "YES";

HIPEX_NON45_FLAG = "NO";

!--------------------------------------------------------------------

!Connectivity parameters

!--------------------------------------------------------------------

HIPEX_TERNARY_CONNECT_THROUGH_TOUCH = "NO";

!--------------------------------------------------------------------

!Output parameters

!--------------------------------------------------------------------

HIPEX_COMMENT_MODEL = "NO";

HIPEX_COMMENT_TOP_SUBCKT = "NO";

HIPEX_HIER_SPICE_WL_NAME = "/home/alexa/2020_06/05/mux4_hier.spice";

HIPEX_MOSFET_LW_ONLY = "NO";

HIPEX_MOSFET_EXCLUDE_W_SD = "NO";

HIPEX_OUTPUT_SPICE_ATTRIBUTES = "YES";

HIPEX_CAP_OUTPUT_LW = "NO";

HIPEX_RES_OUTPUT_LW = "YES";

HIPEX_CAP_OUTPUT_AREA_PERIMETER = "YES";

HIPEX_OUTPUT_SPICE_FORMAT = "HSPICE";

HIPEX_PININFO = "NO";

HIPEX_PRINT_MESSAGES = "NO";

NETLIST_OUTPUT_PM = "NO";

NETLIST_DISTRIBUTION_MODE = "ACCURATE";

NETLIST_LINE_LENGTH = 80;

NETLIST_EXCLUDE_LIBRARY_PREFIX = "NO";

NETLIST_GLOBALS_IN_SUBCKT_PINS = "YES";

NETLIST_TEXTED_PINS = "YES";

NETLIST_LIBRARIES = {};

!--------------------------------------------------------------------

!ERC parameters

!--------------------------------------------------------------------

HIPEX_DANGLE_FLAG = "YES";

HIPEX_CAP_MESSAGE = "NO";

HIPEX_DIODE_MESSAGE = "NO";

HIPEX_RENAME_OPENS = "NO";

HIPEX_MULTILABEL_NAME = "";

HIPEX_SOFTCHECK_WARNINGS_AS_ERRORS = "NO";

!--------------------------------------------------------------------

!Node Name parameters

!--------------------------------------------------------------------

HIPEX_HIERARCHY_SEPARATOR = "/";

HIPEX_NODE_NAME_SEPARATOR = "_";

HIPEX_DEFAULT_INSTANCE_PREFIX = "I";

HIPEX_DEFAULT_NODE_PREFIX = "#";

HIPEX_DELETE_BAD_CHAR = "NO";

HIPEX_XY_LOCATION = "NO";

HIPEX_CASE_SENSITIVE_NET_NAMES = "YES";

HIPEX_AUTOGENERATE_LOCAL = "YES";

POWER_NODE = {"VDD"};

GROUND_NODE = {"VSS"};

GLOBAL_TEXT_LIST = {"VDD", "VSS"};

HIPEX_PIN_DELIMITER = ":";

!--------------------------------------------------------------------

!Explosion parameters

!--------------------------------------------------------------------

HIPEX_WIRING_EXPLODE = "NO";

HIPEX_KEEP_FLATTEN_CELLS = "YES";

HIPEX_TEXT_TOP = "NO";

HIPEX_AUTO_EXPLODE = "NO";

!--------------------------------------------------------------------

!Pins parameters

!--------------------------------------------------------------------

HIPEX_IGNORE_DANGLE_PINS = "NO";

!--------------------------------------------------------------------

!BackAnnotate parameters

!--------------------------------------------------------------------

HIPEX_BACKANNOTATE = "NO";

!--------------------------------------------------------------------

!Capacitance Extraction parameters

!--------------------------------------------------------------------

CPX_COUPLED_THRESHOLD = 0.0;

CPX_EXTRACT_DANGLES = "NO";

CPX_OUTPUT_DUMMY_CAPA = "NO";

CPX_FIELD_SOLVER = "NO";

!--------------------------------------------------------------------

!Field Solver C-extraction (Stellar) parameters

!--------------------------------------------------------------------

CPX_STEP_X = 0.5;

CPX_STEP_Y = 0.5;

CPX_STEP_Z = 0.5;

CPX_PRECISION = 0.01;

CPX_MAX_ITER = 100;

CPX_DECOMPOSITION = "YES";

CPX_DEC_STEP = "NO";

CPX_DEC_VALUE = -1.0;

CPX_BOX = "NO";

CPX_BOX_VALUES_XMIN = 0.0;

CPX_BOX_VALUES_XMAX = 0.0;

CPX_BOX_VALUES_YMIN = 0.0;

CPX_BOX_VALUES_YMAX = 0.0;

CPX_FILTER = "NO";

CPX_CAPA_MIN = 1e-20;

CPX_RENEW = "NO";

CPX_SAVE_FILE = "/home/alexa/2020_06/05/RenewSavedFile.sav";

CPX_THREED_GENERATION = "NO";

CPX_THREED_FILENAME = "/home/alexa/2020_06/05/3DStructureFile.str";

!--------------------------------------------------------------------

!Field Solver C-extraction (Clever) parameters

!--------------------------------------------------------------------

!--------------------------------------------------------------------

!Resistance Extraction parameters

!--------------------------------------------------------------------

RPX_SERIAL_MERGE_THRESHOLD = 0.0;

RPX_OUTPUT_XY = "YES";

RPX_OUTPUT_LAYER_NAMES = "YES";

RPX_SKIP_POWER = "YES";

RPX_USE_TEXTS_AS_SUBNODES = "NO";

RPX_USE_FIELD_SOLVER = "NO";

!--------------------------------------------------------------------

!Netlist RC Reduction parameters

!--------------------------------------------------------------------

NETLIST_CRC = "NO";

!--------------------------------------------------------------------

!Coefficient Units parameters

!--------------------------------------------------------------------

HIPEX SET_UNIT /CAPACITANCE "pF";

HIPEX SET_UNIT /RESISTANCE "Ohm";

HIPEX SET_UNIT /LENGTH "um";

run_net.lisa

INCLUDE ("hipex_ex05_opt.lisa");

INCLUDE ("hipex_ex05_net_cmd.lisa");

HIPEX_SUMMARY_PATH = "/home/alexa/2020_06/05";

HIPEX_NET_MAIN();

run_rc.lisa

INCLUDE ("hipex_ex05_opt.lisa");

INCLUDE ("hipex_ex05_net_cmd.lisa");

INCLUDE ("../techfiles/hipex/hipex_ex05_r.lisa");

INCLUDE ("../techfiles/hipex/hipex_ex05_c.lisa");

HIPEX_SUMMARY_PATH = "..";

HDB READ;

print("Writing Stripe Database ...");

HDB WRITE_STRIPES /FULL "default" 200 10;

print("Stripes OK.");

print("Parasitic capacitance extraction...");

CPX MAIN "default" /append;

print("Parasitic resistance extraction...");

RPX MAIN "default" /append;

netlist spice/hier/rc "../mux4_rc_hier.spice";