17 : Use of Integration with SmartLVS for Hipex Parasitic Extraction

Minimum Required Versions: Expert 5.2307.0.R, Hipex 4.2307.0.R, SmartDRC 1.2307.0.R

Prior to performing parasitic RC extraction, Hipex executes netlist (connectivity/device) extracion. Hipex netlist extraction creates Hipex Database (HDB) serving as source of netlist-annotated geometries for RC extraction.

Alternatively to built-in netlist extractor, Hipex is capable of using extraction provided by SmartLVS program. For providing integration with Hipex, SmartLVS exports Annotated Layout Storage (ALS) in GDSII format (*_net_dump.gds file), and associated extraction rule file (*_net_dump_rule.pwr). Hipex, in turn, converts these files into HDB and Hipex technology files. This conversion enables RC-extraction and various (Spice, Dspf, etc.) netlistings.

This example shows the usage of outlined above SmartLVS-Hipex flow for parasitic extraction.

STEP-BY-STEP INSTRUCTIONS

1. Perform netlist extraction using SmartLVS

- Make sure option file (*.rcf) for launching SmartLVS contains instruction: ExtractionLayoutDBOutput:"yes" ;

- Run SmartLVS with the "lvs.rcf" file to generate annotated GDSII ("sample_layout_net_dump.gds") and PWR rule ("sample_layout_net_dump_rule.pwr") files for Hipex: smartdrc -V 1.2307.0.R lvs.rcf

2. Start Expert 5.2307.0.R with Hipex 4.2307.0.R: expert -V 5.2307.0.R -lpev:4.2307.0.R

3. Import (menu File->Import... ) the file "sample.gds" (cell "sample") without any technology. If the message "Technology file is not specified. Proceed without technology?" appears, press the "Yes" button.

4. Open LPE Setup dialog (menu Verification->Extraction->Setup... ) and load (press the "Load..." button) the file "sample_setup.lpe".(This step is optional; it only saves efforts on "manual" specifying some necessary LPE settings, mentioned below).

5. Set parameters for conversion of extraction rules from SmartLVS to Hipex and creation of HDB from annotated layout:

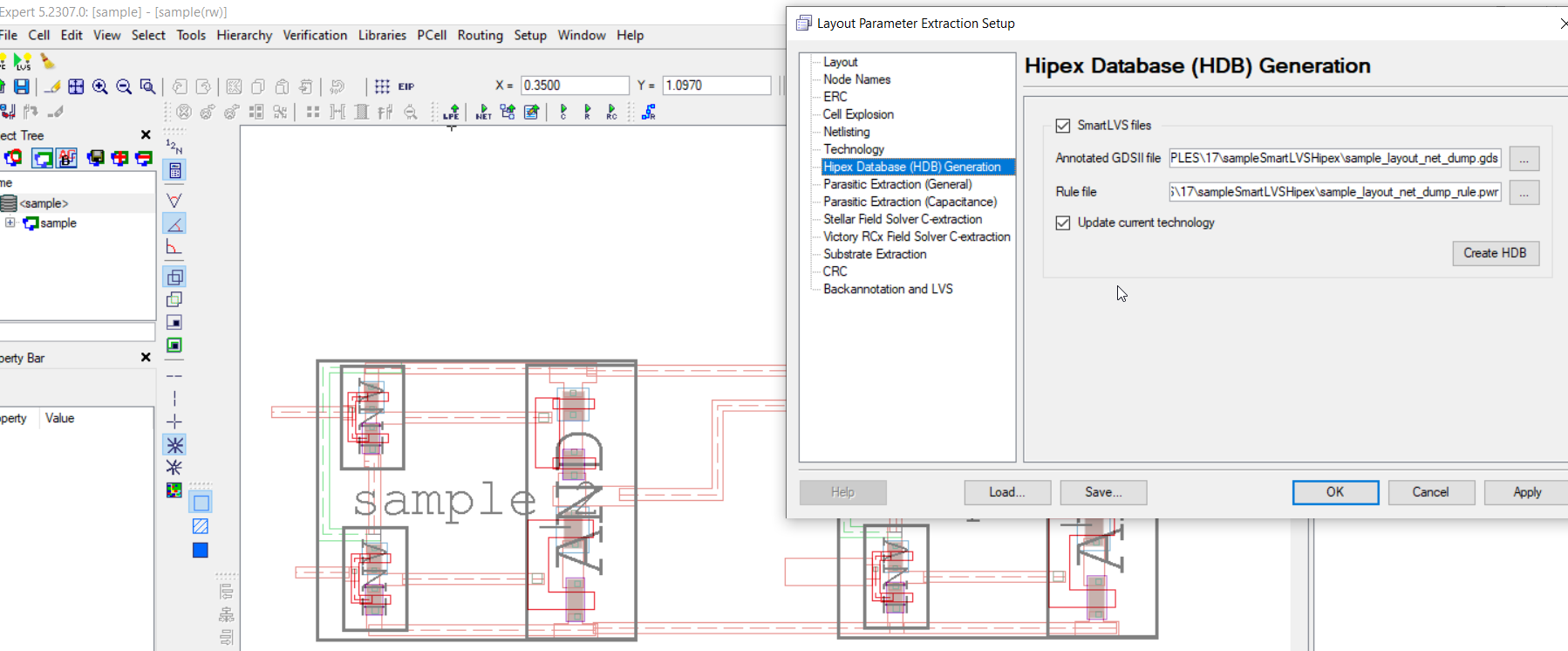

- Select "Hipex Database (HDB) Generation" page of LPE Setup dialog (see Figure1 );

- Check the SmartLVS files box;

- Choose "sample_layout_net_dump.gds" in Annotated GDSII file selector;

- Choose "sample_layout_net_dump_rule.pwr" in Rule file selector;

- (optional) check the Update current Technology box;

6. (optional) Invoke HDB build (this can be performed automatically on parasitic extraction runs):

- Press the Create HDB button ("Hipex Database Generator" dialog appears to monitor rule conversion and HDB creation);

- Upon completion of HDB generation, press the Close button to exit "Hipex Database Generator" dialog;

7. Specify rules for parasitic extraction:

- select Technology page of LPE Setup dialog;

- choose (or make sure they chosen) external scripts ("c_tech.lisa" file for capacitance technology and "r_tech.lisa" for resistance technology);

8. Specify capacitance layer mapping:

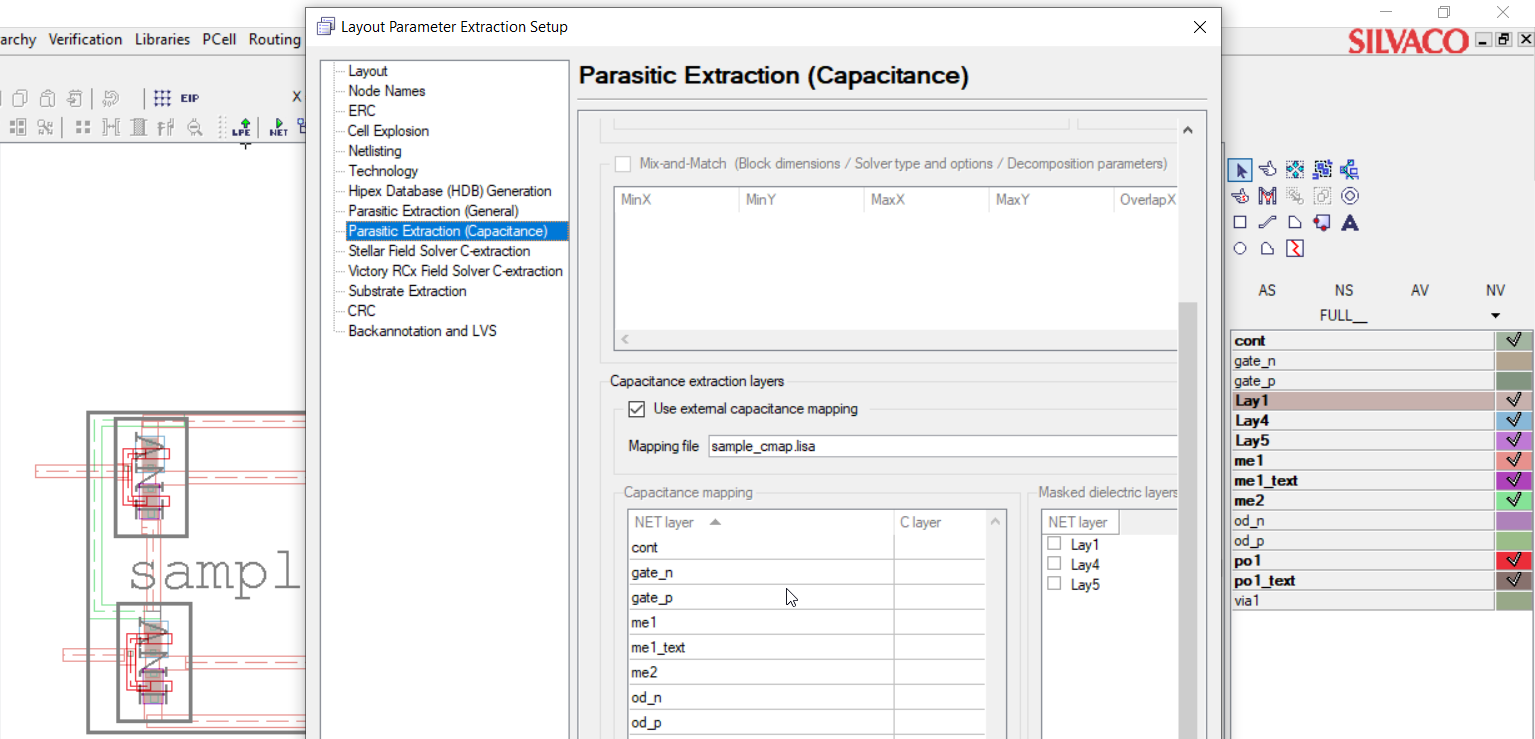

- select Parasitic Extraction (Capacitance) page of LPE Setup dialog (see Figure2 );

- check Use external capacitance mapping checkbox in Capacitance extraction layers group;

- choose (or make sure it is specified) "sample_cmap.lisa" file in Mapping file selector;

NOTE. As alternative to using external mapping file, it is possible to make manual layer assignments using Capacitance mapping table (un-checking "Use external capacitance mapping" box). However, to use this option, HDB creation (step 5) should be executed with Update current technology checkbox ON in the Hipex Database (HDB) Generation page of LPE Setup.

9. Press the "OK" button to close the LPE Setup dialog.

10. Run RC-extraction (menu Verification->Extraction->RC->Run ), or

C-extraction ( Verification->Extraction->C->Run ), or

R-extraction ( Verification->Extraction->R->Run ), or

generate extracted netlist without parasitics ( Verification->Extraction->Netlister->SPICE Netlist ).

NOTE. If HDB wasn't created (step 6 was not performed), or deleted, or obtained using old (with no SmartLVS usage) flow, the actions listed in step 10 will be automatically preceded by rule conversions and HDB (re-)creation.

lvs.rcf

ConnectNetByName: "yes"; ExtractionLayoutDBOutput: "yes"; ExtractionMapOutput: "yes"; ExtractionMode: "hier"; ExtractionNVNFullPath: "no"; ExtractionNativeCellInterface: "no"; ExtractionSkipFlatDevices: "yes"; ExtractionSpiceFileName: "sample.spo"; ExtractionSpiceOutput: "yes"; Layout: "sample.gds"; NVNRunFile: "sample_nvn.rcf"; OutputFile: ".\outfile_ext.gds"; RuleFile: "sample_ext_rule.pwr"; RunDirectory: "./"; RunName: "sample"; ShowAllErrorsFound: "yes"; TopCell: "sample"; input_format: gds; output_format: "gds";

sample_nvn.rcf

LVS

{

Schematic: spice "sample.spi";

Layout: spice "sample.spo";

TopCell : sample;

WriteLVSInfo : yes VIEWER;

CaseIgnore : no ALL;

CheckInterface : no;

CompareParameters : MOS W 0, L 0;

LayoutOneNet : vss L-vss_L018_vss_ML_1;

RunDirectory : "./";

}

sample.spi

* Copyright (c) 2009 POLYTEDA Software Corporation. All rights reserved. .SUBCKT AND and_in1 and_in2 and_out and_vdd and_vss * devices for model MN D G S * X=0.279 Y=0.200 m_MN1 and_vss and_in2 lvs_7 MN L=0.032u W=0.030u * X=0.272 Y=0.450 m_MN2 and_out and_in1 lvs_9 MN L=0.018u W=0.037u * devices for model MP D G S * X=0.274 Y=0.328 m_MP3 lvs_7 and_in2 and_out MP L=0.031u W=0.033u * X=0.272 Y=0.555 m_MP4 lvs_9 and_in1 and_vdd MP L=0.019u W=0.038u .ENDS .SUBCKT INV inv_in inv_out inv_vdd inv_vss * devices for model MN D G S * X=0.067 Y=0.058 m_MN1 inv_vss inv_in inv_out MN L=0.015u W=0.026u * devices for model MP D G S * X=0.067 Y=0.131 m_MP2 inv_out inv_in inv_vdd MP L=0.015u W=0.026u .ENDS .SUBCKT sample_2 in1 in2 out vdd vss x_AND_1 lvs_17 lvs_18 out vdd vss AND x_INV_2 in2 lvs_18 lvs_12 vss INV x_INV_3 in1 lvs_17 vdd lvs_12 INV .ENDS .SUBCKT sample in11 in12 in22 out vdd vss x_sample_2_1 in11 in12 lvs_12 vdd vss sample_2 x_sample_2_2 lvs_12 in22 out vdd vss sample_2 .ENDS

sample_ext_rule.pwr

// Copyright © 2009 POLYTEDA Software Corporation. All rights reserved.

$layer_def(gds, in, 1) {

diff = 1 type 0;

pplus = 4 type 0;

nplus = 5 type 0;

po1 = 2 type 0;

cont = 8 type 0;

me1 = 6 type 0;

me2 = 7 type 0;

via1 = 9 type 0;

me1_text = text 10 type 0;

po1_text = text 11 type 0;

}

$layer_def(gds, out, 1) {

outlayer_od = 2 type 0;

outlayer_gate = 4 type 0;

}

diff_n = diff * nplus;

diff_p = diff * pplus;

gate_n = diff_n * po1;

gate_p = diff_p * po1;

od_n = diff_n - po1;

od_p = diff_p - po1;

$connect od_n me1_text;

$connect od_p me1_text;

$connect po1 po1_text;

$connect me1 me1_text;

$connect od_n po1_text;

$connect od_p po1_text;

$connect po1 me1_text;

$connect me1 po1_text;

$connect po1 gate_n;

$connect po1 gate_p;

$connect po1 me1 $by cont;

$connect od_n me1 $by cont;

$connect od_p me1 $by cont;

$connect me2 me1 $by via1;

$device MOS (MN) gate_n od_n(D) gate_n(G) od_n(S);

$device MOS (MP) gate_p od_p(D) gate_p(G) od_p(S);

sample_cmap.lisa

!-------------------------------------------------------------------- !C map command file !DESIGN : design !TECHNO : techno !USER : !TIME : Thu Feb 23 04:05:50 2023 !-------------------------------------------------------------------- ! HIPEX to CUP map table cup layer "po1" /hipex_layer="po1"; cup layer "me1" /hipex_layer="me1"; ! MASKED DIELECTRIC LAYERS

r_tech.lisa

! ========================================================== !

! Hipex-R parasitic resistance extraction rules !

! ========================================================== !

hipex set_unit /resistance "Ohm" ;

hipex set_unit /length "um" ;

rpx define_parasitic Wire

/layer = me1

/max_length = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 1.0

;

rpx define_parasitic Wire

/layer = me2

/max_length = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 1.0

;

rpx define_parasitic Wire

/layer = po1

/max_length = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 1.0

;

rpx define_parasitic Contact

/layer = cont

/top = me1

/bottom = po1

/pres_area_resistivity_value = 100.0

;

rpx define_parasitic Contact

/layer = cont

/top = me1

/bottom = od_n

/pres_area_resistivity_value = 100.0

;

rpx define_parasitic Contact

/layer = cont

/top = me1

/bottom = od_p

/pres_area_resistivity_value = 100.0

;

c_tech.lisa

! ========================================================== !

! Hipex-C parasitic capacitance extraction rules !

! ========================================================== !

hipex set_unit /capacitance "pF" ;

hipex set_unit /length "um" ;

cpx order po1, me1;

cpx Lateral me1 po1

/factor = 1.0,1.0,1.0

/max_distance = 5

/max_width = 0

/l_threshold = 0

;

cpx Area me1 po1

1.0

;

sample_setup.lpe

[BackannotateAndLVS] Enable=0 LvsProject= RunLVS=0 SchematicFile= UseCellSettings=0 UseLvsProject=0 [BackannotateAndLVS/Cells] Count=0 [Capacitance] CouplingGroundThreshold=0 CouplingThreshold=0 ExtCurCupCoefs=c_tech.lisa GlobalVicinity=0 HierarchicalNetlist=sample_c_hier.spice NodeBasedExtraction=0 UseCurCupCoefs=0 UseIntPcapScript=0 [Cells] Count=4 [Cells/Cell_0] Bidirectional= Clock= Explosion=EXPLODE Input= Name=AND Output= Reduction=0 [Cells/Cell_1] Bidirectional= Clock= Explosion=EXPLODE Input= Name=INV Output= Reduction=0 [Cells/Cell_2] Bidirectional= Clock= Explosion=EXPLODE Input= Name=sample_2 Output= Reduction=0 [Cells/Cell_3] Bidirectional= Clock= Explosion=EXPLODE Input= Name=sample Output= Reduction=0 [Crc] CellCount=4 [Crc/Cell_0] Name=AND NetCount=0 [Crc/Cell_1] Name=INV NetCount=0 [Crc/Cell_2] Name=sample_2 NetCount=0 [Crc/Cell_3] Name=sample NetCount=0 [Crc/Cell_All] ThresholdCap=-1 ThresholdRes=-1 [Crc/Cell_Top] ThresholdCap=-1 ThresholdRes=-1 [Crc/Details] DetailedDisplay=0 DetailedSummary=0 DisplayPartitions=0 TitleLine=0 [Crc/Input] Directory=SPF File=sample.dspf Format=DSPF [Crc/Output] Directory=CRC_Files File=sample.dspf.crc Format=DSPF [Crc/Reduction] Authorize=0 CouplingMode=0 ParallelCheck=0 PortFile= SerieCheck=0 [Erc/DangleNodes] Netlist=0 Report=1 [Erc/Errors] SoftcheckWarnings=0 [Erc/OpenNodes] Rename=0 Short=0 [Erc/ShortedNodes] GenerateName=0 MultilabelName=MULTILABEL [Erc/Warnings] BJT=0 MOSFET=1 [Explosion] AutoExplode=0 CellArrayReduction=0 KeepFlattenCells=1 Wiring=0 [External] CapacitanceUnit=pF DeckBuildVersionForHipex= LengthUnit=um ResistanceUnit=Ohm TernaryConnectThroughTouch=0 UseCurLayoutText=1 UseCurProcess=1 UseCurProcessCommon=1 UseCurProcessVictoryRCx=1 UseCurTechConnect=1 UseCurTechDevice=1 UseDerLayersDRCFile=1 UseIntDrcScript=0 UseIntLayoutTextScript=0 UseIntProcessScript=0 UseIntProcessScriptCommon=0 UseIntProcessScriptVictoryRCx=0 VictoryMeshVersionForHipex= VictoryProcessVersionForHipex= [FsCExtraction] CapMinValue=1e-20 ConductorFilter=0 Decomposition=1 DecompStep=0 DecompStepValue=-1 DomainLimitations=0 DomainLimitXmax=0 DomainLimitXmin=0 DomainLimitYmax=0 DomainLimitYmin=0 GridStepX=0.5 GridStepY=0.5 GridStepZ=0.5 MaxIterations=100 Precision=0.01 Renew=0 RenewSavedFile=RenewSavedFile.sav Stellar3DStructFile=3DStructureFile.str Stellar3DStructGeneration=0 [FsExtr_GlobalSettings/CapacitanceOptions] Count=10 [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption0] Name=CAPsolver= Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption1] Name=Cjunc= Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption2] Name=Ground Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption3] Name=userCAPchoice= Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption4] Name=DomainBoundaryCondition= Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption5] Name=fast Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption6] Name=accurate Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption7] Name=fixDummyCharge Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption8] Name=biasConductors Use=0 Value= [FsExtr_GlobalSettings/CapacitanceOptions/CmdOption9] Name=M2Iverysmall Use=0 Value= [FsExtr_GlobalSettings/CDloss] Count=0 [FsExtr_GlobalSettings/ExtractionCapacitance] AdaptCValue=0.04 CapAccuracy=3 MinCalValue=1e-19 UseAdaptC=0 UseCapAccuracy=0 UseMinCap=0 [FsExtr_GlobalSettings/ExtractionGeneral] ExtractBoth=1 ExtractCap=1 ExtractRes=1 ExtractStructure= ExtractUseStructure=0 Model3D=1 RefineMax=0 RefineMaxValue=10 Tolerance=0 ToleranceValue=0 UseHEforCap=0 UseVEforRes=0 [FsExtr_GlobalSettings/ExtractionResistance] AdaptRValue=0.04 External=0 MinResValue=0.01 ResAccuracy=1 UseAdaptR=0 UseMinRes=0 UseResAccuracy=0 [FsExtr_GlobalSettings/General] CutlineArea_MaxX=0 CutlineArea_MaxY=0 CutlineArea_MinX=0 CutlineArea_MinY=0 SpecifyArea=0 TopCellName= WorkArea_MaxX=0 WorkArea_MaxY=0 WorkArea_MinX=0 WorkArea_MinY=0 [FsExtr_GlobalSettings/JColumns] Count=9 [FsExtr_GlobalSettings/JColumns/Column0] Width=50 [FsExtr_GlobalSettings/JColumns/Column1] Width=140 [FsExtr_GlobalSettings/JColumns/Column2] Width=220 [FsExtr_GlobalSettings/JColumns/Column3] Width=220 [FsExtr_GlobalSettings/JColumns/Column4] Width=120 [FsExtr_GlobalSettings/JColumns/Column5] Width=120 [FsExtr_GlobalSettings/JColumns/Column6] Width=120 [FsExtr_GlobalSettings/JColumns/Column7] Width=300 [FsExtr_GlobalSettings/JColumns/Column8] Width=140 [FsExtr_GlobalSettings/Other] DefaultCSV= numPrecision=1 SendMailWhenFinish=0 ShowSpecifiedJobs=0 ShowStructureImg=2 UseCDloss=0 UserDefinedDecimalNumber=0 UserEMail= WorkTemplate=%current_project%%current_cell%_#%order% [FsExtr_GlobalSettings/Parallel] AutoSelectParallelJobs=1 ParallelJobCount=1 ParallelMode=0 ReUseStructure=1 [FsExtr_GlobalSettings/ResColumns] Count=7 [FsExtr_GlobalSettings/ResColumns/Column0] Width=50 [FsExtr_GlobalSettings/ResColumns/Column1] Width=50 [FsExtr_GlobalSettings/ResColumns/Column2] Width=220 [FsExtr_GlobalSettings/ResColumns/Column3] Width=220 [FsExtr_GlobalSettings/ResColumns/Column4] Width=120 [FsExtr_GlobalSettings/ResColumns/Column5] Width=120 [FsExtr_GlobalSettings/ResColumns/Column6] Width=120 [FsExtr_GlobalSettings/SpecifyCleverVersion] CleverVersion=3.10.15.R SpecifyCleverVersion=0 [HdbGeneration] AnnotatedGdsFile=sample_layout_net_dump.gds SmartLvsRuleFile=sample_layout_net_dump_rule.pwr UpdateCurrentTechnology=0 UseSmartLvsFiles=1 [HierViolatChecks] Count=0 [Layout] DelWhite=1 ExportAnnotate=0 FixedSize=0 Flatten=0 GlobalDatatypes= Labels=0 NetFixedSize=0 NetLabels=0 Non45=0 Overlap=0 ParallelModeDeriv=1 Rebuild=0 SafeHierDerivation=0 SafeHierDerivType=1 ShortLabel=0 TopCell=sample TopLevel=0 TopTextDepth=1 [Layout/FixedSize] Height=0 Width=0 [Layout/NetFixedSize] NetHeight=0 NetWidth=0 [NodeName] CaseSensitiveNetNames=0 GlobalNode= GroundNode=0 HierarchySeparator=/ InstancePrefix=I NodeNameSeparator=_ NodePrefix=# PinDelimiter=: PowerNode= TopVirtualConnect=1 UseNdlInstNames=0 UseNdlNetNames=0 VirtualConnectNames= VirtualNetFlag=0 VirtualNetSymbols=: XY=0 [Output] CommentModel=0 ExcludeLibraryPrefix=0 FlatNetlist=sample_flat.spice FlatNetlisting=0 GlobalsInSubcktPins=1 HierarchicalNetlist=sample_hier.spice Messages=0 NetlistLineLength=80 NetlistTextedPins=0 PModelOutput=0 SbcktPininfo=0 [Output/Parameters] Capacitors=1 CapacitorsLw=0 LWOnly=0 Resistors=1 SdNoW=0 [Ports] Count=0 [Project] EditorVersion=0.7.2.A User=viktarm [Rc] CouplingMode=1 DeleteFloatingSubnets=0 DistributionMode=2 DspfOutput=1 DspfOutputDir=SPF IgnoreNets= Miller=1 ParallelMode=0 ProcessorNumber=16 RcGetCsv=0 RcGetDspf=0 RcGetSpef=0 RcGetSpice=1 RcIgnoredNets=1 RCReduction=0 SelectedNodesList= SmallResistance=0.0001 SpefOutputDir=SPF SpiceOutputDir=sample_rc_hier.spice SPM=1 SubCells=1 TauMin=0 TM=0 VictoryRCxParallelMode=0 VictoryRCxProcessorNumber=1 VictoryRCxVersion= [Rc/OutputParameters] DevicesAsInstances=0 ExtractDevices=0 Layer=0 SuppressSubcktEnds=0 XY=0 [Resistance] ExtCurPresCoefs=r_tech.lisa HierarchicalNetlist=sample_r_hier.spice IgnoreDangles=0 IgnoreHierGlbNodes= IgnoreNodes= IgnorePower=1 OutputRDB=0 SelectedNodesList= SerialMergeThreshold=0 SubNodeSep=~ Threshold=0 UseCurPresCoefs=0 UseFieldSolver=0 UseIntPresScrip=0 UseTextsAsSubnodes=0 [Resistance/Output] LayerNames=1 LW=1 XY=1 [Resistance/OutputRDB] Pins=0 TopOnly=0 [Stripes] ActiveCollection=default BoxSizeX=400 BoxSizeY=400 BoxVicinityX=50 BoxVicinityY=50 CapMappingFile=sample_cmap.lisa CollectionsCount=1 DecompositionType=0 FsCExtract=0 FsCExtractMode=1 IncludeDangles=0 IncludeDummies=0 IncrementalCdbRdb=1 MnmBlockCount=0 MnmCExtract=0 StripeWidth=200 UseExternCapMapping=1 VicinityWidth=10 [Stripes/Collection_0] BA_Names=0 IgnoredNets=0 Name=default NetsCount=0 NetsList= SelectedNets=0 SkipCells=0 SkipCellsFile= TopOnly=0 TopOnlyNocells=0 [SubstrateExtraction] BacksideConductivity=3.3e-10 BacksidePermittivity=6.2 BacksideThickness=10 IncludeBacksideModel=0 RunSipex=0 SiliconBackside=0 SiliconBacksideNode=cwsBackside SiliconThickness=300 SipexManufacturingDatabase= SipexVersion= SpxTemperature=27 SubstrateExtractionMode=0