006 : Initial Correspondence File

Minimum Required Version: Guardian LVS 4.8.36.R

The initial correspondence file can be used in Guardian LVS to set equivalence between various netlist elements such as nodes, instances, and device models.

The syntax of the initial correspondence file is described below for several netlist elements that a user may want to establish equivalence between the schematic netlist and a layout extracted netlist.

Net Equivalence

Setting net equivalence in a circuit that has symmetric elements can make the LVS matching process more efficient. The syntax for this statement is as follows:

.NET [subckt]:[name] = [subckt]:[name]

[subckt] is the top level subcircuit name.

The example file init_crspnd.in contains the following two lines in order to match the power and ground nets of the circuit.

.NET DFF:VDD = logic_dff:PWR

.NET DFF:VSS = logic_dff:GND

Note that Guardian LVS will generate an LVS clean report without using the net equivalence in the initial correspondence file if the LVS option Detect label mismatch is not selected. However, the net equivalence statement is very useful for the case where label matching is needed yet there may be a different node naming convention.

Subcircuit Equivalence

In order to run hierarchical LVS, the subcircuit names must match between the schematic netlist and layout netlist. In the case of one of the netlists employing a different naming convention for subcircuits , the subcircuit equivalence statement shown below can be used:

.HCELL [subckt1] = [subckt2]

The example file init_crspnd.in contains the following two lines in order to match the schematic subcircuit names to the ones used in the layout:

.HCELL NAND2 = logic_nand_2

.HCELL NAND3 = logic_nand_3

Running Guardian LVS

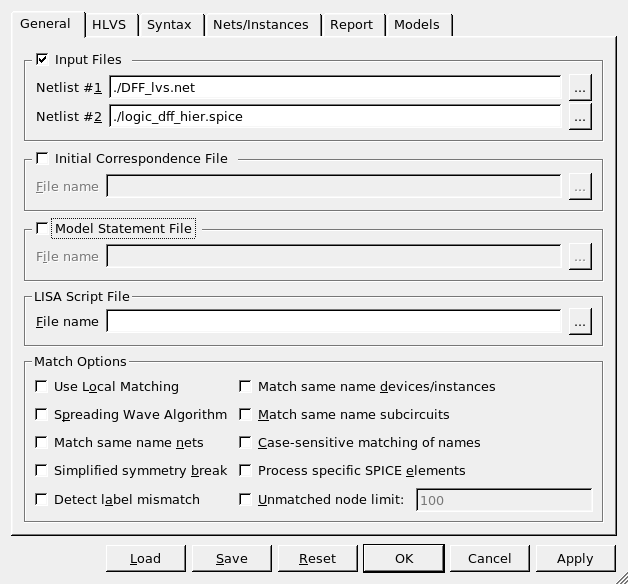

Launch Guardian LVS and then select Setup->Project Settings from the menu to open the settings GUI. Browse to the schematic netlist DFF_lvs.net in the Netlist #1 field, and browse to the layout netlist logic_dff_hier.spice in the Netlist #2 field.

If the two netlists are compared without any of the matching options selected as seen in Figure 1 , Guardian LVS will run in flat mode and produce an LVS match since the two netlists are functionally equivalent despite having different subcircuit and net naming conventions.

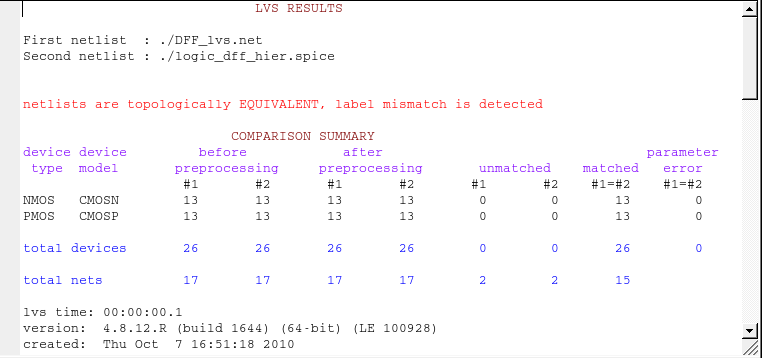

If the project settings option Detect label mismatch is selected and LVS run again, the log file will display the message: "netlists are topologically EQUIVALENT, label mismatch is detected" as seen in Figure 2 .

This is due to the schematic netlist using VDD and VSS , and the layout netlist using PWR and GND . By selecting the project settings option for using the initial correspondence file and browsing to init_crspnd.in and running LVS again, the label mismatch warning will be eliminated due to the net equivalence statements in the initial correspondence file.

If the option Match same name subcircuits is selected, and the hierarchical mode is enabled from the HVLS tab of the project settings GUI, then Guardian LVS can perform hierarchical LVS on the two netlists since the initial correspondence file maps the subcircuit names from the schematic and layout netlist. After the settings are changed and LVS is run again, the log file will display a match for the two subcircuits used in this example as seen in Figure 3 .

init_crspnd.in

.HCELL NAND2 = logic_nand_2 .HCELL NAND3 = logic_nand_3 .NET DFF:VDD= logic_dff:PWR .NET DFF:VSS= logic_dff:GND