001 : Running Guardian LVS

Minimum Required Versions: Expert 4.10.37.R, Guardian LVS 4.8.36.R

Guardian LVS (Layout Versus Schematic) netlist comparison tool compares two SPICE netlists. One of the compared netlists usually corresponds to the schematic of a circuit produced by a schematic editor (e.g. Gateway ), which represents the circuit. The other netlist is extracted from the circuit layout by Guardian NET . It represents the actual physical layout of the circuit as produced by a layout editor (e.g. Expert ).

1. Execution of Guardian LVS

1) Launch Guardian LVS from Expert by selecting Verification->LVS->Launch LVS .

2) It is necessary to se the project settings in the Project Settings dialog. To open it, select Setup->Project Settings or click the Project Settings button in the Action Toolbar .

3) Add two SPICE netlists to Input Files in the General tab. The netlist has to be set as follows:

Netlist #1 ----- Netlist of the schematic

Netlist #2 ----- Netlist of the layout

If the order of the two netlists is reversed, cross probing will not be executed.

4) To adjust the settings of a model, select the Models tab. You can either adjust the settings for a group of models (e.g., all MOS devices) or for a particular model of a specified device.

5) Then run LVS by selecting Run LVS from the Action menu or by clicking the Run LVS button in the Action Toolbar .

6) The LVS result is displayed in the LVS Log file.

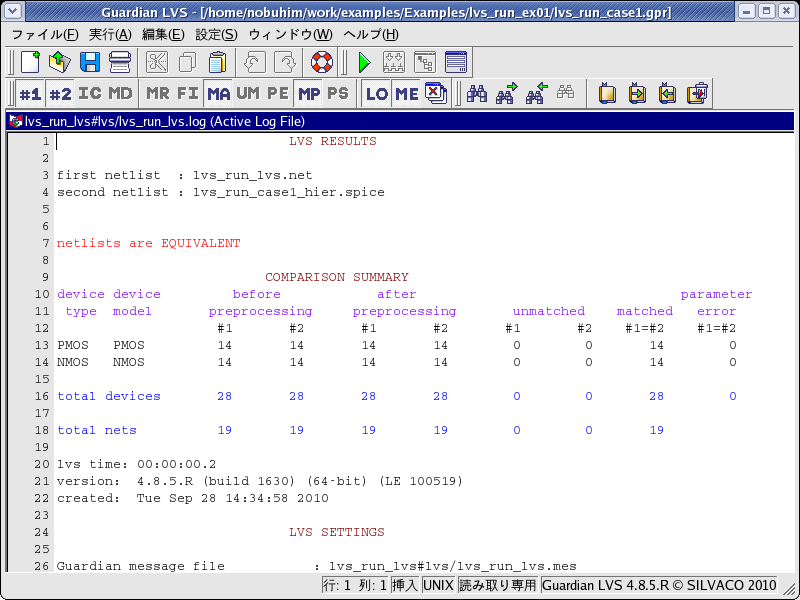

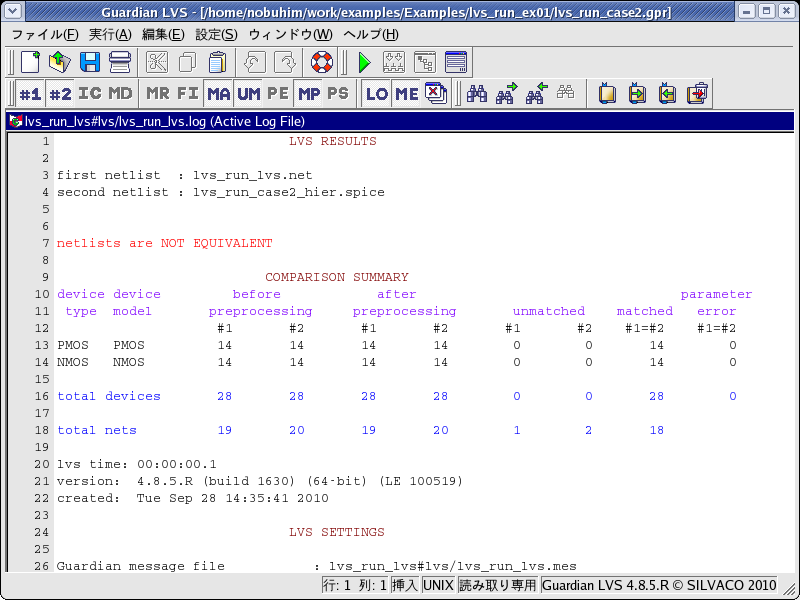

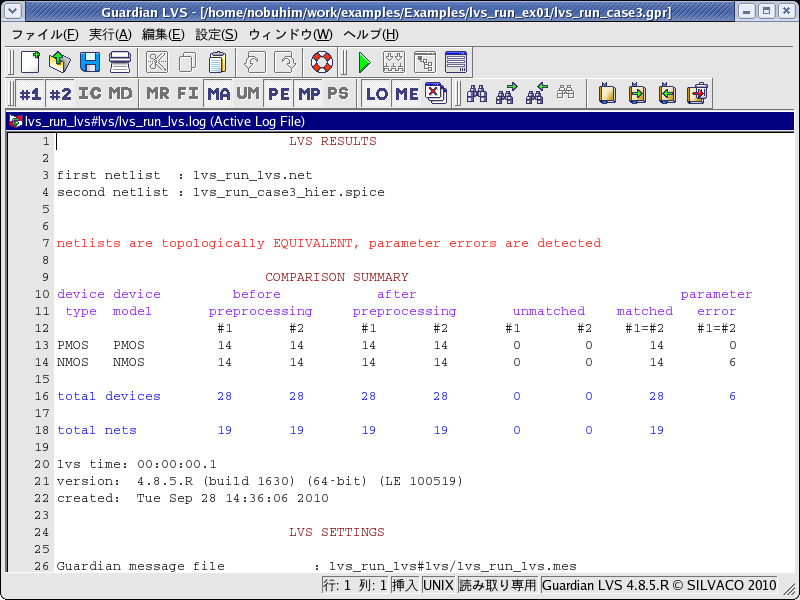

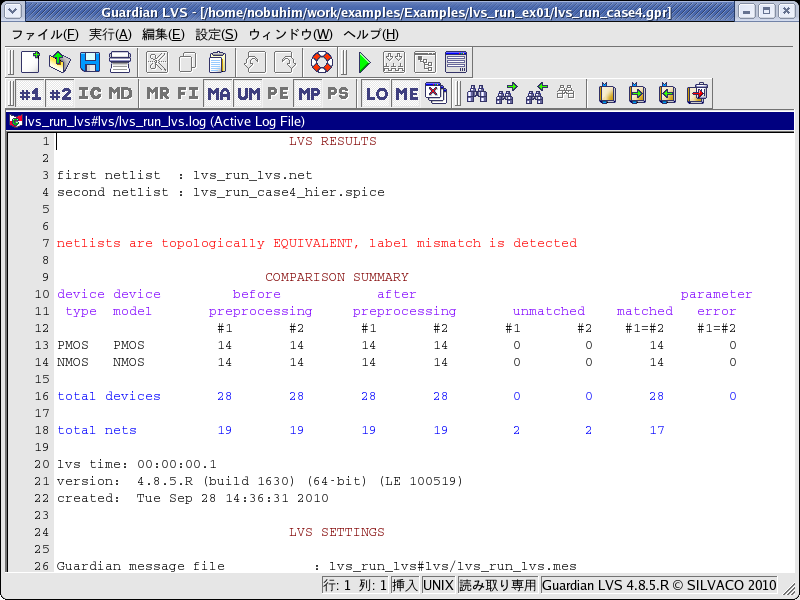

Here is the example of the LVS result:

netlists are EQUIVALENT : two netlists are logically equivalent.

netlists are NOT EQUIVALENT : two netlists are not logically equivalent.

netlists are topologically EQUIVALENT, parameter errors are detected : two netlists are logically equivalent, but it has parameter errors.

netlists are topologically EQUIVALENT, label mismatch is detected : two netlists are logically equivalent, but it has a label mismatch error.

7) Details of the error are in the Unmatched file ( UM ) and Parameter Error file ( PE ) when there is an LVS error. When a node name (device name) in the UM ( PE ) file is double-clicked, cross probing between the UM ( PE ) and the layout is executed. The LVS error part is highlighted in the layout, so it is easy to find the LVS error.

2. Execution of Guardian LVS with the LVS project file (*.gpr)

1) Load the Guardian LVS project file *.gpr by clicking the Load button at the bottom of the Project Settings dialog.

2) If you would like to compare another netlist, change the setting.

3) Run LVS.

4) The LVS result is displayed in the LVS Log file.

3. Execution of Guardian LVS with examples

Case1: netlists are EQUIVALENT (see lvs_run_case1.png

)

1) Load lvs_run_case1.gpr .

2) Run LVS.

Case2: netlists are NOT EQUIVALENT (see lvs_run_case2.png

)

1) Load lvs_run_case2.gpr .

2) Run LVS.

Case3: netlists are topologically EQUIVALENT, parameter errors are detected (see lvs_run_case3.png

)

1) Load lvs_run_case3.gpr .

2) Run LVS.

Case4: netlists are topologically EQUIVALENT, label mismatch is detected (see lvs_run_case4.png

)

1) Load lvs_run_case4.gpr .

2) Run LVS.

lvs_run_lvs.net

* Gateway 2.12.11.R Guardian Netlist Generator * Workspace name: lvs_run.workspace * Simulation name: lvs_run.schlr * Simulation timestamp: 28-Sep-2010 10:34:29 * Schematic name: lvs_run .SUBCKT lvs_run A B Cn Cn+1 Sn M1 NET1 A VDD PMOS L=0.4U W=2.4U M=1 M2 NET1 B VDD PMOS L=0.4U W=2.4U M=1 M3 NET1 Cn VDD PMOS L=0.4U W=2.4U M=1 M4 NET4 NCn+1 NET1 PMOS L=0.4U W=2.4U M=1 M5 NET2 Cn NET1 PMOS L=0.4U W=2.4U M=1 M6 NET3 B NET2 PMOS L=0.4U W=2.4U M=1 M7 NET4 A NET3 PMOS L=0.4U W=2.4U M=1 M8 NET4 A NET5 NMOS L=0.4U W=1.6U M=1 M9 NET4 NCn+1 NET8 NMOS L=0.4U W=1.6U M=1 M10 NET5 B NET6 NMOS L=0.4U W=1.6U M=1 M11 NET6 Cn GND NMOS L=0.4U W=1.6U M=1 M12 NET8 A GND NMOS L=0.4U W=1.6U M=1 M13 NET8 B GND NMOS L=0.4U W=1.6U M=1 M14 NET8 Cn GND NMOS L=0.4U W=1.6U M=1 M15 Sn NET4 GND NMOS L=0.4U W=1.6U M=1 M16 Sn NET4 VDD PMOS L=0.4U W=2.4U M=1 M17 NET12 A VDD PMOS L=0.4U W=2.4U M=1 M18 NET12 B VDD PMOS L=0.4U W=2.4U M=1 M19 NET13 B NET12 PMOS L=0.4U W=2.4U M=1 M20 NCn+1 A NET13 PMOS L=0.4U W=2.4U M=1 M21 NCn+1 Cn NET12 PMOS L=0.4U W=2.4U M=1 M22 NCn+1 A NET16 NMOS L=0.4U W=1.6U M=1 M23 NET16 B GND NMOS L=0.4U W=1.6U M=1 M24 NCn+1 Cn NET18 NMOS L=0.4U W=1.6U M=1 M25 NET18 A GND NMOS L=0.4U W=1.6U M=1 M26 NET18 B GND NMOS L=0.4U W=1.6U M=1 M27 Cn+1 NCn+1 GND NMOS L=0.4U W=1.6U M=1 M28 Cn+1 NCn+1 VDD PMOS L=0.4U W=2.4U M=1 .ENDS lvs_run * Global Nodes Declarations .GLOBAL GND VDD * End of the netlist

lvs_run_case1_hier.spice

******************************************************************************* * * Extracted SPICE netlist for top cell lvs_run_case1 * Created Tue Sep 28 14:30:01 2010 by hipex 3.4.7.R 64-bit (Tue May 25 12:44:06 PDT 2010) version * ******************************************************************************* .MODEL pmos PMOS .MODEL nmos NMOS ******************************************************************************* * * Sub-Circuit Netlist of : lvs_run_case1 * ******************************************************************************* .subckt lvs_run_case1 A B Cn Cn+1 GND Sn VDD MI3 GND A #11 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI1 GND Cn #11 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI0 Sn #2 GND GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI2 #11 B GND GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI19 #2 A #6 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI11 #1 A #5 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.64P PS=2U PD=2.4U MI7 #4 Cn GND GND nmos L=0.4U W=1.6U AS=1.28P AD=0.32P PS=4.8U PD=2U MI5 #2 A #3 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.64P PS=2U PD=2.4U MI4 #11 #1 #2 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI6 #3 B #4 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.32P PS=2U PD=2U MI9 GND B #12 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI8 Cn+1 #1 GND GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI10 #12 Cn #1 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI15 VDD Cn #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI13 GND A #12 GND nmos L=0.4U W=1.6U AS=1.28P AD=0.64P PS=4.8U PD=2.4U MI12 #5 B GND GND nmos L=0.4U W=1.6U AS=0.64P AD=0.32P PS=2.4U PD=2U MI14 Sn #2 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI17 VDD A #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI16 #10 B VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI18 #10 #1 #2 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI23 VDD B #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI21 #7 Cn #10 VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.48P PS=6.4U PD=2.8U MI20 #6 B #7 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.48P PS=2.8U PD=2.8U MI22 Cn+1 #1 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI25 #1 A #8 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI24 #9 Cn #1 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI26 #8 B #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.48P PS=3.2U PD=2.8U MI27 #9 A VDD VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.96P PS=6.4U PD=3.2U .ends lvs_run_case1 .end

lvs_run_case2_hier.spice

******************************************************************************* * * Extracted SPICE netlist for top cell lvs_run_case2 * Created Tue Sep 28 14:31:28 2010 by hipex 3.4.7.R 64-bit (Tue May 25 12:44:06 PDT 2010) version * ******************************************************************************* .MODEL pmos PMOS .MODEL nmos NMOS ******************************************************************************* * * Sub-Circuit Netlist of : lvs_run_case2 * ******************************************************************************* .subckt lvs_run_case2 A B Cn Cn+1 GND Sn VDD MI3 GND A #11 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI1 GND Cn #12 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI0 Sn #2 GND GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI2 #12 B GND GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI19 #2 A #6 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI11 #1 A #5 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.64P PS=2U PD=2.4U MI7 #4 Cn GND GND nmos L=0.4U W=1.6U AS=1.28P AD=0.32P PS=4.8U PD=2U MI5 #2 A #3 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.64P PS=2U PD=2.4U MI4 #11 #1 #2 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI6 #3 B #4 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.32P PS=2U PD=2U MI9 GND B #13 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI8 Cn+1 #1 GND GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI10 #13 Cn #1 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI15 VDD Cn #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI13 GND A #13 GND nmos L=0.4U W=1.6U AS=1.28P AD=0.64P PS=4.8U PD=2.4U MI12 #5 B GND GND nmos L=0.4U W=1.6U AS=0.64P AD=0.32P PS=2.4U PD=2U MI14 Sn #2 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI17 VDD A #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI16 #10 B VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI18 #10 #1 #2 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI23 VDD B #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI21 #7 Cn #10 VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.48P PS=6.4U PD=2.8U MI20 #6 B #7 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.48P PS=2.8U PD=2.8U MI22 Cn+1 #1 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI25 #1 A #8 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI24 #9 Cn #1 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI26 #8 B #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.48P PS=3.2U PD=2.8U MI27 #9 A VDD VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.96P PS=6.4U PD=3.2U .ends lvs_run_case2 .end

lvs_run_case3_hier.spice

******************************************************************************* * * Extracted SPICE netlist for top cell lvs_run_case3 * Created Tue Sep 28 14:31:37 2010 by hipex 3.4.7.R 64-bit (Tue May 25 12:44:06 PDT 2010) version * ******************************************************************************* .MODEL pmos PMOS .MODEL nmos NMOS ******************************************************************************* * * Sub-Circuit Netlist of : lvs_run_case3 * ******************************************************************************* .subckt lvs_run_case3 A B Cn Cn+1 GND Sn VDD MI3 GND A #11 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI1 GND Cn #11 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI0 Sn #2 GND GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI2 #11 B GND GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI19 #2 A #6 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI11 #1 A #5 GND nmos L=0.4U W=1.7U AS=0.34P AD=0.68P PS=2.1U PD=2.5U MI7 #4 Cn GND GND nmos L=0.4U W=1.6U AS=1.28P AD=0.32P PS=4.8U PD=2U MI5 #2 A #3 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.64P PS=2U PD=2.4U MI4 #11 #1 #2 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI6 #3 B #4 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.32P PS=2U PD=2U MI9 GND B #12 GND nmos L=0.4U W=1.7U AS=0.68P AD=0.68P PS=2.5U PD=2.5U MI8 Cn+1 #1 GND GND nmos L=0.4U W=1.7U AS=0.68P AD=1.36P PS=2.5U PD=5U MI10 #12 Cn #1 GND nmos L=0.4U W=1.7U AS=0.68P AD=0.68P PS=2.5U PD=2.5U MI15 VDD Cn #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI13 GND A #12 GND nmos L=0.4U W=1.7U AS=1.36P AD=0.68P PS=5U PD=2.5U MI12 #5 B GND GND nmos L=0.4U W=1.7U AS=0.68P AD=0.34P PS=2.5U PD=2.1U MI14 Sn #2 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI17 VDD A #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI16 #10 B VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI18 #10 #1 #2 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI23 VDD B #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI21 #7 Cn #10 VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.48P PS=6.4U PD=2.8U MI20 #6 B #7 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.48P PS=2.8U PD=2.8U MI22 Cn+1 #1 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI25 #1 A #8 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI24 #9 Cn #1 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI26 #8 B #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.48P PS=3.2U PD=2.8U MI27 #9 A VDD VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.96P PS=6.4U PD=3.2U .ends lvs_run_case3 .end

lvs_run_case4_hier.spice

******************************************************************************* * * Extracted SPICE netlist for top cell lvs_run_case4 * Created Tue Sep 28 14:31:46 2010 by hipex 3.4.7.R 64-bit (Tue May 25 12:44:06 PDT 2010) version * ******************************************************************************* .MODEL pmos PMOS .MODEL nmos NMOS ******************************************************************************* * * Sub-Circuit Netlist of : lvs_run_case4 * ******************************************************************************* .subckt lvs_run_case4 A B Cn Cn+1 GND Sn VDD MI3 GND B #11 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI1 GND Cn #11 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI0 Sn #2 GND GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI2 #11 A GND GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI19 #2 B #6 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI11 #1 B #5 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.64P PS=2U PD=2.4U MI7 #4 Cn GND GND nmos L=0.4U W=1.6U AS=1.28P AD=0.32P PS=4.8U PD=2U MI5 #2 B #3 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.64P PS=2U PD=2.4U MI4 #11 #1 #2 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI6 #3 A #4 GND nmos L=0.4U W=1.6U AS=0.32P AD=0.32P PS=2U PD=2U MI9 GND A #12 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI8 Cn+1 #1 GND GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI10 #12 Cn #1 GND nmos L=0.4U W=1.6U AS=0.64P AD=0.64P PS=2.4U PD=2.4U MI15 VDD Cn #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI13 GND B #12 GND nmos L=0.4U W=1.6U AS=1.28P AD=0.64P PS=4.8U PD=2.4U MI12 #5 A GND GND nmos L=0.4U W=1.6U AS=0.64P AD=0.32P PS=2.4U PD=2U MI14 Sn #2 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI17 VDD B #10 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI16 #10 A VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI18 #10 #1 #2 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI23 VDD A #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI21 #7 Cn #10 VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.48P PS=6.4U PD=2.8U MI20 #6 A #7 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.48P PS=2.8U PD=2.8U MI22 Cn+1 #1 VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI25 #1 B #8 VDD pmos L=0.4U W=2.4U AS=0.48P AD=0.96P PS=2.8U PD=3.2U MI24 #9 Cn #1 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.96P PS=3.2U PD=3.2U MI26 #8 A #9 VDD pmos L=0.4U W=2.4U AS=0.96P AD=0.48P PS=3.2U PD=2.8U MI27 #9 B VDD VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.96P PS=6.4U PD=3.2U .ends lvs_run_case4 .end