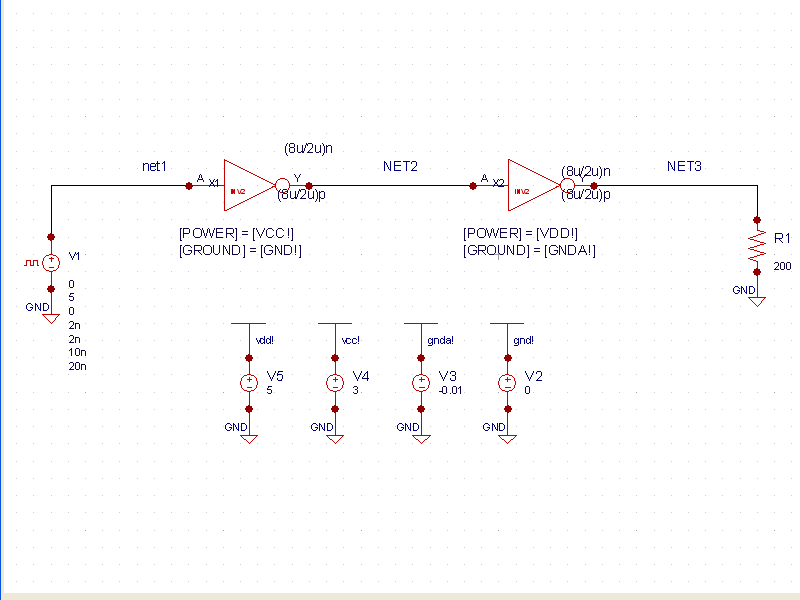

012_inherited_nets_implicit : Inherited Nets with Implicit Pins schematic

Minimum Required Versions: Gateway 2.12.8.R, SmartSpice 3.16.11.R

The illustrates using net property definitions on the symbol instances (see Example12.png ). For X1, VCC! is passed in for POWER and GND! is passed in for GROUND. For X2, VDD! and GNDA! are passed in, respectively.

On the subcircuit levels below, netexpressions are used on wires that can be overridden from a higher level. The [POWER]:[VDD] netexpression means that VDD is the name of the wire unless a value for [POWER] has been assigned on the level above. In this case, [POWER] has been defined for both X1 and X2.

In summary: The netexpression [POWER:[VDD] means: Use VDD for the net if the POWER property is not defined above. Otherwise, use what is defined for POWER

For the netexpression [GND]:[VSS], Use VSS for the net of the GND property is not defined above. Otherwise, use what is defined for GND

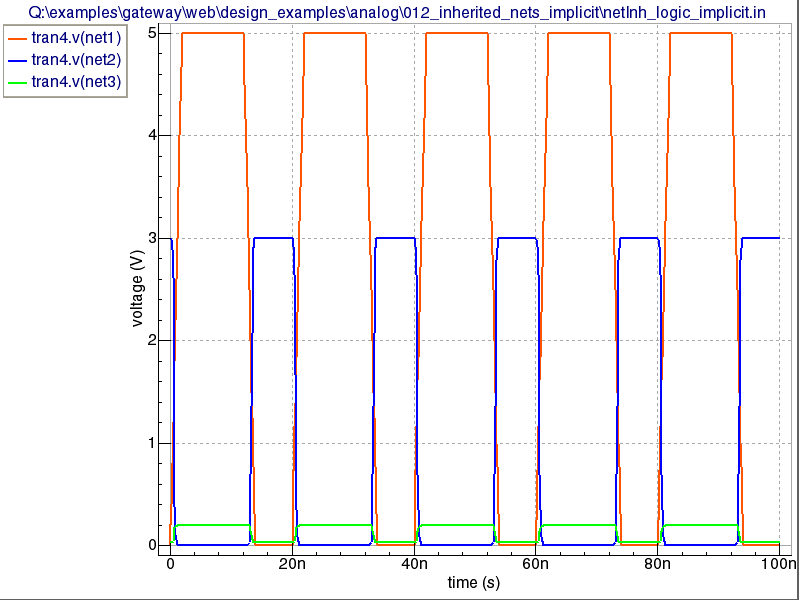

The wave forms (see waveforms.png ) show the input signal at 5 volts, then inverted at a 3 volt rail, and inverted back again across the load resistor.