011_inherited_nets_explicit : Inherited Nets with Explicit Pins Schematic

Minimum Required Versions: Gateway 2.12.8.R, SmartSpice 3.16.11.R

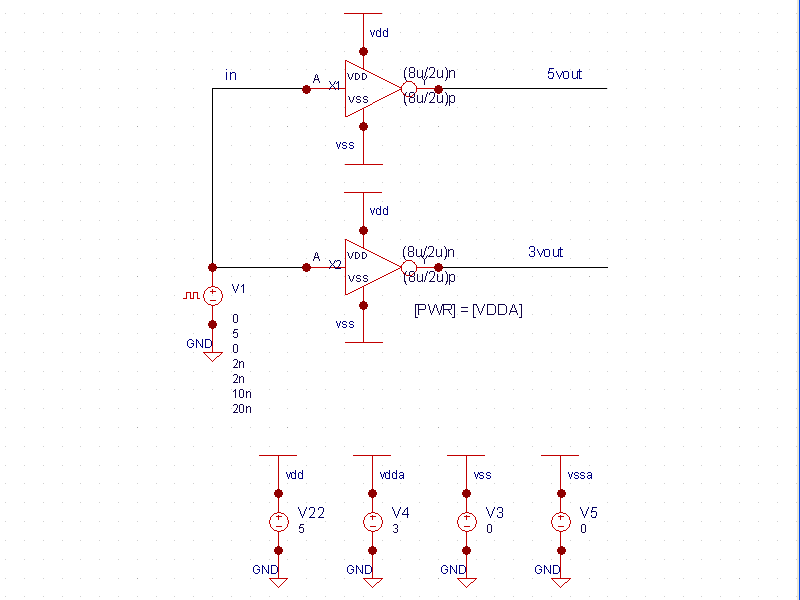

This example illustrates use of inherited nets on logic symbols that have explicit pins for power, substrate, and ground (see schematic.png ). In this example, we define vdd as 5v and vdda as 3v. Using the net property: [PWR]=[vdda] on X2, we override the connected signal (VDD) with VDDA and pass in 3v instead of the 5v that supplies VDD.

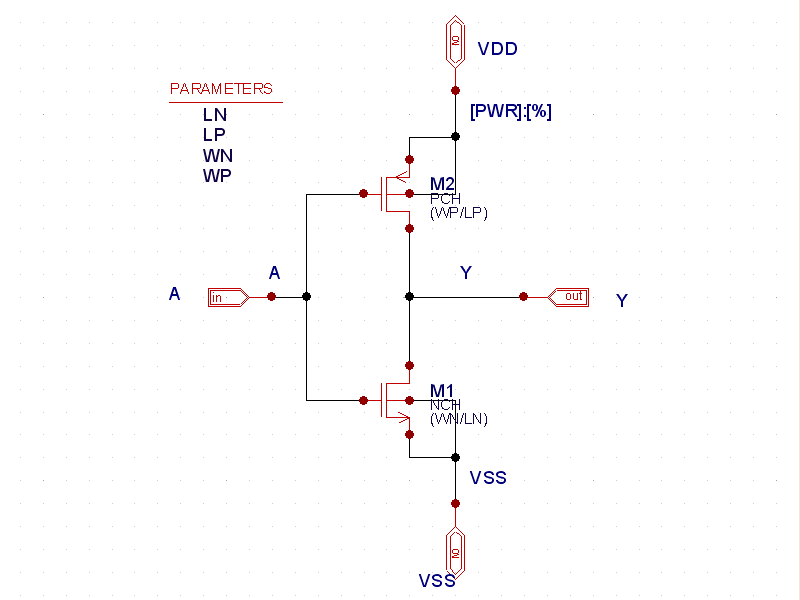

Clicking on the lower_level_X2.png X2 inverter and pressing the D key descends to the lower level. The percent sign [%] in the netexpressions denotes that unless the net property has been defined at a higher level, use the normal name for the net.

In this example, the netexpression [PWR]:[%] means this: For X1, no net property for PWR exists, so X1 uses the normal connection for the net which is VDD. For X2, however, a net property exists defined as [PWR]=[VDDA], so VDDA is used and overrides the VDD connection on this subcircuit.

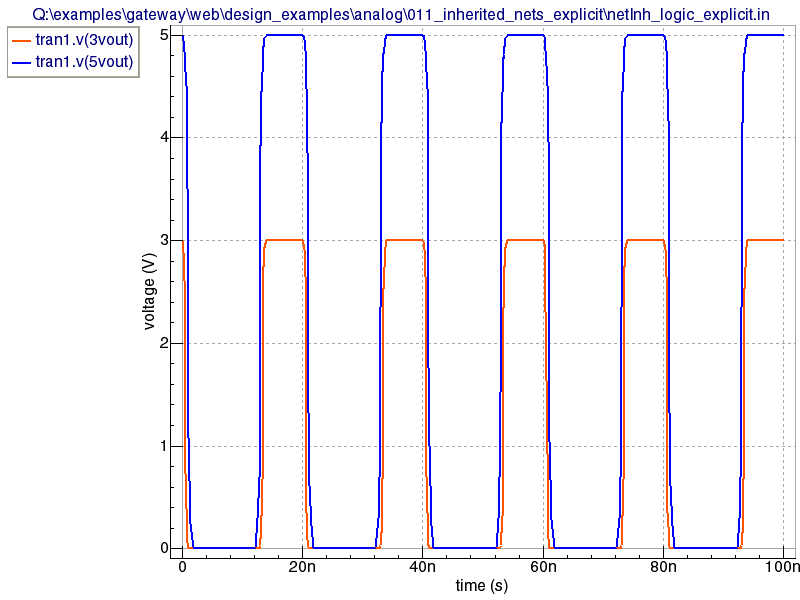

The netlist ( netInh_logic_explicit.net)shows how VDDA is used for X2. The wave forms (see waveforms.png ) display the inverter output at VDD (5V) and X2 override at 3V.

netInh_logic_explicit.net

* Gateway 2.12.6.R Spice Netlist Generator * Workspace name: Q:\examples\gateway\web\design_examples\analog\011_inherited_nets_explicit\inheritednets_explicit.workspace * Simulation name: Q:\examples\gateway\web\design_examples\analog\011_inherited_nets_explicit\netInh_logic_explicit.schlr * Simulation timestamp: 23-Apr-2010 15:18:10 * Schematic name: netInh_logic_explicit V1 in GND PULSE(0 5 0 2n 2n 10n 20n) V3 vss GND DC 0 V4 vdda GND DC 3 V5 vssa GND DC 0 V22 vdd GND DC 5 X1 in 5vout vdd vss inv PARAMS: LN=2u LP=2u WN=8u WP=8u X2 in 3vout VDDA vss inv PARAMS: LN=2u LP=2u WN=8u WP=8u * Schematic name: inv * Synonym List: inh__pwr = VDD * Inherited nets: [pwr]:[%] = inh__pwr .SUBCKT inv A Y inh__pwr VSS M1 Y A VSS VSS NCH L=LN W=WN M2 Y A inh__pwr inh__pwr PCH L=LP W=WP .ENDS inv * Global Nodes Declarations .GLOBAL GND VDD vdd vdda vss vssa * End of the netlist