004_hipex : HIPEX tool for parasitic RC extraction

Minimum Required Versions: Expert 4.10.39.R & HIPEX 3.4.38.R

HIPEX-C is a full-chip parasitic capacitance extractor used to extract coupling and ground capacitors from an Integrated Circuit (IC) layout.

HIPEX-R is a hierarchical full-chip parasitic resistance extractor used to extract resistances from an IC layout.

HIPEX-RC is a full-chip parasitic capacitance and resistance extractor.

1.1. Layout Parameter Extraction Setup

- Node Names

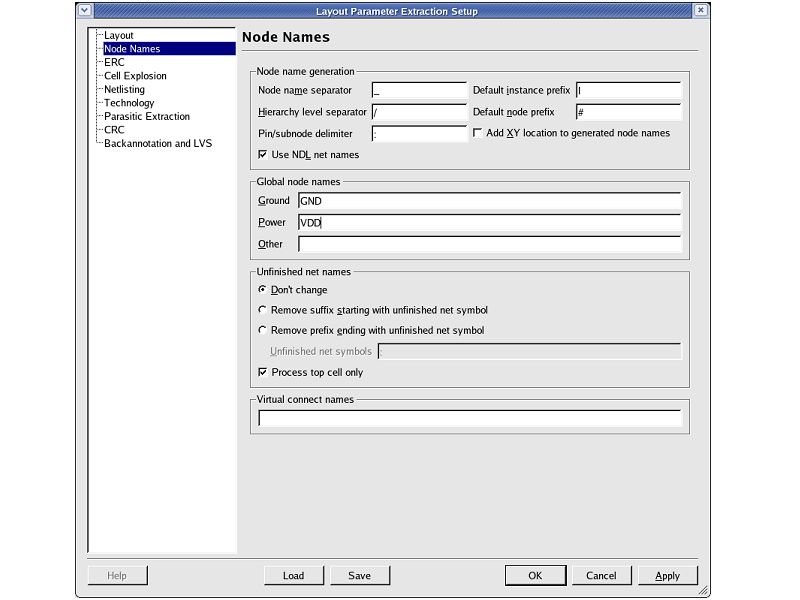

The global node names are set in the Layout Parameter Extraction Setup dialog. To open the Layout Parameter Extraction Setup, select Verification->Extraction->Setup . Then select the Node Names tab page. The global node names of the power, ground and other nodes are set (see node_names.png ). - Netlisting

When using HIPEX-C, the coupling threshold between two nets can be set under this tab. If the threshold is set to "0" all nets can coupled to every other nets for parasitic capacitances. If a threshold is set, only coupling capacitances between two nets with value greather than the threshold will be listed in the netlist. All other nets will have their parasitic value reference to ground. If the Coupling mode switch is enabled, a user can specify the nets for which coupling capacitance is allowed (Selected nets) or the nets for which the coupling capacitance will be ignored (ignored nets). The SPICE, DSPF and SPEF are generated when their options are turned on. - Technology

Technology of the parasitic capacitance and resistance is set. - Parasitic Extraction

Capacitance is extracted for all nodes or for a selected list of nodes in the layout.

1.2. Execution of HIPEX

HIPEX Database (HDB) generation is the first stage of Parasitic Extraction because it contains the information necessary for the Parasitic Databases (Resistance Database:RDB, Capacitance Database:CDB) generation. HDB database contains geometric and electric information on nodes and extracted design devices. Once you generate HIPEX Database (HDB), you don't need to run HIPEX-Net again unless you change the layout or rule file. HDB must be regenerated if an option or rule file was changed since the last run of HIPEX-Net layout.

- Load the file integration_ex04.eld, then open ex04 cell.

- Open the Node Names tab page, then add VDD for Power, GND for Ground.

- Click the Technology tab, then select parasitic_c.lisa for the parasitic capacitance technology and select parasitic_r.lisa for the parasitic resistance technology.

- Select Verification->Extraction->HIPEX-Net->Run which generates the HIPEX database.

To generate parasitic capacitance only, select: Verification->Extraction->HIPEX-C->Run.

To generate the parasitic resistance only, select: Verification->Extraction->HIPEX-R->Run.

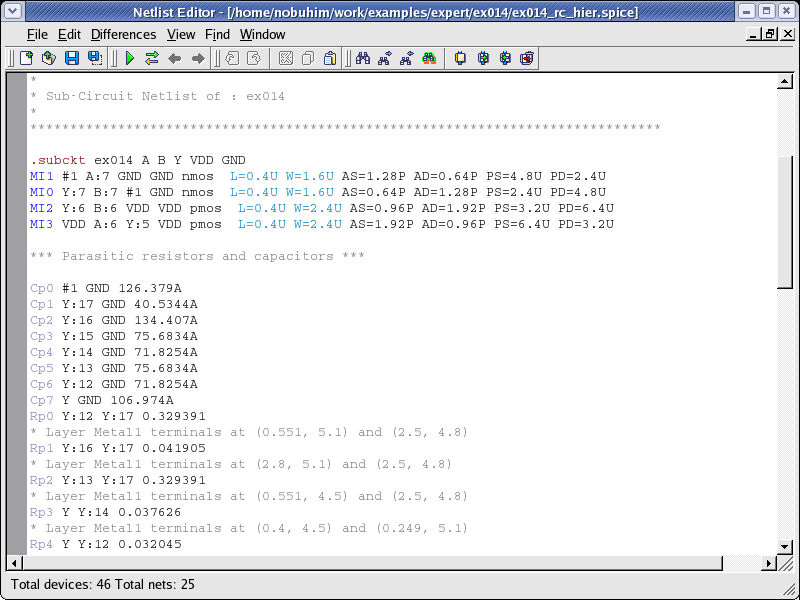

If you would like to get a netlist containing both R and C parasitics, select: Verification->Extraction->HIPEX-RC->Run. - The parasitic netlist is generated (see parasitic_netlist.png ).

- When the node is highlighted by the node probing, parasitic capacitance is displayed in the balloon if the DSPF file was generated. Display of parasitic resistance in two points is also available. To display parasitic resistance, hold down the Ctrl key while clicking two points of the node highlighted (see rc_value.png ).

parasitic_c.lisa

! ========================================================== !

! Hipex-C parasitic capacitance extraction rules !

! ========================================================== !

hipex set_unit /capacitance "pF" ;

hipex set_unit /length "um" ;

cpx order Poly, Metal1, Metal2;

cpx Lateral Metal2

/factor = 2.89,14.2,4.08

/max_distance = 5

/max_width = 0

/l_threshold = 0

;

cpx Area Metal2 Metal1

2.656e-05

;

cpx Fringe Metal2 Metal1

4.156e-05,0.3,0.668

/max_distance = 5

/max_width = 0

;

cpx Fringe Metal1 Metal2

2.34e-05,0.67,0.0001

/max_distance = 5

/max_width = 0

;

cpx Area Metal2 Poly

1.135e-05

;

cpx Fringe Metal2 Poly

3.35e-05,0.193,1.043

/max_distance = 5

/max_width = 0

;

cpx Lateral Metal1

/factor = 0.03,7.02,3.33

/max_distance = 5

/max_width = 0

/l_threshold = 0

;

cpx Area Metal1 Poly

2.6e-05

;

cpx Fringe Metal1 Poly

4.15e-05,0.33,0.65

/max_distance = 5

/max_width = 0

;

cpx Fringe Poly Metal1

6.2e-05,1.15,1.063

/max_distance = 5

/max_width = 0

;

cpx Lateral Poly

/factor = 1e-06,12.0,4.2

/max_distance = 5

/max_width = 0

/l_threshold = 0

;

parasitic_r.lisa

! ========================================================== !

! Hipex-R parasitic resistance extraction rules !

! ========================================================== !

hipex set_unit /resistance "Ohm" ;

hipex set_unit /length "um" ;

rpx define_parasitic Wire

/layer = Metal1

/max_length = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.075

;

rpx define_parasitic Wire

/layer = Metal2

/max_length = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 0.07

;

rpx define_parasitic Wire

/layer = Poly

/max_length = 0.0

/contact_cluster = 0.0

/pres_sheet_resistivity_value = 7.0

;

rpx define_parasitic Contact

/layer = Via

/top = Metal2

/bottom = Metal1

/pres_area_resistivity_value = 0.3

;