/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Gigi Boss

/wp-content/uploads/2019/11/silvaco-logo.png

Gigi Boss2024-04-16 15:54:192024-04-16 15:58:59Silvaco Announces Expanded Partnership with Micron Technology

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Gigi Boss

/wp-content/uploads/2019/11/silvaco-logo.png

Gigi Boss2024-04-16 15:54:192024-04-16 15:58:59Silvaco Announces Expanded Partnership with Micron Technology

Silvaco Successfully Concludes Its Global Users Event (SURGE) With Over 1000 End-Users and Prospects in Attendance

December 21, 2023

Colin Shaw of Silvaco Named Si2 Pinnacle Award Winner

December 12, 2021

Improvement of Parasitic Capacitance Extraction Rules for Large-Scale Layout and Its Accuracy Verification Method

September 17, 2020 | 13:00 – 13:30 (JST)

The accuracy of rule-based full-chip parasitic capacitance extraction tools including Silvaco's Hipex is highly dependent on the description of the rule files.

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2020-01-16 19:31:102021-04-23 13:16:08Accelerate the Circuit Simulation Flow with Jivaro Parasitic Reduction

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2020-01-16 19:31:102021-04-23 13:16:08Accelerate the Circuit Simulation Flow with Jivaro Parasitic Reduction

Parasitic Reduction

Jivaro Parasitic Reduction for Fast, Accurate Simulation

Jivaro is a unique stand-alone solution dedicated to the reduction of parasitic networks. It helps back-end verification teams speed up post-layout SPICE simulation of huge extracted parasitic circuits, while keeping high accuracy.

Parasitic Reduction and Analysis

Jivaro is a unique stand-alone solution dedicated to the reduction of parasitic networks. It helps back-end verification teams speed up post-layout SPICE simulation of huge extracted parasitic circuits, while keeping high accuracy.

Viso analyzes the electrical properties of RC parasitic networks which crucially impact circuit behavior in nanometer processes. These impacts affect circuit gain, delay, maximum clock rate, cross-coupling, level of ESD protection and other features, which can cripple a design. Viso’s parasitics-focused approach enables quick analysis of interconnect in order to pinpoint problems. It provides timing estimation and accurate comparison of different extracted netlists.

Belledonne is used for layout comparison via extracted netlist. It compares two different extracted netlists and is mainly used for layout parasitic extraction (LPE) flow qualification.

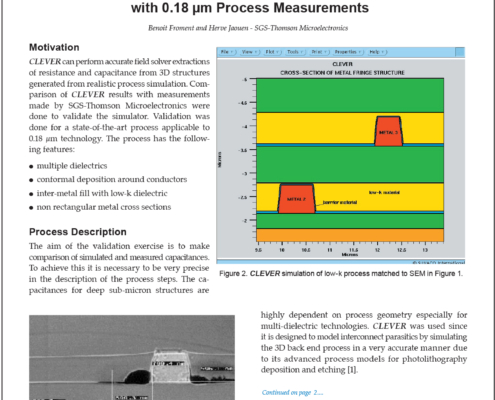

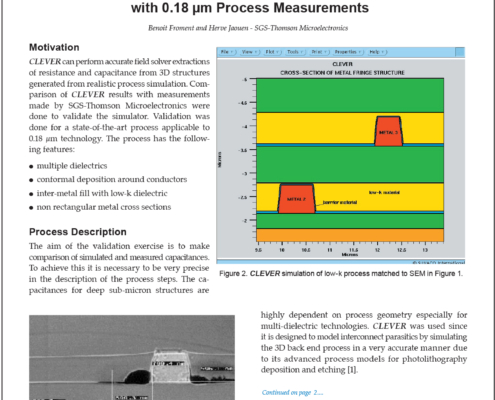

Validation of CLEVER Interconnect Parasitics with 0.18 µm Process Measurements Benoit Froment and Herve Jaouen – SGS-Thomson Microelectronics

CLEVER can perform accurate field solver extractions of resistance and capacitance from 3D structures generated from realistic process simulation. Comparison of CLEVER results with measurements made by SGS-Thomson Microelectronics were done to validate the simulator.