Simulation Standard Technical Journal

A Journal for Process and Device Engineers

Interactive P-cell Generation

1. Abstract

Parameterized cells (P-cells) significantly increase the productivity of layout designers. Silvaco International’s tool Expert has been designed to aid layout designers through its ability to support and manipulate P-cells based on its LISA script language. This simulation standard will demonstrate the capability of Expert and will identify its inherent benefits to the layout engineer.

Interconnect Parasitic Accuracy & Speed Improvements in New CLEVER Release

Introduction

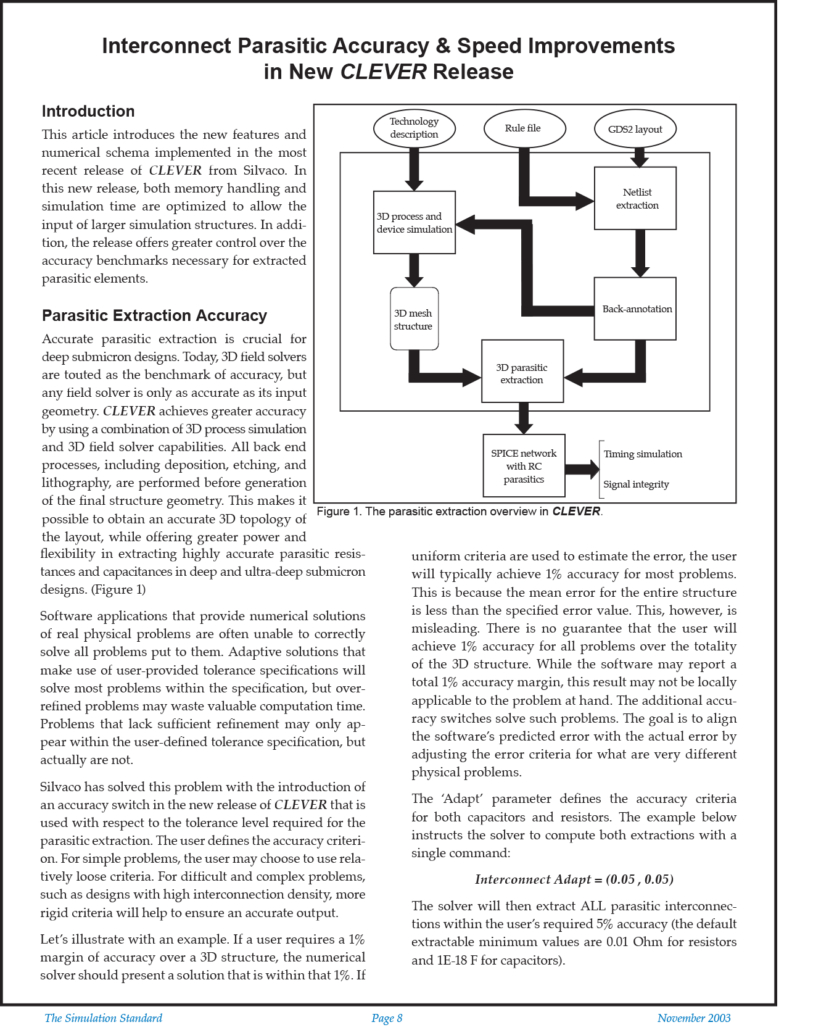

This article introduces the new features and numerical schema implemented in the most recent release of Clever from Silvaco. In this new release, both memory handling and simulation time are optimized to allow the input of larger simulation structures. In addition, the release offers greater control over the accuracy benchmarks necessary for extracted parasitic elements.

Is there a way to automatically specify mesh spacing in ATHENA?

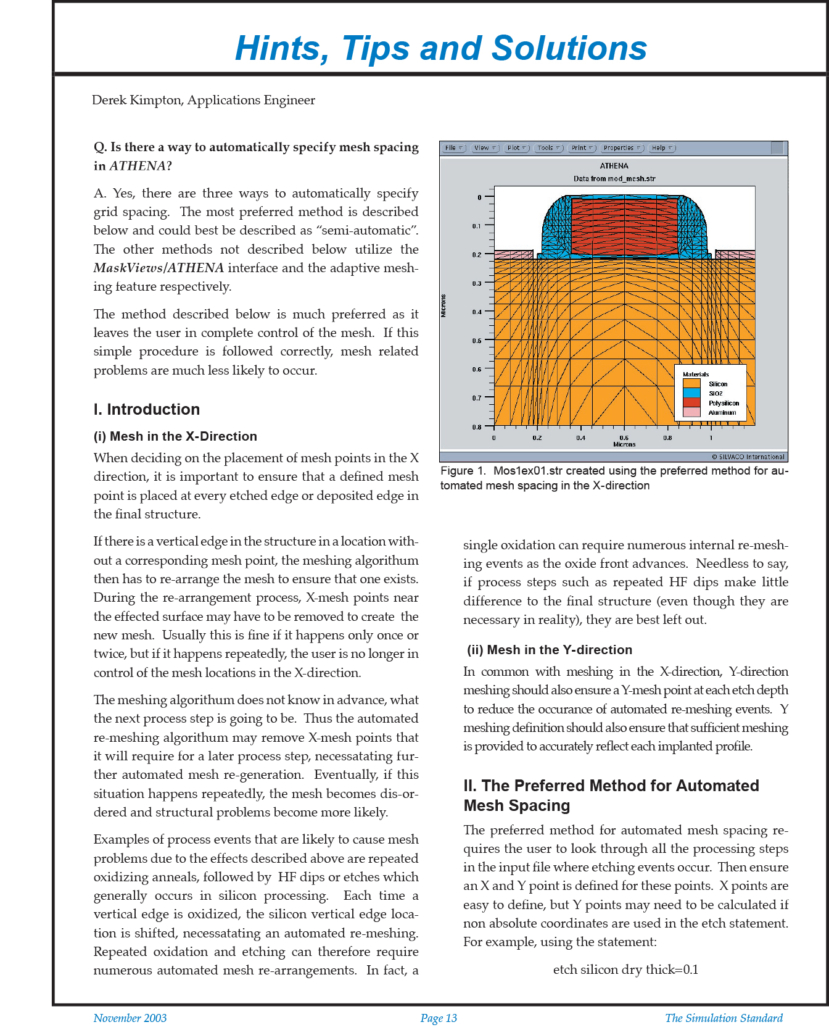

Q. Is there a way to automatically specify mesh spacing in ATHENA?

A. Yes, there are three ways to automatically specify grid spacing. The most preferred method is described below and could best be described as “semi-automatic”. The other methods not described below utilize the MaskViews/ATHENA interface and the adaptive meshing feature respectively.

Topography Simulation of Trench Etch Using Monte Carlo Plasma Etch Model with Polymer Re-deposition

1. Introduction

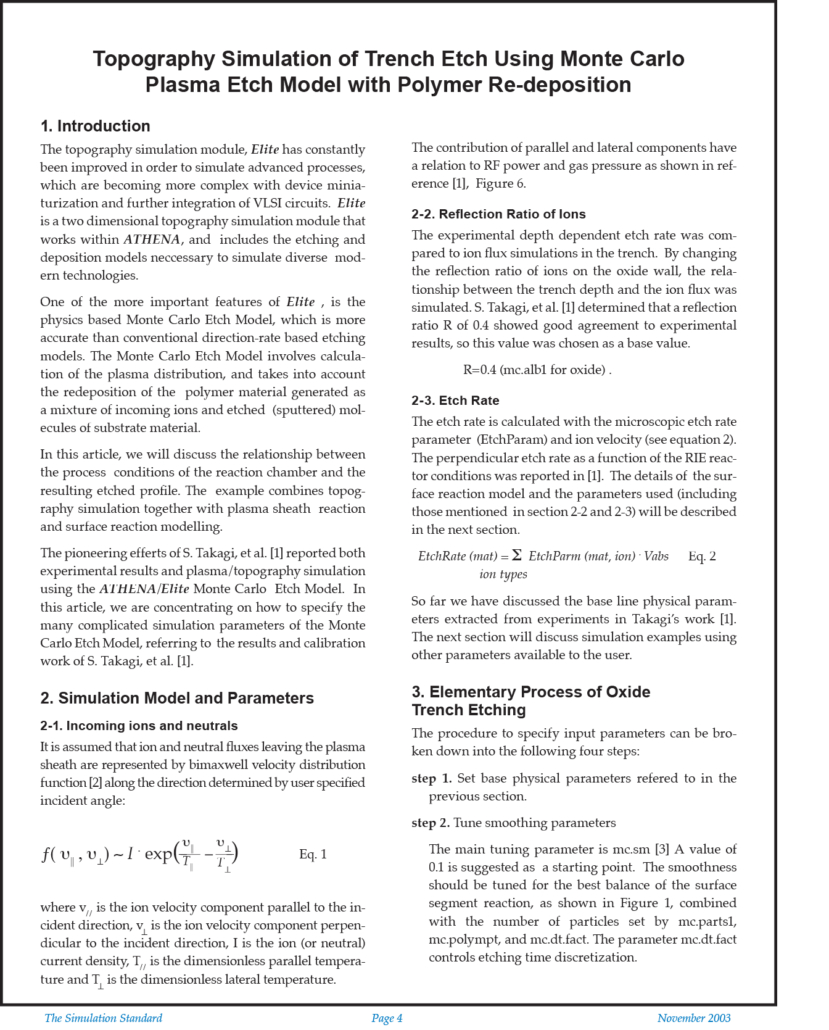

The topography simulation module, Elite has constantly been improved in order to simulate advanced processes, which are becoming more complex with device miniaturization and further integration of VLSI circuits. Elite is a two dimensional topography simulation module that works within ATHENA, and includes the etching and deposition models neccessary to simulate diverse modern technologies.

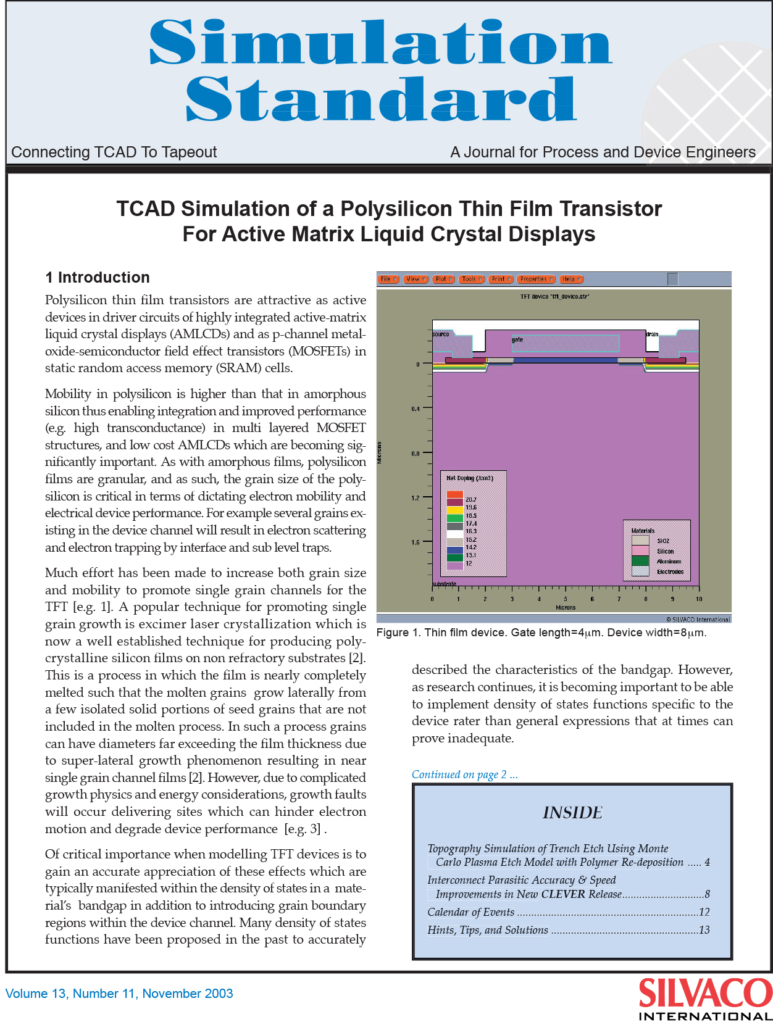

TCAD Simulation of a Polysilicon Thin Film Transistor For Active Matrix Liquid Crystal Displays

Polysilicon thin film transistors are attractive as active devices in driver circuits of highly integrated active-matrix liquid crystal displays (AMLCDs) and as p-channel metal-oxide-semiconductor field effect transistors (MOSFETs) in static random access memory (SRAM) cells.

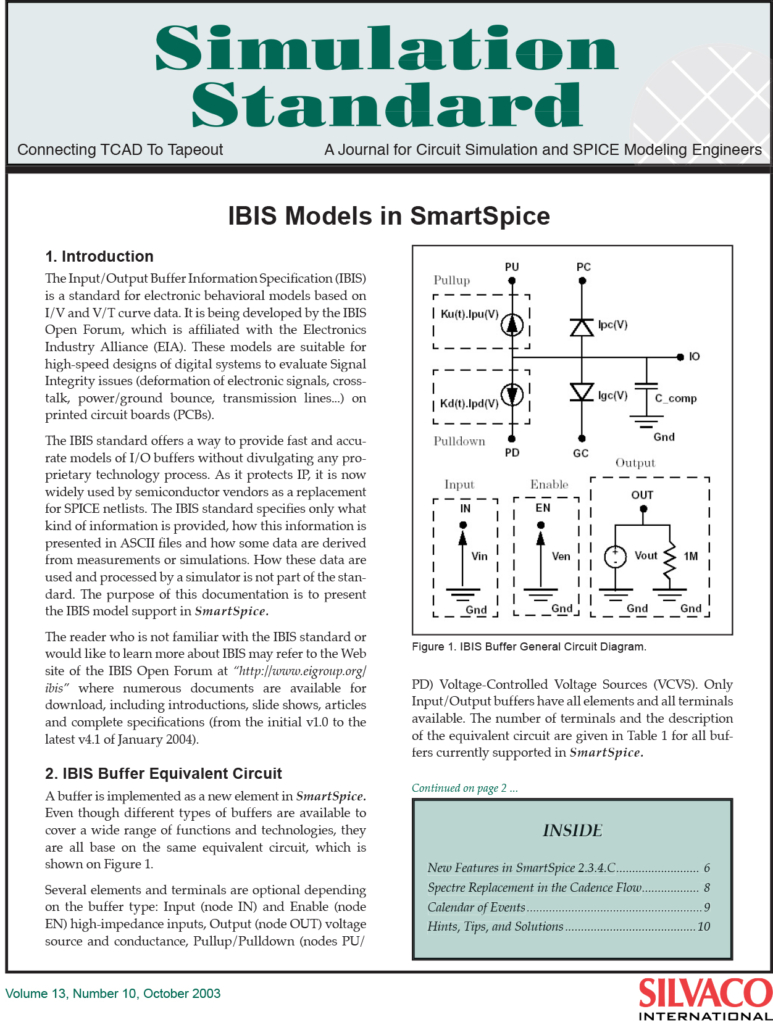

IBIS Models in SmartSpice

The Input/Output Buffer Information Specification (IBIS) is a standard for electronic behavioral models based on I/V and V/T curve data. It is being developed by the IBIS Open Forum, which is affiliated with the Electronics Industry Alliance (EIA). These models are suitable for high-speed designs of digital systems to evaluate Signal Integrity issues (deformation of electronic signals, cross-talk, power/ground bounce, transmission lines...) on printed circuit boards (PCBs).