Library Design Services

Silvaco provides standard cell library design and optimization services either as a fully independent 3rd party IP vendor or as a partner in the development of high performance libraries.

The most common services provided are:

- Standard cell library development

- Standard cell library and design optimization

- Performance add-on cells

- IP migration and generation of library variants

- Library characterization services

Standard Cell Library Development

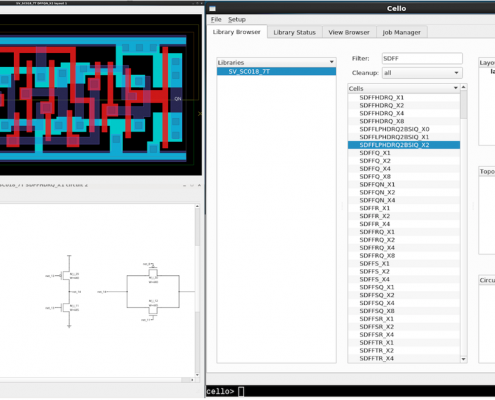

Silvaco has more than 20 years of experience in technology nodes from .35um down to 20nm and now working as partner with major foundries and fabless IC companies on sub-14nm. Our full featured standard cell libraries have demonstrated maximal density and routing performance. The cell schematic used on more complex cells also provides options for high performance or high density design optimizations. As part of the package, all industry standard views (CDL netlist, LEF, GDSII, Liberty, PEX Spice netlist, Verilog, VITAL, EDIF, OpenAccess db and others) are provided from a consistent database. Liberty files can be exported with all timing, power and noise models and for any operating condition (PVT corners). Here are examples of cells found in our standard cell libraries:

- Inverters, Buffers, Clock cells

- NAND, NOR, AND, OR cells

- AOI, OAI, AO, OA cells

- XNOR, XOR (buffered, unbuffered) cells

- MUX, IMUX cells

- D-type Latches (set, reset) and clock gate cells

- D-type Flops and Scan D-Type Flops (set, reset, both, enable)

- Half-Adder, Full-Adder cells

Special cells such as power management, retention and special operation cells can be added to the library. Silvaco also counts with a vast repertory of cells for specific applications.

Few advantages of using Silvaco as a library IP provider and partner:

- High-quality DRC-clean and DFM-friendly layouts in very short time and lower costs – due to the use of our unique Library Creator Platform, the most advanced layout development tool suite;

- Quick library updates (including layout DRC clean-up) when design rules are still changing – technology exploration and PDK development phases;

- Flexibility in the specification of cells (functions, schematics);

- Option to create library variants (refer to IP migration below);

- Vast experience and know-how on standard cell libraries ranging from .35um to 14nm and in the area of application specific performance cells for CPUs and GPUs;

- Broad range of post-sales services such as library re-characterization – and very affordable.

Standard Cell Library and Design Optimization

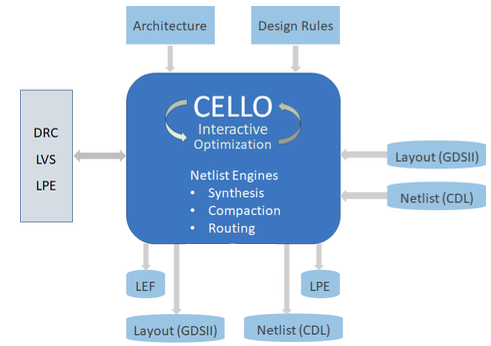

Silvaco has large experience working in processor core optimizations (mainly CPU and GPUs) collaborating with design teams in leading Tier-1 companies. Even foundries have used Silvaco’s design and library optimization flow to achieve higher performance in their benchmarks. In this area of IP optimization, Silvaco provides mainly two independent yet complementary services:

- Standard cell library optimization

- Design optimization

Getting the best performance library involves knowing the target application (design). And getting the best performance design relies on the quality of the standard cell library, macros and memories used. Even though each optimization can be done independently – and they do provide good results -, optimizing both libraries and design concurrently provides ultimate gains similar to or better than those seen in custom design flows. The image below shows how the concurrent optimization works (in cycles):

For further information on high performance (high impact) cells, please refer to Performance Add-On Cells below.

Performance Add-On Cells

As part of the library optimization services or as an independent IP, Silvaco can provide these non standard cells for specific targets (performance, area, power).

Here are some few examples of high performance cells offered by Silvaco:

- Timing Performance Cells: high-skew, asymmetric, tapered, fast inputs, combined “simple”, XOR/XNOR variants, MUX/IMUX variants, low-gain negative-unate cells, extra drive strengths;

- ECO Timing Cells: footprint compatible variants;

- Power Reduction Cells: High-gain positive-unate cells, gate-length (gate biasing) variants, specialized power latches and clock gates, multi-bit cells, VT variants;

- Area Reduction Cells: Combined functions, highly-dense low drive-strength cells;

- Flip-Flop Variants and custom cells

IP Migration: Generation of Library Variants

Silvaco offers IP migration and creation of library variants. It can be part of a library development service or it can be performed over IP from 3rd party vendors. Here are few example of IP migration services where Silvaco has large experience with:

- Vt (threshold) library variants;

- Gate-length (gate biasing) library variants;

- Template (cell architecture) library variants;

- Metal-stack footprint compatible library variants (used for ECO);

- Cell height and transistor sizing library variants, etc.

IP migration services are usually offered at very affordable prices and they have very short development cycles.

For further information or to inquiry on library design services, please contact sales@silvaco.com.