Understanding the Modeling Framework for CMOS Technology within Victory Process

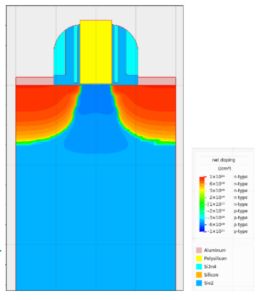

The processing of the latest generations of CMOS devices cannot be simulated with precision using simple diffusion models. This is due to the continuous reduction in size of the technology nodes, which means shallower junctions and smaller doped zones, which in turn means that transient diffusion mechanisms will play a bigger and bigger role in processing those zones and thus in the final device characteristics. Notably, out-of-equilibrium defects and their effects on diffusion mechanisms must be modeled, along with various dopant co-interactions.

In this webinar users will learn how these mechanisms are simulated within Victory Process and how to set up your process simulation with these models. We will then utilize these models with a planar CMOS example and see how the results are much improved.

What You Will Learn

- The CMOS diffusion model physics

- The CMOS diffusion model features

- How to use the CMOS diffusion model in your decks

- Some real-life application examples using the CMOS model

Presenter

Dr Thomas Grenouilloux

Dr Thomas Grenouilloux

WHO SHOULD ATTEND:

Process engineers, simulation engineers, fabrication engineers, product managers, and engineering management.