Circuit Performance Analysis of Multiple ATHENA Transistors Using MixedMode

Introduction

In a previous issue of Simulation Standard for Process and Device Engineers[1] the simulation of a three stage CMOS ring oscillator using ATLAS/MixedMode was introduced. The MOSFETs used in the MixedMode simulation were created using analytical doping profiles specified within ATLAS. This article is intended to investigate some of the effects of process variation on ring oscillator performance. Thus, the individual devices in the ring oscillator circuit are created usingthe two-dimensional process simulation program, ATHENA.

Simulation Methodology

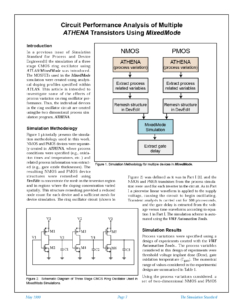

Figure 1 pictorially presents the simulation methodology used in this work. NMOS and PMOS devices were separately created in ATHENA, where process conditions were specified (e.g., oxidation times and temperatures, etc. ) and related process information was extracted (e.g., gate oxide thicknesses). The resulting NMOS and PMOS device structures were remeshed using DevEdit to concentrate the mesh in the inversion region and in regions where the doping concentration varied spatially. This structure remeshing provided a reduced node count for each device and a sufficient mesh for device simulation. The ring oscillator circuit (shown in Figure 2) was defined as it was in Part I [1], and the NMOS and PMOS transistors from the process simulation were used for each inverter in the circuit. As in Part I a piecewise linear waveform is applied to the supply voltage, causing the circuit to begin oscillating. Transient analysis is carried out for 500 picoseconds, and the gate delay is extracted from the voltage versus time waveforms according to equation 1 in Part I. The simulation scheme is automated using the VWF Automation Tools.