SmartDRC/LVS Physical Verification

SmartDRC/LVS는 설계 규칙 검사 (DRC), 레이아웃 연결성 추출 및 레이아웃과 스키매틱의 비교 (LVS) 등, 아날로그, 믹스드 시그널 IC에 대한 물리적 검증을 수행합니다. 신속한 대화식 검증과 직관적인 디버깅과 함께 멀티 CPU, 복잡한 형상의 정확한 처리 및 우수한 생산성을 활용하여 탁월한 성능을 제공합니다. SmartDRC/LVS는 실리콘 입증되었으며, TowerSemi, X-FAB, UMC에서 공정에 대한 파운드리 인증을 받았습니다.

소개

설계는 복잡해지고 공정의 기하학적 구조는 축소되면서, 생산적인 물리적 검증 환경에 대한 필요성이 커지고 있습니다. 이는 규칙 및 기술 파일의 신속한 설정, 설계 시작부터 검증에 이르는 효율적인 데이터 플로우, 대규모 계층적 설계에 대한 검증 툴의 신속한 처리 능력을 포함합니다. 툴에서의 편리한 디자인 탐색, 직관적인 이해, 확인된 오류의 신속한 디버깅 및 해결이 요구됩니다. 복잡한 형태 및 임의의 각도를 갖는 객체를 올바르게 처리하기 위해, 기하학적 구조에 의존적인 SPICE 파라미터의 정확한 계산은 매우 중요합니다.

SmartDRC/LVS는 이러한 요구사항에 적합한 특별한 기능을 갖추고 있습니다. 멀티 스레드 프로세싱, 최적화된 레이어 운영, 효율적인 메모리 관리 및 최신 알고리즘을 통해 탁월한 성능을 제공합니다.

SmartDRC/LVS는 Expert 레이아웃 에디터 및 Gateway 스키매틱 에디터와 긴밀하게 통합되어 있으므로, 설계상의 문제점 및 설계 규칙 위반을 시각적으로 파악하여 신속하게 해결할 수 있습니다. SmartLVS는 레이아웃으로부터 넷리스트를 추출하여, 스키매틱과 레이아웃을 교차 검증할 수 있습니다.

특징

DRC/LVS

- DRC (design rule checking)

- LVS (layout versus schematic)

- NVN (netlist versus netlist)

- 혁신적인 아키텍처를 통해 거의 비례적인 확장 및 실행시간 예측

- 안테나 규칙, 밀도 규칙, 패드, 래치 및 기타 특수 규칙 지원

- 특정 소자에 대해 모든 각도 지원

- 대화형 위반 처리 기능을 갖춘 RDE (실행 및 디버깅 GUI 환경)

- 계층 오류 탐색

- 면제 시스템 (waiver system)

- Expert 레이아웃 편집기에서 기본 오류 탐색

- LVS 교차 프로빙

- 포괄적인 보고서 및 요약

- 프로그래밍 할 수 있는 명확하고 강력한 규칙 언어

- Expert 및 기타 물리적 레이아웃 편집기와 통합

- OpenAccess 기본 지원

장점

- 동급 최고의 성능

- 대규모 CPU 팜 및 멀티 코어 시스템에서 성능 확장 가능

- 그래픽 및 텍스트 DRC 오류 보고서에 의해 간편한 탐색 및 시각화

- 새로운 사용자 및 전문가를 위한 직관적 솔루션

- 실리콘 입증 및 TowerSemi, X-FAB, UMC에서 공정에 대한 파운드리 인증

적용

- 아날로그, 믹스드 시그널, 디지털, MEMS, 메모리, 포토닉스, 전력 관리, 평판, 방사선 내성, RF 설계

성능

SmartDRC는 싱글/멀티 코어에서 플랫 또는 계층형 실행에 대해 예측 가능한 확장 기능을 제공합니다. 180nm로 설정된 기존 복합 파운드리 인증 규칙의 경우, SmartDRC는 자체 기술을 활용하여 대략 시간당 1600만 개의 트랜지스터를 플랫으로 처리할 수 있습니다.

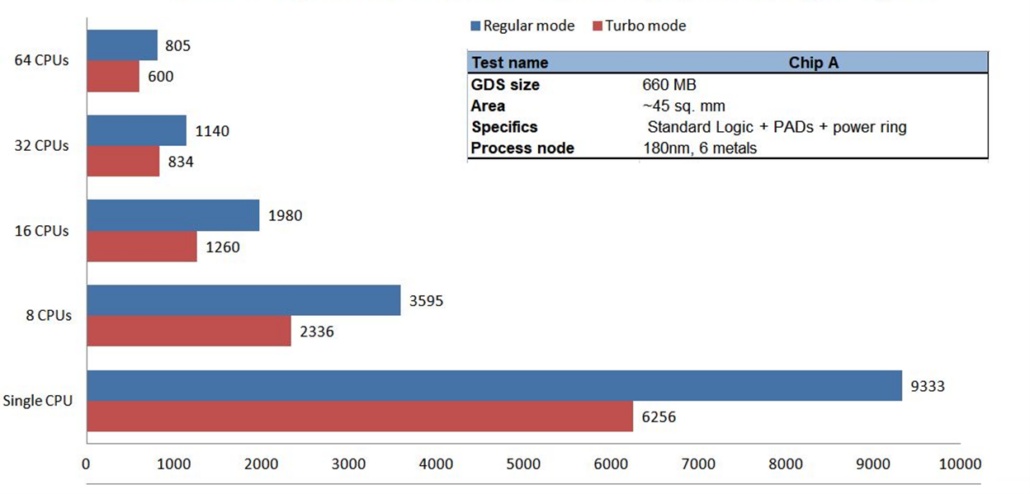

아래 그림에서, SmartDRC는 파운드리에서 인증한 규칙 데크를 사용하여 180nm 설계의 DRC 분석을 수행하였습니다. 여기에는 6개의 메탈 레이어를 사용하는 표준 로직, PAD, 파워 링 등이 포함되었습니다. 플랫 GDS 레이아웃 데이터베이스 크기는 660M로서, CPU 수에 따른 실행 시간(초)을 표시하였습니다. 터보 모드는 대부분의 설계에서 정확도를 최소화하여, 속도를 높이는 경험적 접근 알고리즘입니다. 싱글 CPU에 비해 64개의 CPU를 사용할 경우, 성능이 10배 이상 향상되었습니다. CPU를 32개에서 64개로 늘릴 경우, 역시 25% 이상 성능이 향상되며, 이로써 SmartDRC/LVS 분석 기술의 우수성을 확인할 수 있습니다. SmartDRC/LVS은 다른 물리적 검증 툴과 동등하거나 더 빠른 속도를 보여줍니다.

Viso를 활용한 기생 문제의 조사, 분석 및 해결

Si, GaN, SiC 기술에 대한 전력 소자 SPICE 모델링

SmartSpice를 활용하여 최신 TFT 기반 플랫 패널 설계

Utmost IV를 활용한 소자 모델링의 최신 기술

실바코 플로우를 활용한 FPD 및 검출기의 픽셀 어레이 설계 및 시뮬레이션