Digital Twins for Semiconductor Manufacturing

Abstract:

TCAD models are used to simulate the fabrication and operation of semiconductor devices. TCAD has become essential in the deployment of new semiconductor technology. With increasing accuracy, TCAD models can now be used as “digital twins” to simulate and optimize semiconductor manufacturing processes.

This opens up many new applications, such as virtual development of new semiconductor technology, reducing the need for physical experimentation, and ultimately shortening development time and time to yield. Digital twins can also be used during production in the fab to further optimize processes, monitor variations, and detect malfunctions. This presentation will delve into these concepts and provide examples of TCAD that can be used as digital twins.

Speaker:

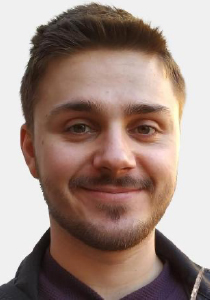

Raúl Camposano, Ph.D, Chief Technology Officer

Silvaco, Inc.

Raúl Camposano, Ph.D., has served as Silvaco’s Chief Technology Officer since February 2022. Dr. Camposano has served as a partner at Silicon Catalyst LLC, an incubator for semiconductor solutions, since April 2015 and as a lecturer on EDA and Machine Learning Hardware at Stanford since April 2018. From July 2020 to January 2022, Dr. Camposano served as an advisor to Applied Materials, Inc., a semiconductor equipment company. From August 2015 to July 2020, Dr. Camposano served as Chief Executive Officer of Sage Design Automation, Ltd., a software tools company acquired by Applied Materials in 2020. From November 2010 to May 2014, Dr. Camposano served as Chief Executive Officer of Nimbic, Inc., an EDA cloud company, acquired by Mentor Graphics Corporation in 2014. From January 1994 to January 2007, Dr. Camposano served in various roles at Synopsys, an EDA solutions company, including as its Chief Technology Officer, Senior Vice President, and General Manager. Prior to that, Dr. Camposano served on the board of directors of the German National Research Center for Computer Science, as a professor of computer science at the University of Paderborn, and as a Research Staff Member at the IBM T.J. Watson Research Center. Dr. Camposano received a B.S. and M.S. in electrical engineering from Universidad de Chile and a Ph.D. in computer science from Karlsruhe Institute of Technology. Dr. Camposano was elected as a Fellow of the IEEE in 1999 and to serve on the board of directors of ESDA, the EDA Consortium, in 2012.