Low-power Physical IP for the Next Generation of Energy-efficient Solutions

Silvaco enables the next generation of energy-efficient designs through a comprehensive portfolio of Low Power Foundation IP for designers of ASICs, SoCs, and semiconductor solutions across multiple foundries:

- Memory Compilers for SRAMs, Register Files, and ROMs

- Standard Cell Libraries, Power Management Kits, and ECO Kits

Standard Cell Libraries

Silvaco’s Low Power Standard Cell libraries deliver highly optimized cells targeting low power and high-density applications. Our Low Power Standard Cell libraries include thousands of cells with each one being optimized for power, area, speed, routing, and yield.

These libraries may be extended with Power Management Kits, taking power reduction to the next level, and ECO Kits to enable late-stage design modifications.

Standard Cell Libraries Features and Applications

| Feature | Application |

| Multiple Vt and Well options | Customize designs for optimal power, performance, and area |

| Fine grained drive strengths and low leakage cells | Reduce use of oversized or overpowered cells |

| Power Management Kit | Enables power gating and multi-voltage low power design methodologies |

| Multi-bit and Multi-height standard cells | Optimize design implementations with sequential cells and MUX structures |

| ECO kit with fixed pattern for FEOL layers | Provides for flexibility of late layout modifications with minimal number of mask changes |

| Level-shifters | Enables multiple voltage domains |

| Custom Corners | Custom characterization corners such as low voltage operation |

Memory Compilers

Silvaco’s best in class Single Port SRAM is designed to achieve minimum power and area while meeting aggressive timing requirements. This silicon proven memory includes a comprehensive set of features delivering industry leading low Dynamic Power consumption.

Memory Features and Applications

| Feature | Application |

| Multiple Vt periphery | Architecture customized to provide ideal target power, performance, and area |

| Embedded power switches | Saves SoC design time, area, and power while lowering risk |

| Segmented power control | Provides flexibility for segmented power shut off and overall power management |

| Read and Write Assist | Low voltage and low power operation |

| Multiple power management modes | Offers multiple power saving customization options |

| Single power supply option | Easy integration |

| Custom Corners | Custom characterization corners such as low voltage operation |

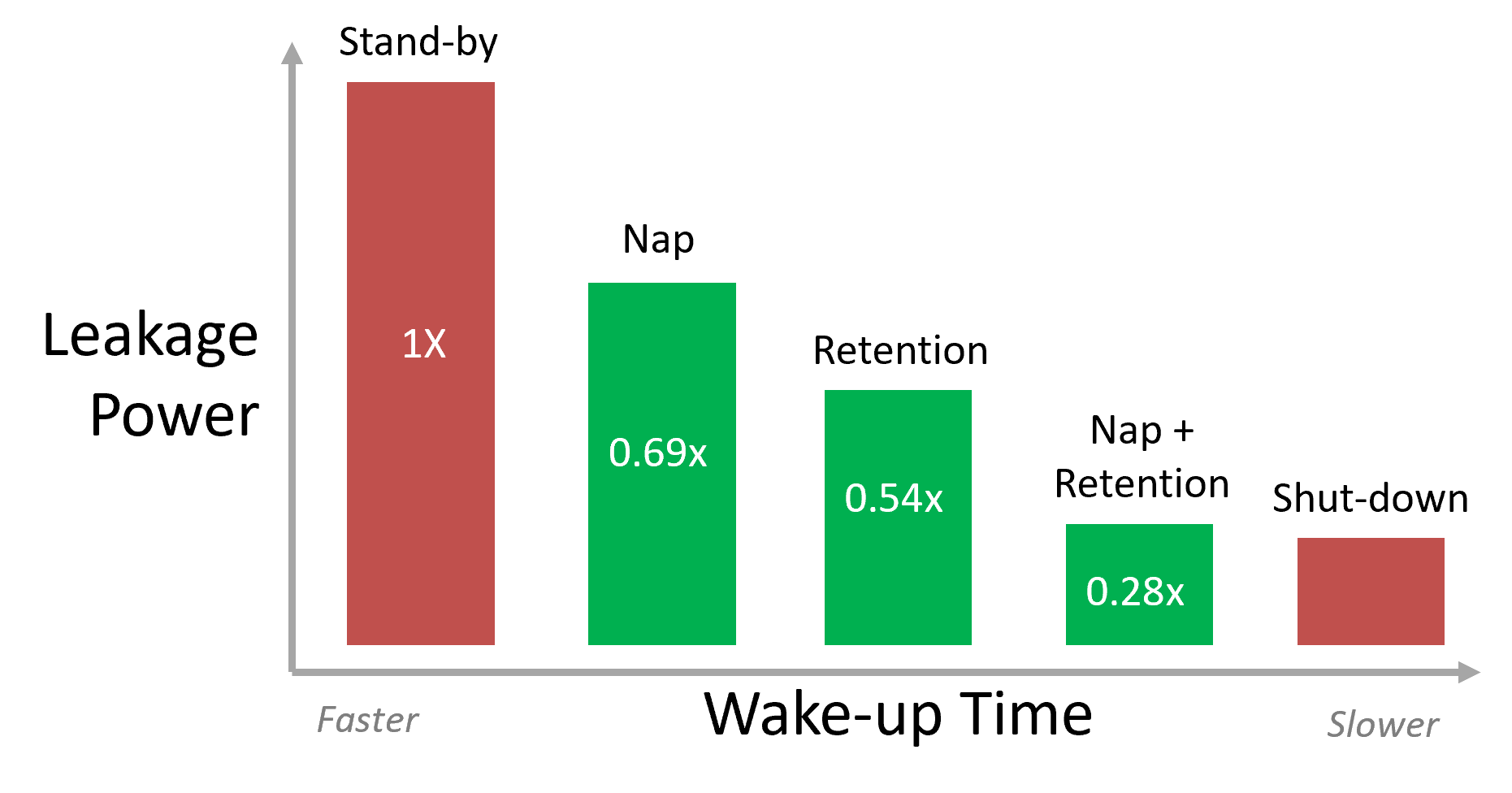

Memory Power Management

Multiple power modes for static power savings are available enabling the best trade-off between power savings and wake up time. Retention, retention-nap, and shut-down modes provide a progressive reduction of leakage power compared to just a stand-by mode. Our architecture enables low power consumption through multiple compiler options.