Build Better Advanced Logic Faster: Process to Device Simulation, Calibration, and FTCO™ Workflows

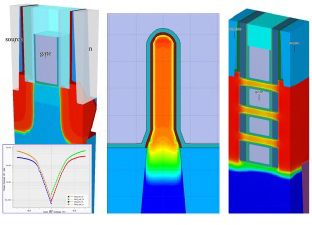

As Moore’s Law continues pushing semiconductor technology forward, transistor architectures have entered the three-dimensional era. FinFETs remain the dominant workhorse for advanced logic nodes, and as scaling pushes further, Gate All Around (GAA) nanosheet transistors have emerged as an important extension for continued electrostatic control and performance. This webinar presents a practical workflow for modeling and simulating advanced node FinFET devices, with a supporting GAA nanosheet demonstration to illustrate how the same methodology extends as architectures evolve.

As Moore’s Law continues pushing semiconductor technology forward, transistor architectures have entered the three-dimensional era. FinFETs remain the dominant workhorse for advanced logic nodes, and as scaling pushes further, Gate All Around (GAA) nanosheet transistors have emerged as an important extension for continued electrostatic control and performance. This webinar presents a practical workflow for modeling and simulating advanced node FinFET devices, with a supporting GAA nanosheet demonstration to illustrate how the same methodology extends as architectures evolve.

We focus on the key physical effects and modeling considerations required for accurate device representation—such as quantum confinement, band structure corrections, strain engineering, and mobility behavior—within a calibrated process to device simulation flow using Silvaco Victory TCAD. Powered by Victory Device, we show how simulations can be calibrated and validated against reference data. Finally, we demonstrate how Victory Analytics and Fab Technology Co-Optimization (FTCO™) enable multidimensional process/design exploration, accelerating development cycles and helping optimize design windows for next generation high performance, low power logic.

What You Will Learn

- FinFET and nanosheet/GAA: what changes at advanced nodes

- A practical Victory TCAD workflow for advanced logic simulation

- How calibration/validation fits into the TCAD loop

- How FTCO™ enables multi‑parameter exploration and optimization

- Using DoE + analytics to find sensitivities and trade‑offs faster

- How FTCO can build an interactive digital twin

Presenter

Jay Zhou

Jay Zhou

Senior TCAD FAE, Silvaco

Jay Zhou is a TCAD Field Application Engineer with 9 years of professional experience in the semiconductor industry. Prior to joining Silvaco, he worked at several leading semiconductor foundries, focusing on process development and device optimization. Currently, he is responsible for providing technical support and application solutions for TCAD customers.

WHO SHOULD ATTEND:

Process engineers, simulation engineers, fabrication engineers, product managers, and engineering management.

When: March 26, 2026

Where: Online

Time: 10:00 Santa Clara

Time: 11:00 Paris

Time: 10:00 Beijing

Language: English