Modification of BEM for Precise Capacitance Extraction

Introduction

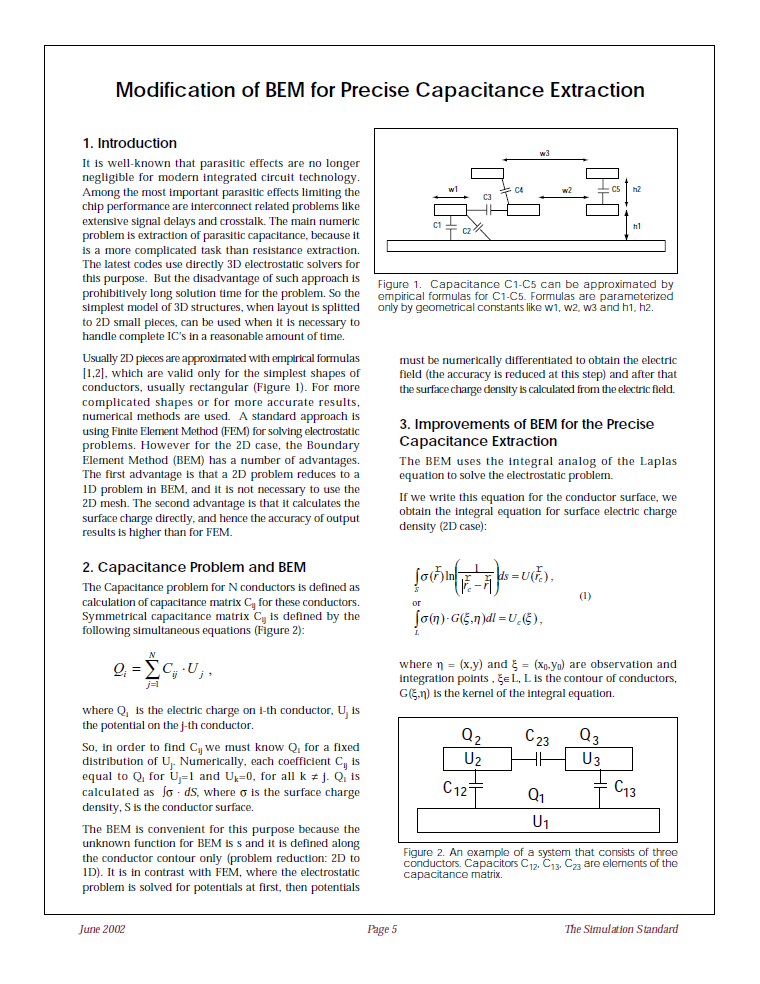

It is well-known that parasitic effects are no longer negligible for modern integrated circuit technology. Among the most important parasitic effects limiting the chip performance are interconnect related problems like extensive signal delays and crosstalk. The main numeric problem is extraction of parasitic capacitance, because it is a more complicated task than resistance extraction. The latest codes use directly 3D electrostatic solvers for this purpose. But the disadvantage of such approach is prohibitively long solution time for the problem. So the simplest model of 3D structures, when layout is splitted to 2D small pieces, can be used when it is necessary to handle complete IC’s in a reasonable amount of time.