LPE Optimization with Clever/Hipex/Exact Linkage Methodology

1. Introduction

On the cutting edge of LSI design, the accuracy of Layout Parasitic Extraction (LPE) tools is a critical issue to miniaturized LSI design of rules measuring 0.13 um or lower. The quantitative consideration of coupling capacitance based on three-dimensional calculation is indispensable. Conventional advanced LSI design tools and methodology are limited in their ability to optimize the LPE library. As a result, the discussion of LPE tool accuracy and extracted parasitic results lack significant quantitative generality.

This article proposes a new methodology for verifying accuracy of LPE tools and optimizing the LPE library for today’s 0.13 um designs and the more scaled-down next generation LSI design of nodes at 100 nm or less.

2. Simulation Flow and Methodology

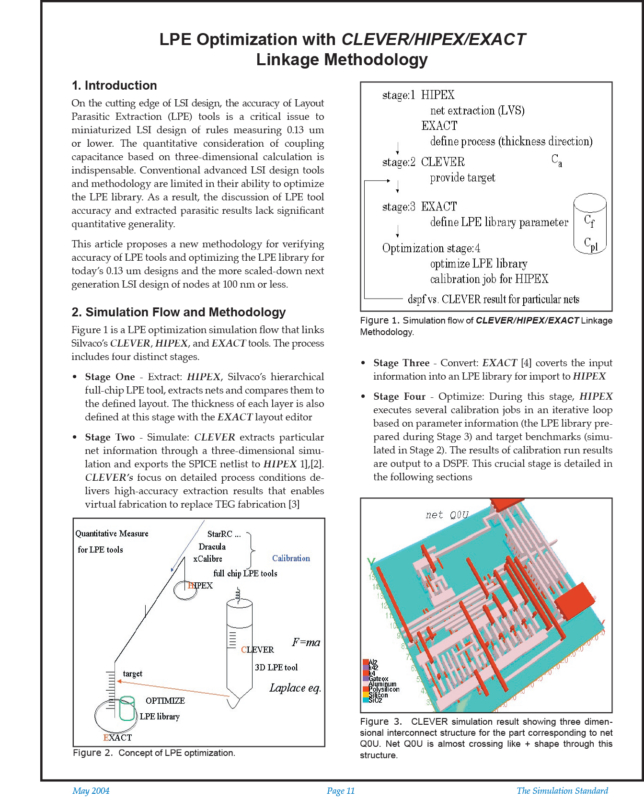

Figure 1 is a LPE optimization simulation flow that links Silvaco’s CLEVER, HIPEX, and EXACT tools. The process includes four distinct stages.

- Stage One – Extract: HIPEX, Silvaco’s hierarchical full-chip LPE tool, extracts nets and compares them to the defined layout. The thickness of each layer is also defined at this stage with the EXACT layout editor

- Stage Two – Simulate: CLEVER extracts particular net information through a three-dimensional simulation and exports the SPICE netlist to HIPEX 1],[2]. CLEVER’s focus on detailed process conditions delivers high-accuracy extraction results that enables virtual fabrication to replace TEG fabrication [3]

- Stage Three – Convert: EXACT [4] coverts the input information into an LPE library for import to HIPEX

- Stage Four – Optimize: During this stage, HIPEX executes several calibration jobs in an iterative loop based on parameter information (the LPE library prepared during Stage 3) and target benchmarks (simulated in Stage 2). The results of calibration run results are output to a DSPF. This crucial stage is detailed in the following sections.